《计算机存储与外设》----2.3 DRAM

本 节 书 摘 来 自 华 章 出 版 社 《计算机存储与外设》 一 书 中 的 第2章,第2.3节, 作 者 Computer Organization and Architecture: Themes and Variations[英]艾伦·克莱门茨(Alan Clements) 著, 沈 立 肖晓强 王苏峰 译, 更 多 章 节 内 容 可 以 访 问 云 栖 社 区 “华 章 计 算 机” 公 众 号 查 看。

2.3 DRAM

大多数PC机和工作站使用DRAM实现主存储器,它已经在高性能计算机的发展中起到关键作用,表现为其工作参数不断发展变化且出现新的变种。我认为DRAM在不久的将来仍然是主流。本节首先描述DRAM的工作原理,接着介绍它的时序,然后介绍DRAM系列,最后描述它们如何在微机中使用。

动态随机访问存储器(dynamic random access memory,DRAM)的工作原理很简单。数据以存储在晶体管中的静电电荷的形式保存。当材料不带电时,材料中的电子数等于质子数;即电子的负电荷抵消了带正电的质子,因此不带电。当材料充电后,电子要么被添加要么被移除。如果有太少的电子,则电性为正;如果有太多的电子,则电性为负。在微小的电容上有极性还是没有极性这个信息可以用来存储一个比特。人们所要做的就是为电容充电、放电以及检测其是否带电。

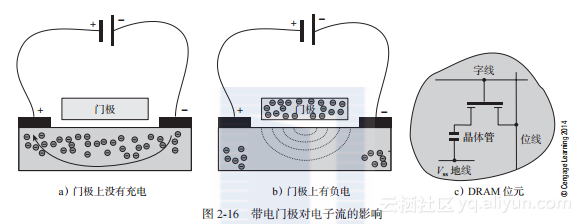

图2-16显示了场效应晶体管的基本原理,它是大多数逻辑设备的基本元件。掺杂(doped)硅芯片上的一个微小区域有两个端子分别连到电池正、负极。掺杂这个词意味着在硅芯片中掺入杂质使电子流可以自由通过硅(纯硅中电子受到束缚而不能穿过硅材料)。

图2-16a中,两个端子之间有电流流动。

图2-16中,在硅区域上方的导电体被标记为门极。假设其与图2-16a中两个端子之间硅通道中的电子流是绝缘的。

在图2-16b中,对门极充上负电荷。电荷产生静电场,穿过硅通道。因为门极上电荷是负的,故通道中的电子被排斥(同性电荷相斥,异性电荷相吸)。图2-16b中,所充的负电荷十分强大,通道处于夹断(pinched)状态,没有电流通过该通道。

通过对门极充负电荷还是不充负电荷,可以控制流过通道的电流。所有门极都是通过这种方式来切断电子流的。它还可用于DRAM以及包括EPROM、EEPROM和Flash EPROM在内的大部分时间为读的存储器。

如果将负电压加到门极上以便对其充电,从而使晶体管关闭。当撤去电压时,晶体管仍然不能导通直到电荷消除。如果门极与通道绝缘,消除电荷的时间可能需要几毫秒。

在电容中保存电荷是形成单晶体管DRAM位元的基础。在门极上充电使晶体管处于两种状态之一。图2-16c展示了一个单晶体管DRAM位元的结构。

保存的电荷最终会泄漏,存储在位元中的任何数据都会丢失,使所有位元处于相同的状态。为了使保存的电荷具有记忆效应,实际的存储器必须每隔几毫秒就读取晶体管的状态然后将其写回晶体管。这种操作称为刷新(refreshing)。

第一代DRAM存储器的刷新是一场噩梦,需要复杂的电路和定时器,因此开销很大。只要可能,设计师就会使用SRAM来避免使用DRAM进行系统设计带来问题。今天情况已经好转,因为将刷新逻辑设计在DRAM芯片中使DRAM的刷新要求大大简化。

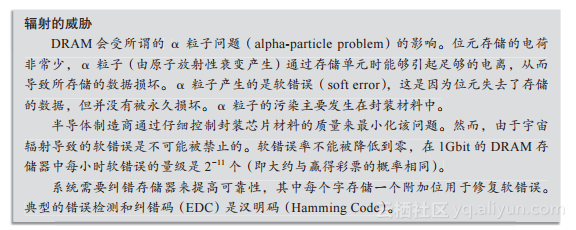

图2-17给出了DRAM的结构。乍一看,它似乎与静态存储器芯片非常相似,除了两个低电平有效的控制输入。除了片选外,还有行地址选通(row address strobe)和列地址选通(column address strobe)。DRAM接口不同于静态RAM接口的一个重要方面是:动态存储器使用多路复用地址总线(multiplexed address bus)来减少地址引脚的数量。即使用两步来获得地址。例如,一个28位地址的256Mb芯片,有14位地址输入,28位的地址必须是连续两个14位值的合并。在存储器访问的开始,该芯片提供14位的行地址以给出所需位元所在行,然后通过相同的引脚给出第二个14位的列地址。通过信号来获得行地址,使用与信号来获得列地址。然后才能访问给定行列位置的位元。

将地址总线从28位减少到14位需要两个阶段来锁存地址。由行地址选通锁存14位行地址,列地址选通锁存14位列地址。地址复用以及和的选通控制由片外逻辑提供。

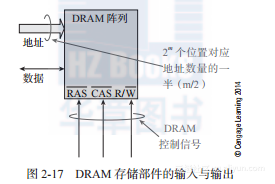

图2-18给出了DRAM存储器的内部结构。最需要注意的一点是其中包含不止一个存储阵列。商用芯片通常由4个存储阵列或存储体组成。

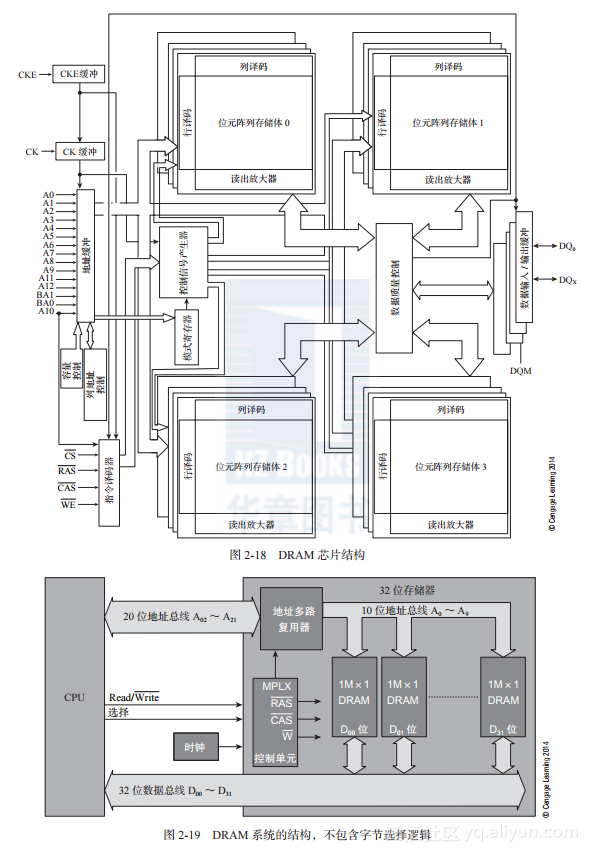

图2-19给出了某4MB的DRAM的结构,其地址为A00~A21,由32个1Mb的DRAM芯片构成。来自计算机的地址线A02~A21可以选择220个32位的字。DRAM存储子系统使用多路复用器从地址总线上选择行或列地址。控制单元根据CPU的控制信号产生DRAM的、和信号。

介绍了DRAM的基本概念后,下一步将介绍它的时序,因为时序是理解所有DRAM后期变化的关键。

2.3.1 DRAM时序

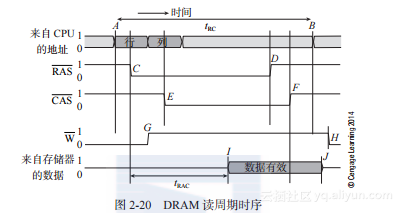

本节首先介绍20世纪80年代经典的DRAM时序,所有现代DRAM时序均可由其变化得到。虽然DRAM存储位元是由一个晶体管构成这一属性基本没有变化,了解DRAM时序的基本属性是为了理解,DRAM是如何一代一代变得更快的。图2-20给出一个简化的DRAM芯片的读周期时序图。假定1Mb的芯片组织具有220个地址,每个地址1位。

来自CPU的20位地址A00~A19被送到一个多路复用器,要么选择A00~A09(行地址)要么选择A10~A19(列地址)。CPU地址多路复用器(MPLX)的10个输出连接到DRAM地址输入A0~A9。

图2-20中的读周期从A持续到B,最短持续时间为tRC,即读周期时间(read cycle time)。静态存储器的存储周期与访问时间相同;动态存储器的存储周期比其访问时间要长。因为在当前访问结束后,在两次访问之间,DRAM需要执行被称为预充电(pre-charging)的内部操作,因此不能开始新的访问。

读周期的第一步是向芯片输入来自CPU的低10位地址A0~A9。然后,在点C,行地址选通(row address strobe,)变为低电平有效,将行地址保存到芯片内部的锁存器。一旦获得行地址,从处理器来的低位地址就是多余的,周期剩余部分不再需要它。相比之下,SRAM的地址必须在整个读或写周期中保持稳定。

来自CPU的高10位地址接着被交给存储器的地址输入,然后列地址选通(column address strobe,)在E点变为低电平有效,锁存列地址。此时,所有20位地址都已交给存储器,系统可以改变地址总线的内容,因为DRAM已获得了地址。

一旦变为低电平,根据地址选中的存储单元将数据放到其数据输出端口,允许CPU读取。读周期结束时,变为高电平无效,数据总线被关闭,变为悬浮状态。和可以同时、也可以次序任意变为高电平。无论谁先变为高电平都无所谓,只要其他的时序满足要求。要使对DRAM的解释更容易理解,需要将它分为几个部分,并从地址引脚的作用开始讨论。

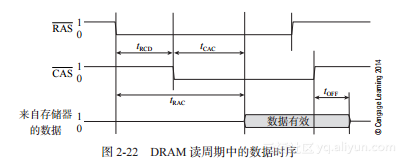

详细的DRAM地址时序如图2-21所示。行地址必须在信号下降沿到来之前稳定至少tASR时间(即行地址建立时间)。由于tASR的最小值可能是0ns,此时行地址的建立时间为零,不需要在信号下降沿到来之前有效。最坏情况下,它必须在信号下降沿到来之前有效。当已经变为低电平,行地址必须稳定tRAH时间不改变,即行地址保持时间。保持时间限制了在此之后列地址才可以被多路复用到芯片上的地址引脚上。

一旦行地址保持时间已经得到满足,列地址可以复用到存储器的地址引脚,就可以变为低电平。列地址的建立时间tASC通常最小为0ns;即可以在列地址有效的同时变为低电平。变为低电平有效后,列地址必须稳定tCAH时间才可以改变,这就是列地址保持时间。一旦tCAH已经得到满足,地址总线在当前访问中就没有作用了。

行地址必须在行地址选通信号下降沿到来之前保持有效tASR时间,且在下降沿之后保持有效tRAH时间。同样,列地址必须在列地址选通信号下降沿到来之前保持有效tASC时间,且在下降沿之后保持有效tCAH时间。和下降沿之间的最小时间为tRCD,该时间由行地址保持时间、多路复用器切换时间和列地址建立时间组成。

图2-21中的一个重要参数是tRCD,即由其他参数决定的行列选通时间。tRCD的最小值由行地址保持时间、多路复用器切换时间和列地址建立时间决定。tRCD的最大值为伪最大值(pseudomaximum),此时超出了存储器的访问时间。tRCD(max)、tRAC和tCAC之间的关系为:tRCD(max)=tRAC-tCAC。

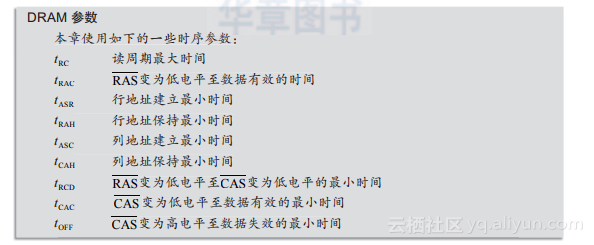

通过和就可以锁存地址,芯片数据引脚上就会出现数据,如图2-22所示。为清晰起见,图2-22中只画出了、以及数据信号。假设信号在读周期内为高电平,地址建立时间、保持时间和所有相关的参数都得到了满足。

下降沿之后,数据引脚上的数据在tRAC时间后开始有效,这就是行地址选通后的访问时间。可见,行访问时间只有在其他条件都满足了之后才能实现。列地址选通具有两个功能:锁存存储阵列相应的列地址,以及打开数据输出缓冲。下降沿之后,数据至少在tCAC时间内不可用,这是列地址选通后的访问时间。

当在读周期结束后变为高电平时,数据总线被关闭,并悬浮tOFF时间(输出缓冲关闭延迟)。在读(或写)周期结束时没有作用。可以在之前或之后改变,只要它的时序要求得到满足。

数据在下降沿到来以后保持不多于tCAC时间,且在下降沿之后保持不多于tRAC时间。周期结束时,数据总线缓冲在最早的和上升沿tOFF时间内被关闭。

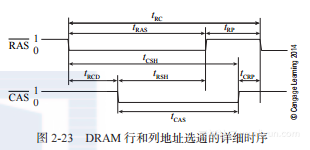

DRAM的读取周期时序图需要考虑的最后一个问题是,行和列地址选通的时序要求,如图2-23所示。和用来锁存地址、控制内部操作和三态缓冲器。

图2-23中的基本参数是tRC,即读周期时间,这是连续的存储器周期之间最短的持续时间。在每个读周期中,选通必须至少保持tRAS时间(行地址选通脉冲宽度)。典型的最大值为10 000ns,这是由于设备需要刷新且不能出现问题导致的,该时间是微处理器读周期的多倍。在失效后,它必须保持高电平至少tRP时间,这是行地址选通预充电时间(动态存储器芯片的相关内部操作)。时序的最后一个约束为相对的保持时间tRSH。必须在有效后保持低电平tRSH时间。

列地址选通时序的要求与行地址选通的类似。必须有效至少tCAS时间,在下一个下降沿到来之前必须失效至少tCRP时间,且从当前下降沿开始至少保持tCSH时间有效。

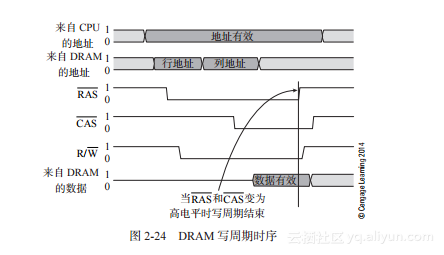

写周期时序

DRAM存储器的写周期比相应的读周期更复杂,因为对其和数据输入信号提出了严格的要求。通过对读周期时序图的介绍,这里不需要重复介绍相同的过程。图2-24给出了简化的DRAM存储器写周期的时序图。这是一个提前写周期(early write cycle),因为信号在变为低电平之前有效。某些DRAM的写周期中,信号是在变为低电平之后才有效的。读与写周期中的、以及地址输入的时序要求是相同的。

写命令信号,由信号的下降沿锁定,建立时间为tWCS。一旦有效,为低电平的最小持续时间为tWP,在下降沿之后至少tWCH时间后才允许失效。信号必须在信号上升沿到来之前至少有效tRWL时间,且在信号上升沿到来之前至少有效tCWL时间。写周期中的关键事件是信号的下降沿,因为它锁存信号和向DRAM输入的数据。

数据在信号的下降沿写入存储器。数据输入时序的需求简单直接,只涉及3个参数。写入存储器的数据必须在信号的下降沿到来之前有效tDS时间(数据建立时间),且在其后继续维持tDH时间(数据保持时间)。

2.3.2 DRAM技术的发展

前面已经介绍了基本的DRAM。下面开始介绍页(page)模式、半字节(nibble)模式、静态列(static column)模式等改进的DRAM。这些变化仍然利用行列地址输入多路复用,同时克服了访问之间预充电造成一些限制。

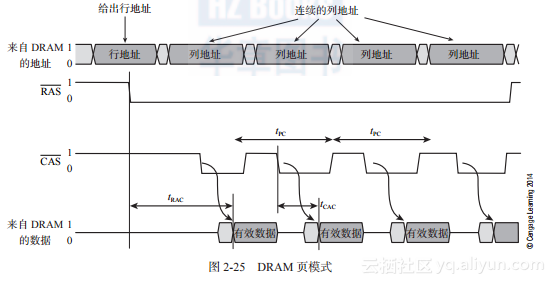

页模式允许快速访问给定行中的任意列位置,如图2-25所示。假设某1Mb的DRAM处于一个正常的读或写周期中。首先给定10位行地址,信号变为低电平有效将其锁存,从而选中一行。其次为列地址,然后是信号有效,接着访问给定位置。页模式通过给出连续的脉冲,且在每个选通信号下降沿锁存新的列地址来连续访问同一行中的数据。

连续页模式访问中,列访问周期是tPC,这大约是原访问周期时间的一半。页模式允许对单一行地址的突发访问,比基本DRAM周期时间要好。页模式对从连续地址访问一批数据(例如,成块数据传输或光栅扫描图形处理)来说特别有用的。页模式及其他突发模式可用符号4:2:2:2来描述,这意味着第一个访问延迟为4个周期,以后的数据元素只需要经过两个周期即可获得。今天,页模式DRAM已经过时(在大多数DDR2和DDR3之前的DRAM变种中也是这样)。

半字节模式DRAM具有一些页模式的特点但速度更快。半字节模式访问开始时与普通DRAM访问相同,都是先获取行地址再获取列地址。如果选通信号重复出现,则对连续4个位置进行读(或写)操作而不需要提供新的列地址。

图2-26给出了半字节模式的时序。不同于页模式,半字节模式只是在突发访问开始时锁存单一的列地址。接下来的访问顺序(使用循环出现的)以00、01、10、11、00、10的顺序出现。DRAM自己在内部自动产生序列地址。例如,如果访问位置0x0 1234,然后循环出现的,将访问的位置为0x0 1234,0x0 1235,0x0 1236和0x0 1237(按顺序访问)。第一个半字节模式访问时间与读或写周期的时间相同。后续访问时间要比普通的访问周期的一半还要少。

随着系统速度加快,DRAM制造商开发了降低DRAM访问时间的其他方法。扩展数据输出(extended data out,EDO)是DRAM页模式的变种,它比页模式DRAM具有更短的页周期时间。EDO设备在变为高电平时不关闭其输出。数据在下降沿有效,所以设计师可以使用信号来选通数据。

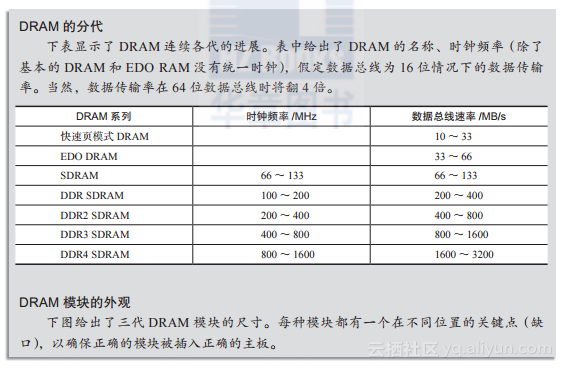

1. SDRAM

快速页模式DRAM和EDO DRAM都是DRAM的变种。DRAM技术史上第一个根本变化发生在1997年前后,出现了与以前的DRAM具有不同接口的同步DRAM(SDRAM)。1998年,SDRAM占有了DRAM存储器50%的世界市场。SDRAM使用系统时钟进行同步,采用了更复杂的接口可以从处理器接收已编码命令。例如,SDRAM使用组合控制信号来对命令进行编码,如读、写或预充电。SDRAM访问时间与DRAM系列其他成员的访问时间类似;然而,它的突发访问时间却相当短。

控制信号和指令在时钟的上升沿锁存,这样做简化了系统的设计。SDRAM中的控制寄存器定义了它的操作参数,如突发长度(即每个读或写周期访问的字数)。也就是,SDRAM是一种操作参数可以面向特定系统进行调整的可编程装置。

SDRAM具有多个存储体可以独立操作。图2-27描述了SDRAM的读周期。在时钟的上升沿获取命令和行地址(周期15ns意味着频率为66.67MHz)。列地址在下一个时钟上升沿读取。数据在读周期开始60ns后出现,类似DRAM的访问时间。但是,接下来的3个元素每隔15ns就会出现一个。

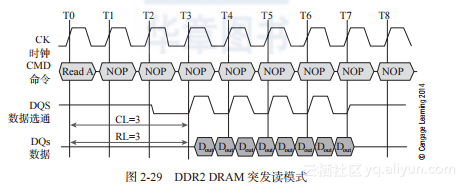

2. DDR DRAM

DDR DRAM或者double-data rate SDRAM,(双数据速率SDRAM),与传统SDRAM的内部存储机制稍有不同。DDR DRAM、SDRAM之间的区别在于其接口。DDR SDRAM在时钟的上升沿和下降沿都执行数据访问;即它以时钟频率两倍的速度提供数据。图2-28给出了DDR的读周期时序。一旦开始进行突发访问,数据在时钟的每个边缘都可出现。参数CAS延迟(CAS Latency,CL)以时钟周期为单位定义了从列地址选通有效至数据有效之间的时间。此参数是反映DDR性能的主要参数。其他3个与DRAM相关的参数是RL(读延迟)、AL(附加延迟)和BL(突发长度)。

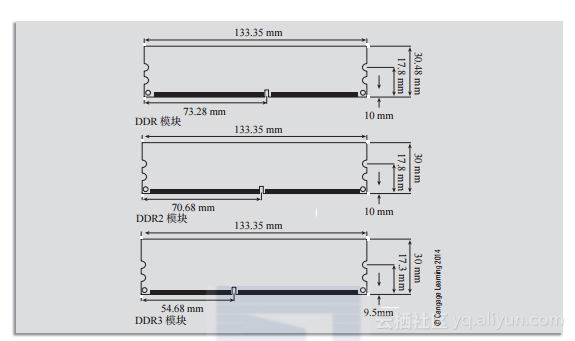

3. DDR2与DDR3 DRAM

每种技术的变种如DDR DRAM都有其寿命。DDR风光后由DDR2代替。DDR2风光后就引入了DDR3。现在DDR4还在等着。在微机世界中,每种技术的变种都伴随着新的主板芯片系列为其提供连接到主机CPU的接口。

与DDR相比,DDR2也是在时钟的上升沿和下降沿传输数据,但其更进一步,可以在每个时钟周期内执行4次数据传输。某个具有64位数据总线以266MHz频率工作的DDR2存储模块能够获得传输数据的峰值速率是64×266×106×4/8=8512MB/s。式中4表明每个周期传输4个数据。数据传输速率是数据值的1/8,因为每次数据传输需要8位。DDR2的最大信息传输速率是1066兆次传输/s。

DDR2和这个系列的后来成员在某种意义上说是可编程的,这是由于它们具有参数配置寄存器,可由主机系统装载操作参数。例如,可以定义DDR2 SDRAM如何进行刷新(前面说过,每个位元都需要周期性地更新,存储的数据需要再写一遍)。

DDR3是数据传输速率加倍原理的进一步扩展,相比DDR2其数据传输率又翻了一番,可以在每个时钟周期内进行8次访问。在增加数据传输率的同时,DDR3模块可以允许单个芯片的容量高达8Gb。Samsung在2009宣布第一款使用50ns技术的4Gb DDR3 DRAM,这仅仅在Intel刚成立时发布其1024位的DRAM后的40年。那时的人们很难想象,存储芯片的容量将在他的一生中以超过400万倍的速度增长。DDR3存储器内部由8个存储体而不像DDR2那样由4个存储体构成。增加存储体的个数可以增加交叉的程度。DDR3内核速度与DDR2的稍有不同。

DDR3-1600模块工作在200MHz,其周期时间为5ns,执行速度为1066兆次传输/s,对应的数据传输率为12800MB/s。图2-29给出了DDR2突发读操作的时序(来自Samsung DDR2 SDRAM Device Operating & Timing Diagram manual)。

动态存储器设计的一个重要趋势是降低工作电压。DDR2工作在1.8V,第一代DDR3工作在1.55V,后来的DDR3工作在1.35V。工作电压从1.8V降至1.35V可以降低功耗25%。

DRAM技术通过向运行多任务的复杂操作系统以及处理音频和视频的多媒体应用提供大容量、经济的、直接访问的存储器,使得PC世界蓬勃发展。下面会介绍只读存储器,它虽然只对PC世界有适度的影响,但对普适计算(例如,MP3播放器和数码相机)有更大的影响。

4. DDR4

2011年,正当DDR3以新的设计替换DDR2并越来越受欢迎的时候,DDR4出现了。Samsung是第一家提供DDR4模块的公司。新的DDR4技术比DRAM家族中以前的成员更快且能效更好。它采用新的电路设计技术,并且将电压从DDR3的1.55V降至1.2V以减少功耗。自Intel 1103 DRAM需要3股电源(+5V、-5V和12V)开始,已经走过了漫长的道路,该模块的数据传输率仅为2133比特/s。

介绍完主流的读/写存储设备后,在讨论正在兴起的(目前已经出现)未来主存储器支撑技术之前,先介绍一下只读存储器。

《计算机存储与外设》----2.3 DRAM相关推荐

- 计算机未来的储存装置,图说计算机存储设备

现在大家可能都已经对上GB的存储设备司空见惯了,可是也许您没曾想到20年这样容量的硬盘是同冰箱大小相仿的.今天的Royal Pingdom网站上撰写了一篇计算机存储设备历史的文章,用图片的形式回顾了之 ...

- 数据结构 (计算机存储、组织数据方式)

数据结构是计算机存储.组织数据的方式.数据结构是指相互之间存在一种或多种特定关系的数据元素的集合.通常情况下,精心选择的数据结构可以带来更高的运行或者存储效率.数据结构往往同高效的检索算法和索引技术有 ...

- tb计算机存储单位_如何节省数TB的云存储

tb计算机存储单位 Whatever cloud provider a company may use, costs are always a factor that influences decis ...

- 计算机存储数字,计算机是如何存储数字的

计算机存储都是以补码的形式存储的.原因是简化计算机的基本运算电路,使加减法都可以用加法来进行运算. 整数: 原码: 原码就是一个数的二进制形式,只不过最高位是用来表示符号位. 例:+1 = 000 ...

- 在线硬盘存储计算机,存储换算器 - 文件大小转换 - 电脑容量换算

本工具可以实现比特(b),字节(B),千字节(KB),兆字节(MB),千兆字节(GB),太字节(TB),拍字节(PB),艾字节(EB),泽字节(ZB),尧字节(YB),等各种容量单位间的换算. 换算率 ...

- 计算机存储单位试题,计算机存储试题及答案

计算机存储试题及答案 为帮助大家深入学习计算机,yjbys为大家分享最新的计算机数据模拟试题及答案如下: 1.计算机内部用于处理数据和指令的编码是__________. A.十进制码 B.二进制码 C ...

- 计算机存储单位:bit, Byte, KB, MB, GB, TB, PB, EB, ZB, BB

一.计算机的存储单位有哪些呢? 计算机存储单位一般用 bit, Byte, KB, MB, GB, TB, PB, EB, ZB, BB来表示, 我们经常将Byte简称为B,将KB简称问K.什么几K了 ...

- 计算机存储单位的换算关系

计算机存储单位的换算关系 1TB=1024GB 1GB=1024MB 1MB=1024KB 1KB=1024B 1B=8b 计算机存储单位一般用bit.B.KB.MB.GB.TB.PB.EB.ZB.Y ...

- 计算机存储单位 KB,MB,GB,TB,PB

计算机存储单位 bit(比特).Byte(字节).千字节(kb kilobyte).兆字节(MB megabyte).吉字节(GB gigabyte).太字节(TB terabyte).拍字节(PB ...

最新文章

- 有了这款可视化工具,Java 应用性能分析、调优 so easy...

- python中rim的用法_Python笔记(六)_函数

- 如何进入npm_如何用docsify在Github搭建自己的知识文档?

- 【推荐系统】面向科研的推荐系统Benchmark诞生!

- 论文阅读 R-FCN: Object Detection via Region-based Fully Convolutional Networks

- webdriver高级应用- 无人工干预地自动下载某个文件

- 一个程序员的时间管理“辛”路历程

- android显示超图地图,超图---简单地图显示

- Python实现m3u8下载mp4视频原理及源码

- HTML5期末大作业:关于家乡介绍主题网页设计——云南民族文化(8页) HTML+CSS+JavaScript 期末作业HTML代码 学生网页课程设计期末作业下载 web网页设计制作成品

- linux烧录到手机,新人求教,怎么烧录Linux系统到一个小芯片上?

- 遥感智能解译相关产品及公司

- vue删除数据,不刷新页面

- bilstm-crf_序列标注问题

- FineReport(帆软)关于柱状图数据标签被遮挡的问题处理

- usb启动盘提示vesamenu.c32 not a COM32R image

- java的关键业绩指标_SpreadJS前端开发案例:如何利用Javasrcipt创建财务关键业绩指标表...

- 数据库为啥查询那么慢?

- sparql 查询例子

- 基于matlab的光学薄膜特性分析,基于matlab的光学薄膜特性分析.doc

热门文章

- 如何有效地帮助新人融入项目中

- 计算机如果没有什么 就无法启动,电脑开机没有任何反应

- 【数据库】--- Redis

- CINTA作业四:群、子群

- 头晕和眩晕是怎样的感觉?3件小事来缓解!

- Xshell重启服务器

- python 问题Some characters could not be decoded, and were replaced with REPLACEMENT CHARACTER.

- Codeforces 869E. The Untended Antiquity (二维Fenwick,Hash)

- 题目描述: 某城市有一个火车站,铁轨铺设如图所示。 有n节车厢从A方向驶入车站,按进站顺序编号1~n。 现让这些火车按照某种特定的顺序进入B方向的铁轨并驶出车站。 为了重组车厢,可以借助中转站C。

- 力扣每日一题第495题提莫攻击