vivado生成mig_Xilinx-在Zynq上用MIG扩展内存(2)-Vivado篇

硬件平台:ZC706开发板

软件工具:Vivado 2013.2

Step 1: 创建工程

启动Vivado 2013.2,创建一个新的工程zc706_mig。选中Create project subdirectory。

选择RTL Project

一路Next,在Default Part页面选择ZC706开发板。

Step 2: 配置Zynq

在左面的Flow Navigator窗口,单击Create Block Design,Design Name填写zynq。

在Diagram Tab页里面添加IP ‘ZYNQ7 Processing System’。

双击processing_system7_1,打开配置界面。取消所有外设,仅仅保留UART。UART1使用MIO 48..49。关闭FCLK_CLK0的输出。

Step 3: 配置MIG

在Diagram Tab页里面添加IP ‘MIG 7 Series’。双击mig_7series_1,打开配置界面。

在Memory Selection页,选择DDR3

在Controller Options也,配置Clock Period为1250ps,配置Memory Type=SODIMMS; Memory Part=MT8JTF12864HZ-1G6。

在AXI Parameter页,配置Data Width=32, ID width=12。

在Memory Options页,配置Input Clock Period=5000ps(200MHz).

在FPGA Options页,配置System Clock=Differential,Reference Clock=Use System Clock,System Reset Polarity=ACTIVE HIGH。

在Extended FPGA Options页,选中DCI Cascade。

在IO Planning Options页,选择Fixed Pin Out,然后导入labfiles\zc706_mig_pinout.ucf,单击Validate,忽略warnings,单击Next。

在System Signals Selection页,单击Next。

在Summary页,单击Next。

在Simulation Options页,选择Accept,单击Next。

在PCB Information页,单击Next。

在Design Notes页,单击Generate。

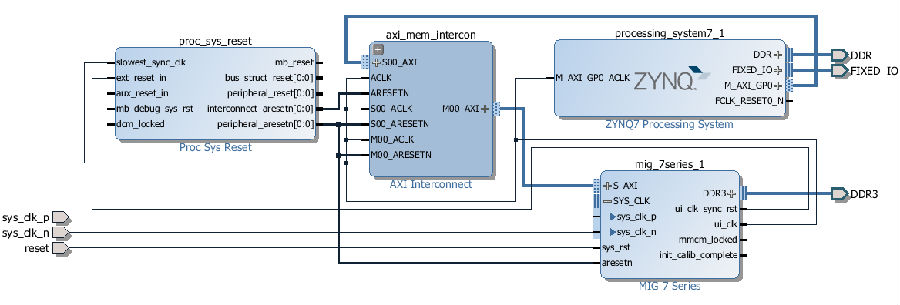

Step 4: 建立IP之间的连接

在Diagram Tab页, 单击窗口上部的Run Connection Automation,选择/mig_7series_1/S_AXI,系统将自动添加IP并建立部分连接。

单击窗口上部的Run Connection Automation,选择/mig_7series_1/sys_rst。

连接/mig_7series_1/ui_clk到processing_system7_1/M_AXI_GP0_ACLK

连接/mig_7series_1/aresetn到/proc_sys_rest/peripheral_aresetn[0:0]

单击窗口上部的Run Block Automation,选择processing_system7_1

单击/mig_7series_1/SYS_CLK前面的加号,展开这个接口。

选中/mig_7series_1/sys_clk_p,单击右键,选择Create Port。在弹出的窗口里面更改Type为Clock,填写Frequency(MHz)为200。

对/mig_7series_1/sys_clk_n执行同样的操作。

选中/mig_7series_1/DDR3接口,单击右键,选择Make External

单击Diagram Tab页左边最下面的Regenerate Layout按钮,由工具自动重新排布。生成的结果如下。是不是感觉非常漂亮?

Step 5: 创建约束

命名为system,将以下内容拷贝到约束文件中:

set_property LOC G9 [ get_ports sys_clk_n]

set_property IOSTANDARD DIFF_SSTL15 [ get_ports sys_clk_n]

set_property LOC H9 [ get_ports sys_clk_p]

set_property IOSTANDARD DIFF_SSTL15 [ get_ports sys_clk_p]

set_property LOC A8 [ get_ports reset]

set_property IOSTANDARD LVCMOS15 [ get_ports reset]

# additional constraints

#

create_clock -name sys_clk_pin -period "5.0" [get_ports "sys_clk_p"]

Step 6:设计验证

在Block Design窗口里面,在zynq.bd上面单击右键,选择Generate Output Products,然后再单击右键,选择Create HDL Wrapper。

在左面的Flow Navigator窗口,单击Generate Bitstream。

在我的计算机上,大约20分钟后,bit文件生成。

然后在Vivado中,单击File->Export->Export Hardware for SDK,选中Launch SDK。

在SDK里面,可以用模板“Memory Tests”创建一个工程,测试确认MIG工作正常。

以此为基础,开发者可以灵活的调整MIG的AXI端口和Memory端口的工作频率,完成贴合自己应用的嵌入式设计。

vivado生成mig_Xilinx-在Zynq上用MIG扩展内存(2)-Vivado篇相关推荐

- Vivado生成bit文件布局失败解决

1.1 Vivado生成bit文件布局失败解决 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)Vivado生成bit文件布局失败解决: 5)结束语. 1.1.2 本节引 ...

- Vivado生成bit文件报错彻底解决

1.1 Vivado生成bit文件报错彻底解决 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)Vivado生成bit文件报错彻底解决: 5)结束语. 1.1.2 本节引 ...

- Vivado生成bit文件出现error解决

1.1 Vivado生成bit文件出现error解决 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)Vivado生成bit文件出现error解决: 5)结束语. 1.1 ...

- 未指定的IO标准导致vivado生成bit文件报错

1.1 未指定的IO标准导致vivado生成bit文件报错 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)未指定的IO标准导致vivado生成bit文件报错: 5)结束 ...

- FPGA资源不足导致vivado生成bit失败

1.1 FPGA资源不足导致vivado生成bit失败 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA资源不足导致生成bit失败: 5)结束语. 1.1.2 本 ...

- Vitis初探—1.将设计从SDSoC/Vivado HLS迁移到Vitis上

〇.前言 2020.11.25日,Xilinx更新了Vitis2020.2版本.正好之前报名里Xilinx的自适应计算挑战赛,比赛要求使用Vitis平台进行开发,所以今天趁着新版本发布把我之前参加DA ...

- Vivado创建调用自定义IP上板验证

Vivado创建调用自定义IP上板验证 本次记录如何使用Vivado创建调用自定义IP上板验证 自定义IP(Key_test) 按键消抖功能的模块 然后调用此(Key_test) IP 在顶层文件进行 ...

- 【基于zynq的卷积神经网络加速器设计】(一)熟悉vivado和fpga开发流程:使用Vivado硬件调试烧写hello-world led闪烁程序实现及vivado软件仿真

HIGHLIGHT: vivado设计流程: note: 分析与综合 和 约束输入 可以调换顺序 [基于zynq的卷积神经网络加速器设计](一)熟悉vivado和fpga开发流程:使用Vivado硬件 ...

- php 上传图片并生成缩略图,php 图片上传并生成缩略图代码

本代码的功能是把你要上传的图片保存到服务器,然后再把当前图重按比例生成一个小的缩略图哦. if($_FILES['image']['size']){ if($_FILES['image']['type ...

最新文章

- nodejs运行python_如何在后台Python中运行子进程命令来启动nodejs服务器

- ES _source字段介绍——json文档,去掉的话无法更新部分文档,最重要的是无法reindex...

- LintCode-56.两数之和

- fedora8完美DNS教程

- boost::test模块测试树管理单元测试

- Xamarin开发笔记—百度在线语音合成

- 【转载】如何制作python安装模块(setup.py)

- 片段中未调用onActivityResult

- Ubuntu编译安装Keepalived

- Windows2019在IIS下添加.NET Framework 3.5 NetFx3 失败 (状态为:0x800f0950)的解决办法)

- KEIL的下载图标是灰色的怎么办

- 【WebGIS bug】WARNING: Too many active WebGL contexts. Oldest context will be lost.

- 基于PHP使用thinkphp开发的教学管理系统

- qpython 3h_QPython 3H

- 怎么注册tk域名_新.tk域名免费注册教程

- 拭血长短句手札【2013-2017】微信公众号 shixuemp

- python登录豆瓣_手把手教你用python模拟登录豆瓣

- 哈斯图 寻找 极小元与极大元 最小元与最大元 上界与下界 最小上界(上确界)和最大下界(下确界)(一看就会)附一练习题

- 名编辑电子杂志大师教程 | 仿古书翻页

- js判断当前浏览器的环境是微信、pc、还是手机端非微信环境