【FPGA】Spartan-6的时钟管理器(CMT)

目录

时钟管理器(CMT)

DCM

(1) 延时锁相环(DLL)。

(2) 数字频率综合器(DFS)。

(3) 相移单元(PS)。

(4) 状态逻辑。

DCM原语

PLL

组成

工作原理

PLL的原语

PLL作用

(1) PLL 对时钟网络去歪斜SKEW。

(2) PLL 用于频率合成。

(3) PLL用作抖动滤波器。

应用模型

(1) 时钟网络去歪斜。

(2) 零延迟缓冲器。

(3) DCM 驱动PLL。

(4) PLL 驱动DCM。

(5) PLL 到PLL 的连接。

时钟管理器(CMT)

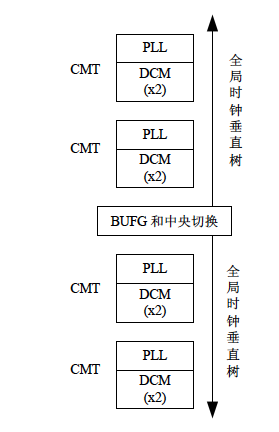

Spartan-6 CMT是一个灵活、高性能的时钟管理模块。它位于芯片中央、垂直的全局时钟网络旁。如图2-17所示,它包含一个PLL和两个DCM。

图2-17 Spartan-6 FPGA CMT片内布局图

DCM

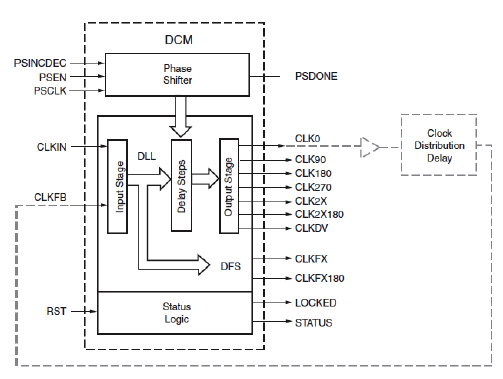

Spartan-6中的DCM与Spartan-3中的类似,如图2-18所示,同样由4部分组成。

图2-18 DCM 功能结构图

(1) 延时锁相环(DLL)。

DLL 延时锁相环可以根据输入时钟去除DCM 的输出时钟歪斜,以完全消除时钟分布延迟。其原理是将时钟输入(CLKIN)与一个反馈输入(CLKFB)进行比较,然后控制延迟线选择器,通过在DLL 路径中加入合适的延迟直到CLKIN 与CLKFB 重合。

DLL 输入时钟是CLKIN 和CLKFB,输出时钟信号是CLK0、CLK90、CLK180、CLK270、CLK2X、CLK2X180 和CLKDV。

(2) 数字频率综合器(DFS)。

DFS有两个用户寄存器,用来设置相对于输入时钟(CLKIN)倍频(CLKFX_MULTIPLY)和分频(CLKFX_DIVID)系数。DFS可以单独使用,还可以和DLL一起配合使用;如果DFS不和DLL一起使用,CLKIN和DFS输出之间没有对应的相位关系。DFS的输出为CLKFX和CLKFX180。

(3) 相移单元(PS)。

相移单元PS的输入信号有PSINCDEC、PSEN和PSCLK,输出信号为PSDONE和STATUS[0]。相移模式包括固定相移和可变相移。

固定相移是指DCM的9个时钟的相位输出,通常是输入时钟周期的若干分之一,固定相移值在设计中设定并在FPGA配置时载入FPGA。

除了固定相移,PS还支持可变相移,根据系统要求,通过数字接口(PSINCDEC、PSEN和PSCLK)动态改变相移。每次动态改变的相移值为DCM_DELAY_STEP,DCM_DELAY_STEP对应的范围可参考《Spartan-6数据手册》。

(4) 状态逻辑。

状态逻辑反映DCM的状态,对应两个输出信号LOCKED和STATUS[0]。

DCM原语

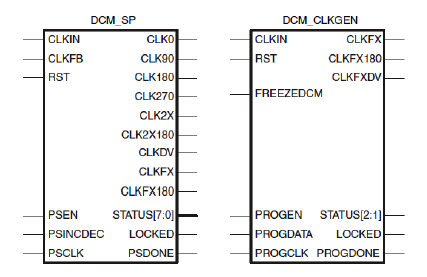

如图2-19所示,主要有2个DCM的原语调用,DCM_SP和DCM_CLKGEN。

图2-19 DCM原语

DCM_SP提供DCM的传统特性:时钟DESKEW、频率综合和固定及可变相移。

DCM_SP所有的属性都是在设计时确定,上电配置的时候编程到FPGA,除了动态相移功能外,所有的属性在运行时是不可以更改的。

DCM_CLKGEN提供了如下更多的DFS性能。

低抖动的CLKFX和CLKFX180输出。提高了输入时钟CLKIN的抖动容限。支持M和D的动态编程,动态设置CLKFX_MULTIPLY和CLKFX_DIVIDE。CLKFX_MULTIPLY和CLKFX_DIVIDE属性值范围更大。当输入时钟丢失时,自激振荡器工作。具有扩频功能。

在设计中特别要注意DCM_SP和DCM_CLKGEN的特性和参数,请参考《Spartan-6 时钟资源用户手册》。

PLL

Spartan-6 器件最多包含6 个CMT,12 个PLL。PLL 的主要用途是作为频率合成器,产生更宽范围的频率输出,在与CMT 中的DCM 连接时,具有良好的滤波功能。

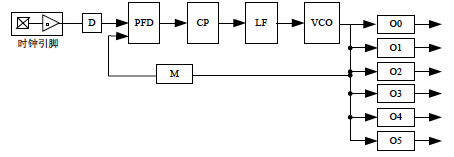

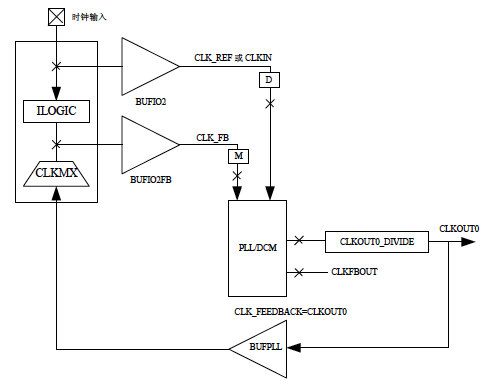

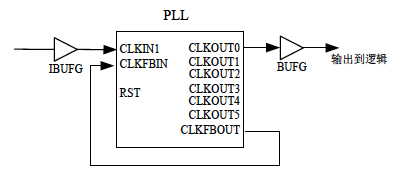

图2-20 所示为PLL 的功能框图。

图2-20 Spartan-6 PLL功能框图

组成

其中包括可编程计数器D、相位/频率检测器(Phase-Frequency Detector,PFD)、电荷泵(Charge Pump ,CP ) 、环路滤波器(Loop Filter , LF) 、压控震荡器(Voltage Controlled Oscillator,VCO)、O0~O5 为6 个可编程计数器。

工作原理

PFD将输入时钟与反馈时钟的相位和频率进行比较,产生的信号驱动CP 和LF,CP和LF 为VCO产生一个参考电压,这个参考电压将影响VCO的输出频率。那么VCO的频率是如何变化的呢?PFD完成2个时钟的比较后,产生CP和LF 的驱动信号,这个信号确定了VCO 应该工作在较高频率还是较低频率。当VCO工作频率过高时,PFD触发一个下降信号,致使控制电压下降,从而降低VCO的工作频率。当VCO工作频率过低时,PFD触发一个上升信号,致使电压上升。VCO 共产生8个输出相位,每个输出相位都可选作输出计数器的参考时钟,如图2-20所示。另外PLL 还提供了一个专用计数器M,用来控制PLL的反馈时钟,以实现大范围频率合成。6个“O”计数器可以独立编程,例如,O0可以编程为进行二分频操作,而O1编程为进行三分频操作。唯一的限制是VCO的工作频率对所有输出计数器来说必须相同,因为VCO驱动所有计数器。使用专用PLL 布线资源,必须将CLK_FEEDBACK设置CLKOUT0,按照图2-21所示使用BUFPLL和BUFIO2FB。

图2-21 带CLKOUT0反馈的PLL

当使用CLKOUT0的专用反馈路径时,输出计数器CLKOUT0_DIVIDE将影响VCO频率,fVCO=FIN×M×CLKOUT0_DIVIDE/D。

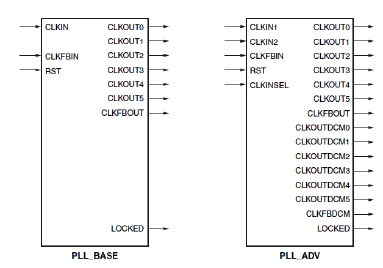

PLL的原语

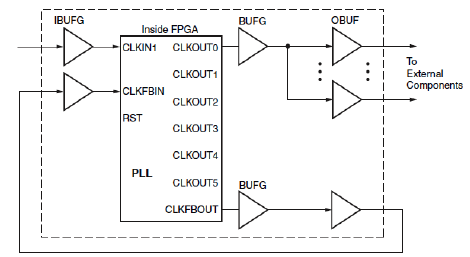

图2-22所示为PLL常用的两个模块,PLL_BASE和PLL_ADV。PLL_BASE允许使用独立的PLL 的最常用功能,包括时钟去歪斜、频率合成、粗粒度相移和占空比编程等。

PLL_ADV具备所有PLL_BASE功能,它具有更多的时钟输出。

图2-22 PLL的原语

PLL作用

Spartan-6 PLL是为支持时钟网络去歪斜SKEW、频率合成和减少抖动而设计的混合信号模块。接下来将详细讨论PLL 的这3种作用。

(1) PLL 对时钟网络去歪斜SKEW。

在许多情况下,设计人员在其I/O时序预算中不希望有时钟网络的延迟。其实,用PLL/DLL就可以解决这个问题,因为PLL/DLL具有补偿时钟网络的延迟的功能。当然,包括Spartan-6中的PLL。一个与参考时钟CLKIN的频率相匹配的时钟(通常是CLKFBOUT或CLKOUT0)连接到BUFG,并且反馈到PLL的CLKFB引脚。其余输出仍可用来合成更多用户所需频率。这样一来,所有的输出时钟就会与参考时钟之间有一个指定的相位关系。为了精确地降低由于时钟输入布线引起的歪斜,建议采用图2-21 所示的方法,使用BUFIO2FB缓冲器。

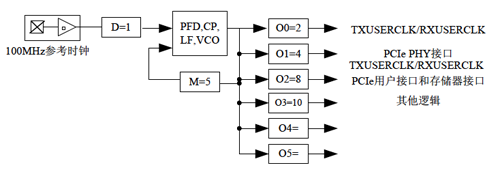

(2) PLL 用于频率合成。

PLL还可以用于频率合成。在这种应用中,PLL不能用于时钟网络去歪斜,而是用来为其他模块提供时钟。在这种模式下,PLL反馈通路因为要将所有布线保留为局部布线而应设置成internal反馈模式,以尽量减少抖动。图2-23所示为将PLL配置成频率合成器的示例。

图2-23 仅用于频率合成的PLL

在本例中,输入为100MHz参考时钟,设置M=5,D=1,可使VCO晶振的频率为500MHz(100MHz×5),6个PLL输出中的4个编程提供以下时钟。

250MHz GTP收发器时钟TXUSRCLK和RXUSRCLK。125MHz PCI Express PHY时钟。62.5MHz PCI Express用户接口和BRAM接口时钟。50MHz逻辑时钟。

在此示例中,参考时钟和输出时钟之间没有相位关系,但是各输出时钟之间要求有相位关系。

(3) PLL用作抖动滤波器。

PLL始终可以降低参考时钟上固有的抖动。PLL可以被例化以滤掉外部时钟在驱动另一个逻辑模块前(包括DCM)的抖动。作为抖动滤波器,PLL通常被简单地视为一个缓冲器,在其输出上重新生成输入频率(例如,FIN=100MHz,FOUT=100MHz)。通常,将PLL的BANDWIDTH属性设置为Low,可以实现较强的抖动滤波,但要注意,将BANDWIDTH设置为Low会导致PLL的静态偏差增大。

如何使用PLL呢?通常有如下几种方法。

ISE软件中的PLL向导可以帮助生成各种PLL参数。可以手动将PLL例化成一个组件。将PLL与IP核合并,IP核将包含并管理PLL。

应用模型

PLL有5种应用模型,下面分别介绍。

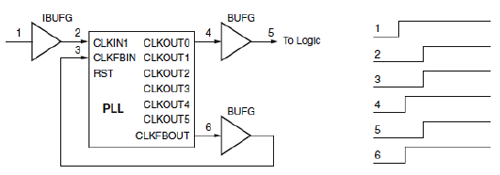

(1) 时钟网络去歪斜。

PLL的主要用途之一是时钟网络去歪斜。图2-24所示为这种模式下的PLL。O计数器之一的时钟输出用来驱动片内逻辑或I/O。反馈计数器用来控制输入时钟与输出时钟之间的精确相位关系(例如,当需要90°相移时)。右侧所示相关时钟的波形是输入时钟与输出时钟需要相位对齐的情况。这种PLL的配置方式最灵活,但它需要两个全局时钟网络。

图2-24 PLL使用两个BUFG的时钟去歪斜

这里,对反馈时钟有些限制,也就是PFD的2个输入时钟的频率必须完全相同。因此,必须满足下列关系式:

ƒIN/D=ƒFB=ƒVCO/M

例如,如果ƒIN是166MHz,D=1,M=3,O=1,则VCO的输出时钟频率和PLL的时钟(CLKBOUT)输出的频率都是498MHz。因为反馈通路中的M值是3,所以PFD上的两个输入时钟频率都是166MHz。

另一种更复杂的情况是输入频率为66.66MHz,D=2,M=15,O=2。在这种情况下,VCO的频率是500MHz,而O的输出频率是250MHz。所以,PFD上的反馈频率是500/15,即33.33MHz,与PFD上输入时钟频率的66.66MHz/2相符。

如果PLL用作频率合成器或抖动滤波器,并且PLL输入时钟与PLL输出时钟之间不要求有相位关系,那么PLL反馈可以是PLL的内部反馈。因为反馈时钟根本不通过内核电源供电,所以反馈时钟不受内核电源噪声干扰,因而PLL的性能会有所提升,如图2-25所示。当然,CLKIN信号和BUFG上引入的噪声依然存在。

图2-25 具有内部反馈的PLL

(2) 零延迟缓冲器。

如果系统中只有一个时钟,而这个时钟又需要驱动到所有的器件,为了保证时钟到达各目的器件之间的歪斜尽可能小,该如何实现这个应用呢?这时,就需要用PLL的零延迟缓冲器的应用模式。如图2-26 所示,其中,反馈信号在片外传递,经过了一段PCB板的走线。使用这种配置,可以保证在FPGA的时钟输入引脚和外部器件的时钟输入引脚时钟边沿是对齐的。很显然,在反馈路径中,PCB走线的最大延迟是有限制的。

图2-26 零延迟缓冲器

在某些情况下,由于外部器件输入电容与FPGA反馈路径上的输入电容存在差异,很难实现精准对齐。例如,如果外部器件有1pF~4pF的输入电容,而FPGA 的输入电容是8pF,这样一来,信号斜率就会存在差异,这是基本的时钟歪斜。为了确保时序,设计人员有必要了解这种问题的存在。

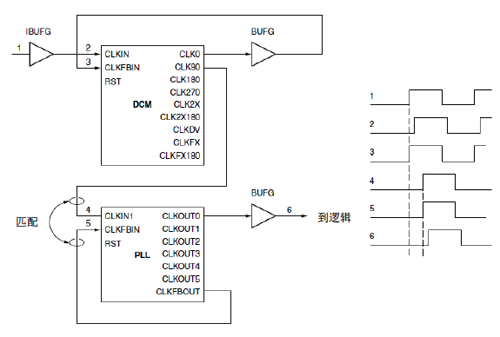

(3) DCM 驱动PLL。

DCM提供了一种生成精确相移时钟的好方法,但是,DCM不能降低参考时钟固有的抖动。PLL可用来降低DCM输出时钟抖动。如图2-27所示,将PLL配置成不引入任何相移(通过PLL的零延迟)的模式,框图右侧所示为相关波形。当使用DCM的输出直接驱动PLL时,DCM和PLL必须同处在一个CMT模块内。这种实现方案在局部专用布线上产生的噪声量最小,因此是首选方案。不过,也可以把DCM输出CLK90连接到BUFG,再去驱动PLL的CLKIN输入。

图2-27 DCM 驱动PLL 以降低抖动

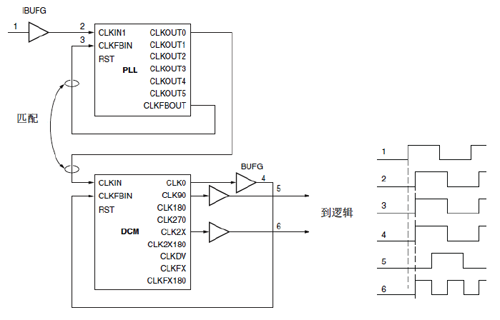

(4) PLL 驱动DCM。

减少时钟抖动的另一种可选方案是在输入时钟抖动传入DCM之前用PLL将其清除。这样可以改善所有DCM的输出抖动,但DCM附加的任何抖动都仍会传到时钟输出。PLL和DCM应处在同一个CMT模块中,因为PLL与DCM之间存在用来支持零延迟模式的专用资源。如果PLL和DCM不在同一个CMT中,那么唯一的连接就是通过一个能抑制歪斜可能性的BUFG。只要参考频率可以由一个PLL生成,则一个PLL即可驱动多个DCM。例如,如果将一个33MHz的参考时钟送入PLL,而设计用一个DCM在200MHz频率下工作,同时用另一个在100MHz频率下工作,那么VCO就可以在600MHz(M1=18)频率下工作。可以对VCO的频率进行三分频以生成200MHz的时钟,同时可以对另一个计数器进

行六分频以生成100MHz的时钟。对于图2-28中的示例,一个PLL可以驱动两个DCM。

图2-28 PLL驱动一个DCM

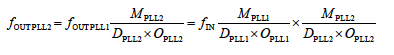

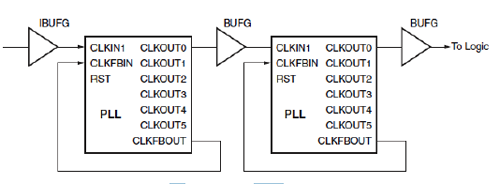

(5) PLL 到PLL 的连接。

可以级联PLL,以便生成更大范围的时钟频率。公式2-1所示为最终输出频率与输入频率之间的关系。图2-29所示为两个PLL的级联,第一个PLL的输出连接到BUFG,再连接到第二个PLL的CLKIN引脚。此路径具有最小的器件抖动。

公式2-1:

图2-29 PLL驱动PLL

点击打开链接

【FPGA】Spartan-6的时钟管理器(CMT)相关推荐

- MMCME2_ADV介绍 高级混合模式时钟管理器(7 Series FPGA)

目录 MMCME2_ADV 高级混合模式时钟管理器(Advanced Mixed Mode Clock Manager) Introduction Design Entry Method 端口描述(P ...

- Virtex-6器件的时钟资源、混合模式时钟管理器(MMCM)

时钟资源 为了更好的控制时钟,Virtex-6器件分成若干个时钟区域,最小器件有6个区域,最大器件有18个区域.每个时钟区域高40个CLB.在时钟设计中,推荐使用片上专用的时钟资源,不推荐使用本地时钟 ...

- Xilinx中时钟资源:模式时钟管理器(MMCM)的使用

混合模式时钟管理器(MMCM) 除了丰富的时钟网络以外,Xilinx还提供了强大的时钟管理功能,提供更多更灵活的时钟.Xilinx在时钟管理上不断改进,从Virtex-4的纯数字管理单元DCM,发展到 ...

- FPGA - 7系列 FPGA内部结构之Clocking -03- 时钟管理模块(CMT)

前言 本文节选UG472的第三章,进行整理翻译,用于介绍7系列 FPGA的时钟管理模块的内部结构以及相关用法.本文介绍的CMT在FPGA开发设计中是比较重要的一个内容,因此文章篇幅也相对较长. 文章目 ...

- FPGA芯片结构(可编程输入输出单元IOB/可配置逻辑块CLB/数字时钟管理模块DCM/ 嵌入式块RAM(BRAM)/丰富的布线资源/ 底层内嵌功能单元/内嵌专用硬核)

目前主流的FPGA仍是基于查找表技术的,已经远远超出了先前版本的基本性能,并且整合了常用功能(如RAM.时钟管理 和DSP)的硬核(ASIC型)模块.如图1-1所示(注:图1-1只是一个示意图,实际上 ...

- 赛灵思FPGA中的主要时钟资源介绍

把握DCM.PLL.PMCD 和MMCM 知识是稳健可靠的时钟设计策略的基础. 赛灵思在其FPGA 中提供了丰富的时钟资源,大多数设计人员在他们的FPGA 设计中或多或少都会用到.不过对FPGA设计新 ...

- UltraScale时钟资源和时钟管理模块

UltraScale时钟资源和时钟管理模块 绪论 图2.1和2.2给出了UltraScale结构的时钟结构.从图中可以看出,基本的结构是由表示分段时钟行和列的CR块构成的CR以一个单元的方式排列,从而 ...

- Spartan-6的时钟管理 DCM与 PLL详细介绍

本文转自:https://blog.csdn.net/Reborn_Lee/article/details/80351618 时钟管理器(CMT) Spartan-6 CMT是一个灵活.高性能的时钟管 ...

- S3C2443时钟管理

S3C2443时钟管理 S3C2443有两个PLL用来产生内部时钟,分别是MPLL和EPLL,其中MPLL为包括ARM,AHB和APB的总体功能模块产生内部时钟,而EPLL为比如是USB,I2S和ca ...

最新文章

- 删库跑路升级版,著名大厂员工离职为报复公司,直接删虚拟机!

- 深入理解Java Proxy和CGLIB动态代理原理

- “面试不败计划”:多线程

- PHP操作mongodb数据库操作类

- python学习实例(2)

- 看看大货车到底有多少盲区,肯定用得到!救命的!

- Google Cloud大规模宕机;中国正式进入 5G 商用元年!苹果发布SwiftUI |开发者周刊...

- Windows自动关机命令

- 【2020.10.27 牛客 普及组 模拟赛5】T4 飞行棋

- 自动升级Golang版本

- 播放超1200w,仅21w粉的B站UP主靠带货也能引爆B站

- visual studio 2008 提示 “函数xxx 已有主体”

- Intel无线网卡linux,Gentoo 安装之intel无线网卡篇

- Ink脚本语言学习笔记(小结)

- 经典功率谱估计(直接法、间接法、直接法的改进(包括Bartlett法、Welch法))

- 企业实战zabbix(7)--结合qqmail(报警信息发给qq用户)

- OPC UA - Open62541学习

- 【Cuckoo】add_path()失败 和 report.json太大解决办法

- Android自动化测试工具SoloPi

- 经纬度 十进制 和 度分秒 转换

热门文章

- 流氓软件彻底免疫程序 v2.2 绿色版

- SQL Server 数据库崩溃后的恢复之法

- voliate修饰数组有作用吗_Arrays.asList()真的就把数组转换为了List集合吗?

- 三元组顺序表表示的稀疏矩阵加法_数据结构实验题(三元组顺序表表示的稀疏矩阵转置运算)...

- python中options类_python中的optionParser模块

- python生成时间戳_python生成13位或16位时间戳以及反向解析时间戳的实例

- 常用计算机主要硬件设备,个人计算机常用的输出设备41.计算机硬件的组成部分主要包括:...

- 计算机内部使用什么方法技术,计算机内部使用什么技术

- 一个很奇怪的 OpenCV出错:resize的坑

- AI Studio 不同环境下的执行速度