Xilinx FPGA用户原语介绍

原语,即primitive。不同的厂商,原语不同;同一家的FPGA,不同型号的芯片,可以也不一样;原语类似最底层的描述方法。使用原语的好处,可以直接例化使用,不用定制IP;即可通过复制原语的语句,然后例化IP,就可使用;Xilinx是通过直接修改原语中的参数再例化IP来使用;Xilinx公司的原语分为10类,包括:计算组件,IO端口组件,寄存器/锁存器,时钟组件,处理器组件,移位寄存器,配置和检测组件,RAM/ROM组件,Slice/CLB组件,G-tranceiver。下图所示为UG799中对原语的分类列表。

项目中主要用到的原语与IO端口有关,所以基本在Input/Output Functions 和IO两类中。下面着重介绍实际中所用到的几个原语,芯片A7系列。

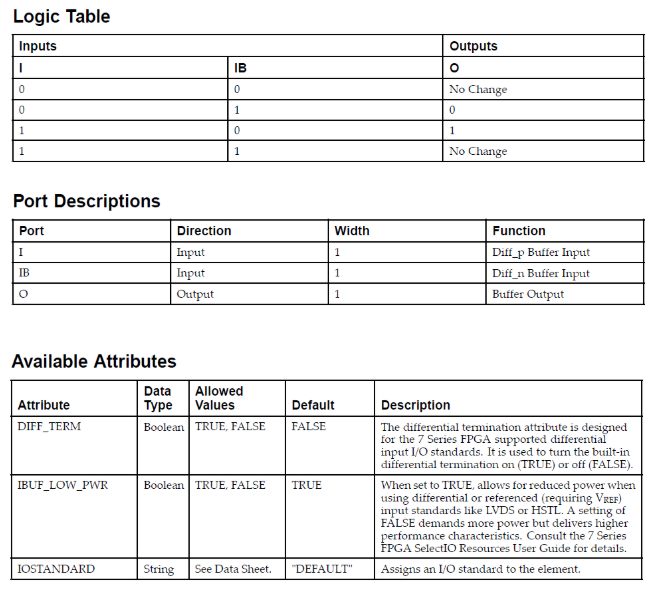

1. IBUF和IBUFDS(IO)

IBUF是输入缓存,一般vivado会自动给输入信号加上,IBUFDS是IBUF的差分形式,支持低压差分信号(如LVCMOS、LVDS等)。在IBUFDS中,一个电平接口用两个独特的电平接口(I和IB)表示。一个可以认为是主信号,另一个可以认为是从信号。主信号和从信号是同一个逻辑信号,但是相位相反。

举例说明:

LVDS_25的差分输入的ADC数据。

IBUFDS #( // 差分输入原语,用于LVDS_25端口

.DIFF_TERM("TRUE"),

.IOSTANDARD("LVDS_25")

) IBUFDS_ADC01 (

.O(ADC01_D[i]),

.I(ADC01_P_D[i]),

.IB(ADC01_N_D[i])

);

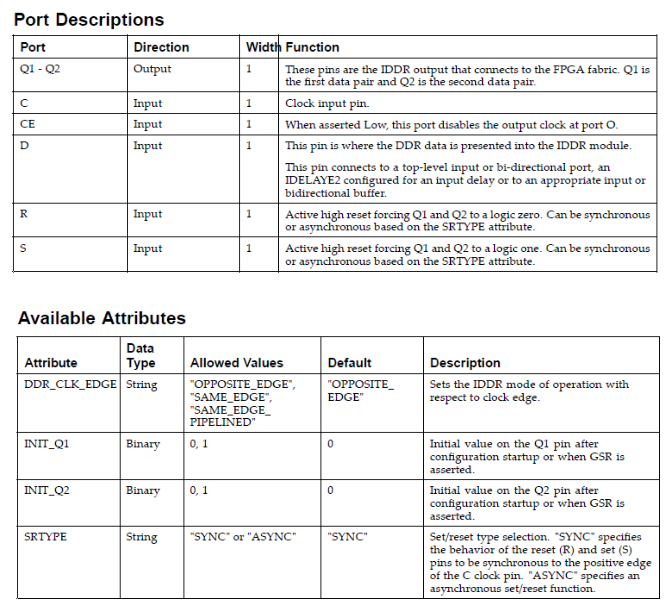

2. IDDR(Input/Output Functions)

被设计用来接收DDR数据,避免额外的时序复杂性。

举例说明:

差分数据源经过差分转单端后,生产ADC01_D,在同步时钟ADC01_DCO的驱动下,产生DDR数据adc01_a_d和adc01_b_d。

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"),

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.SRTYPE("SYNC")

) IDDR_ADC01_D (

.Q1(adc01_a_d),

.Q2(adc01_b_d),

.C(ADC01_DCO),

.CE(1'b1),

.D(ADC01_D),

.R(1'b0),

.S(1'b0)

);

3. IBUFG和IBUFGDS(IO)

IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。 IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。

IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

举例说明:

差分时钟芯片输入的100MHz时钟,作为FPGA的全局时钟。

IBUFGDS #(

.DIFF_TERM ("TRUE" ),

.IBUF_LOW_PWR ("FALSE")

) u_ibufg_clk_100 (

.I (FP_CLK_100M_P),

.IB (FP_CLK_100M_N),

.O (clk_100m )

);

Xilinx FPGA用户原语介绍相关推荐

- 【Xilinx DDR3】Xilinx FPGA DDR3深度介绍

从SDRAM到DDR3 SDRAM:(Dynchronous Dynamic Random Access Memory)同步动态随机存储器 同步时至其始终频率与CPU前端总线的系统时钟频率相同,并且内 ...

- Xilinx FPGA全局介绍

Xilinx FPGA全局介绍 现场可编程门阵列 (FPGA) 具有诸多特性,无论是单独使用,抑或采用多样化架构,皆可作为宝贵的计算资产:许多设计人员并不熟悉 FPGA,亦不清楚如何将这类器件整合到设 ...

- (28)XIlinx FPGA 原语简介(FPGA不积跬步101)

1 引言 原语,即primitive.笔者主要从事Xilinx FPGA开发,这里只介绍XIlinx FPGA原语.使用原语的好处,可以直接例化使用,不用定制IP:项目开发中经常用到和IO有关的原语. ...

- Xilinx 原语简介--(Xilinx FPGA开发实用教程)

目录 前言 1.Xilinx 原语简介 1.1 时钟组件原语(Clock Components) 1.1.1 BUFG 1.1.2 BUFGMUX 1.2 I/O端口组件(IO Components) ...

- Xilinx FPGA平台GTX简易使用教程(五)GTX收发测试及示例工程介绍

GTX IP配置完了,你不得搞个回环测试一番? 汇总篇: Xilinx FPGA平台GTX简易使用教程(汇总篇) 目录 前言 一.示例工程Example Design 1.1 gtx_support模 ...

- Xilinx FPGA DDR3设计(二)时钟介绍

引言:本文介绍Xilinx FPGA外接DDR3时钟相关参数及配置. 1.DDR3芯片时钟.位宽和数据带宽 以MT41K256M16RH-125为例,DDR3关键时序参数如图1所示. 1.1 DDR3 ...

- 《Xilinx - UG471中文翻译》(3)OSERDESE2原语介绍

FPGA大部分拿来做接口,不就是靠的SelectIO么~ 目录 一.前言 二.输出(并-转-串)逻辑资源 2.1数据(并-转-串)转换器 2.2 3-State Parallel-to-Serial ...

- 《Xilinx - UG471中文翻译》(2)ISERDESE2原语介绍

目录 1.前言 2.ISERDESE2原语介绍 3.原语例化 4.ISERDESE2框图 5. ISERDESE2端口信号 5.1时钟接口 5.2并行数据输出 5.3 数据输出选择 5.4级联接口 6 ...

- 《Xilinx - UG471中文翻译》(1)IDELAYE2原语介绍

目录 一.7 系列FPGAs SelectIO 资源 二.selectIO的逻辑资源 2.1 ILOGIC 2.2 IDELAY 2.3 IDELAYCTRL 2.4 ODELAY 2.5 OLOGI ...

最新文章

- 我拷贝大文件的时候报“超过文件大小限制”错误,怎样突破这个限制?

- MySQL删除关联表的数据

- Android7.0占用空间,Android7.0 开发者注意事项

- SwiftUI 很难赶上 UIKit?

- 怎样用计算机算出圆周率,古代没有计算机的时代 祖冲之是如何算出圆周率的...

- k近邻法的实现:kd树

- 苹果手机长截屏_发现一个手机必备软件

- mysql安装教程 2018_sql server 2018下载

- Linux之VM12+ CentOS7安装以及网络配置

- 速达启动时显示“对象名ACCSET无效“

- matlab盒子分形维数_根据计盒维数原理求一维曲线分形维数的matlab程序

- Tableau自定义调色板

- drupal mysql hash密码_變更drupal7用戶密碼加密方式

- 紫光扫描仪ocr_清华紫光扫描仪的安装教程及使用方法

- 【Lv1-Lesson004】Imperative Sentences

- 苹果IOS模拟器电脑版用哪个好 逍遥模拟器玩部分苹果账号互通

- 计算机应用基础与实训教程word2003文字处理软件 教学目标,计算机基础教学计划多篇...

- 运营商,我看未必成为夕阳行业

- 第一章-一大波数正在靠近——排序

- html+ajax登陆,jQuery+Ajax模拟用户登录功能的实现代码

热门文章

- mvc ajax 页面不刷新页面,如何在不刷新页面MVC C#的情况下显示不同的值

- window.location.href如何多次请求_测试同学必会系列之如何进行幂等性的测试

- 如何设置几个循环出来的span其中一个宽度_css几个概念

- html文件中用import,@import引入CSS文件

- [leetcode]746. 使用最小花费爬楼梯

- hdfs+zookeeper+hbase分布式在k8s中部署(本文已过期)

- java读取、生成图片

- jQuery Mobile中选择select的data-*选项

- tensorflow错误:InvalidArgumentError (see above for traceback): Cannot assign a device for operation

- 图像处理五:python读取图片的几种方式