用移位寄存器实现边沿检测(功能仿真及ISE综合)

目录

边沿检测

这是如何实现的呢?

下面给出Verilog HDL代码:

给出测试代码:

在Modelsim进行功能仿真:

ISE中进行综合得到RTL Schematic:

边沿检测

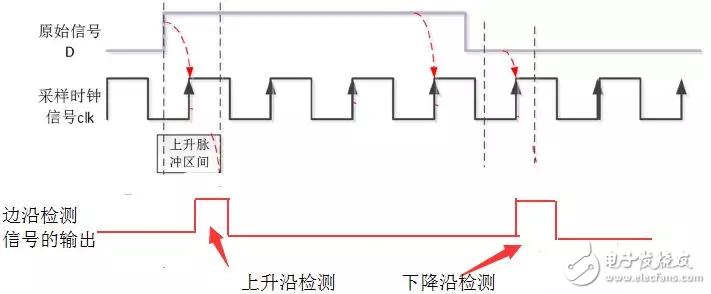

顾名思义,就是检测一个信号的边沿,当信号上升沿或下降沿到来时,获取一个脉冲信号。

时序图如下图:

这是如何实现的呢?

下面给出分析过程:

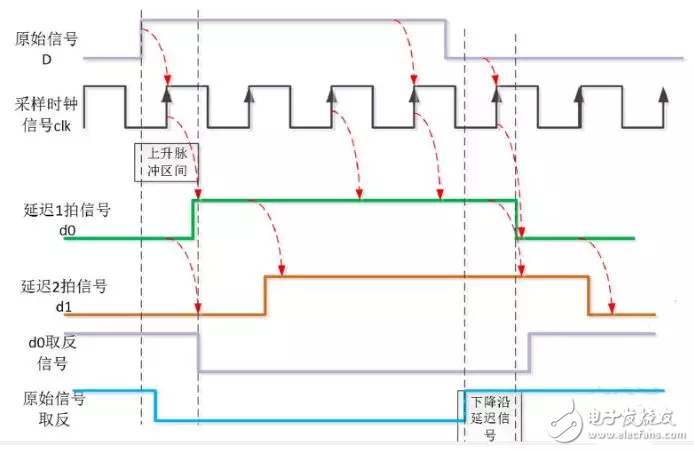

如下图:

d0为输入信号D延迟1拍得到的信号,同理d2是输入信号D延迟2拍得到的信号,上图同时给出了d0和D的取反信号。

可以发现:

原始信号与延迟一拍的信号 d0 的反向信号相与,就是上升沿脉冲;

而原始信号取反,然后与延迟一拍信号d0相与就是下降沿脉冲。

如果担心采样不稳定,可以利用延迟两拍的 d1 信号进行相 与。如果担心不定态,还可以将脉冲信号进行锁存。

下面给出Verilog HDL代码:

//脉冲检测

module dff(clk, D, reset, D_falling_edge, D_rising_edge);input clk;

input D;

input reset;

output D_rising_edge,D_falling_edge;reg d0;

reg d1;

reg Q;always @(posedge clk or negedge reset)

beginif(!reset)begind0 <= 1'b0;d1 <= 1'b0;Q <= 1'b0;endelsebegind0 <= D;d1 <= d0;Q <= d1;end

endassign D_falling_edge = d0 & (~D);

assign D_rising_edge = (~d0) & D;endmodule

给出测试代码:

//测试文件

module dff_tb;

reg D;

reg clk;

reg reset;

wire D_falling_edge, D_rising_edge;always

begin#10 clk = ~clk;

endinitial

beginclk = 1'b0;reset = 1'b0;D = 1'b0;#30 reset = 1'b1;#30 D = 1'b1;#80 D = 1'b0;enddff u1(.clk(clk), .reset(reset), .D(D), .D_falling_edge(D_falling_edge), .D_rising_edge(D_rising_edge));endmodule

在Modelsim进行功能仿真:

ISE中进行综合得到RTL Schematic:

这个原理图我们是可以看懂的,RTL Schematic就是寄存器传输级电路原理图,它是由各门电路组成,通过看RTL图可以初步验证自己的HDL描述是否正确。

参考文献:http://www.elecfans.com/emb/fpga/20180415662221.html

用移位寄存器实现边沿检测(功能仿真及ISE综合)相关推荐

- 模6计数器以及模10计数器(Verilog HDL语言设计)(Modelsim仿真与ISE综合)

目录 前言 模6计数器 Verilog HDL语言描述 测试文件 仿真电路图 RTL Schematic Technology Schematic 模10计数器 Verilog HDL语言描述 测试文 ...

- 边沿检测 Verilog

1.用verilog实现1bit信号边沿检测功能,输出一个周期宽度的脉冲信号 定义了一个2位的寄存器变量data_r,data_r[0]用来存储当前的状态,data_r[1]用来存储上一拍的状态 每个 ...

- FPGA设计心得(2)边沿检测的问题进一步说明(仿真中一定能得到上升沿的设计)

文章目录 背景 新检测方法 旧检测方法 改进旧检测方法 设计介绍 设计代码 仿真情况 仿真图 最后想提出的问题 同行邀请 工程分享 背景 关于边沿检测,写过的博文也很多,不下于4篇了,当然都是学习过程 ...

- FPGA之道(83)功能仿真之仿真语法(Graphic Waveform )

文章目录 前言 仿真语法 Graphic Waveform 数字波形简介 从实际到仿真 实际系统检测 软件仿真模拟 "Hello world"之Graphic Waveform 待 ...

- 【Verilog HDL 训练】第 06 天(边沿检测)

1. 复习verilog语法 [选做题] - reg和wire的区别 寄存器数据类型 Verilog中规定,凡是在程序块中被赋值的变量,都必须是寄存器类型的.(程序块:例如always块) 这里未免还 ...

- HDLBits答案(10)_D触发器、同步与异步复位、脉冲边沿检测

D触发器.同步与异步复位.脉冲边沿检测 HDLBits链接 D触发器 定义: D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,触发器具有两个稳定状态,即"0"和&qu ...

- 【FPGA】基于OV5640的 图像边沿检测

目录 一 项目结构 1.1 设计思路 1.2 设计流程 二 接口设计 2.1 摄像头配置模块 2.2 IIC_master 模块 之后就进行数据采集 2.3 采集数据模块 2.4 灰度转化 2.5 ...

- c语言sobel边缘检测,Sobel图像边沿检测算法的优化设计与实现

0 引言 图像边沿是图像的基本特征,是图像分割.特征提取等图像分析的重要依据,目前已广泛应用于目标识别.机器视觉和运动目标跟踪等领域.现今已有多种边沿检测算法以及一些改进方式,但各种算法都有各自的优缺 ...

- fpga时序逻辑(三段式状态机模板、rom实现、边沿检测)

目录 VL21 根据状态转移表实现时序电路 VL22 根据状态转移图实现时序电路 VL23 ROM的简单实现 VL24 边沿检测 VL21 根据状态转移表实现时序电路 题目分析: 1.使用三段式状态机 ...

最新文章

- 如何将APACHE许可证应用于您的工作

- html5之form表单

- Fast digital I/O for Arduino

- 35 岁程序员的独家面试经历

- mysql保存plc数据_MySQL空间数据的保存

- 全球如何应对新冠大流行?科学子刊社论:数据驱动模型指导

- java版mosquitto客户端使用SSL功能的具体操作总结

- bzoj 1070: [SCOI2007]修车【最小费用最大流】

- Linus 谈软件开发管理经验(转载)

- linux进程map,linux内存优化一文中 查看进程mem_map 的实现

- linux空格转义,如何在bash循环列表中转义空格?

- python 分页插件

- codesys采用G代码实现圆弧插补和螺旋插补的可视化仿真

- 知识图谱-构建:知识图谱构建流程【本体构建、知识抽取(实体抽取、 关系抽取、属性抽取)、知识表示、知识融合、知识存储】

- 迪斯科算法_为什么迪斯科极乐世界如此可重播

- 头条号权重高有什么优势?头条权重在线查询

- 解9*9数独算法(C++)

- linux 工具——终端分屏与vim分屏

- 推荐 8 个超实用的谷歌 Chrome 插件,大牛都在用

- 空间3点求三点所在空间圆的圆心空间坐标

热门文章

- 从零开始学ASP.NET

- 初探maven插件机制

- mysql acer_Acer电脑【no bootable device】引导修复

- JSONObject.fromObject--JSON与对象的转换

- 安装JAVA内部错误61003_JDK1.8 安装报内部错误:61003

- python web flask开发框架_Python Web 开发框架,Flask 与 Django那个更好

- html游戏键盘控制,键盘控制方块移动.html

- APA102C全彩色LED控制IC

- 2021年人工神经网络第三次作业-第二题:遗传算法与人工神经网络-参考答案

- 基于Arduino ATmega328人脸识别IOT演示门锁