Virtex-6系列FPGA的CLB

Virtex-6系列FPGA

Virtex-6是Xilinx 在2009年2月推出的新一代旗舰产品,采用了第三代Xilinx ASMBL架构、40nm 工艺,提供多达760000 个逻辑单元,为业界成本最低、功耗最低、密度最高、性能最高、带宽最大的FPGA。该产品在硬内核IP、收发器以及开发工具支持方面做了很大的优化,在追求更高带宽的同时,支持更广泛的通信标准和更高的性能。Virtex-6 具有以下特性。

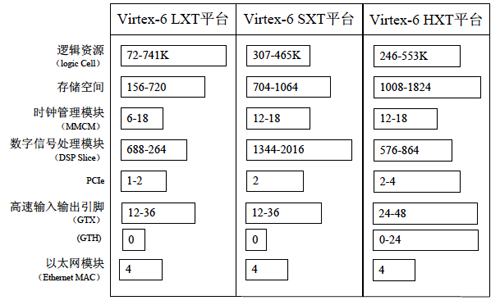

(1) 三个子平台,各平台之间的资源对比关系见图5-1。

LXT 平台:适用于高速串行连接,同时对逻辑资源性能要求比较高的应用。 SXT 平台:适用于高速串行连接,同时对DSP 处理能力要求最高的应用。 HXT 平台:适用于对串行连接带宽要求最高的应用。  图5-1 Virtex-6系列的资源对比

图5-1 Virtex-6系列的资源对比

(2) 子平台间的兼容性。

LXT 与SXT 器件,如果封装相同,则引脚兼容。

(3) 先进的高性能FPGA 逻辑资源。

真正的6 输入LUT 技术。 双LUT5 选项。 LUT/双触发器对。 提高布线效率。 每个LUT 可配置为64 位(或者2 个32 位)分布式LUT RAM。 带寄存器输出的SRL32/双SRL16。 强大的时钟管理模块(MMCM)。

(4) 32kbit BRAM/FIFO,工作频率达600MHz,而且可以拆分成2 个18kbit 以提高BRAM带宽。

(5) 高性能并行SelectIO 技术,支持DDR3。

(6) 先进的25×18 乘累加模块DSP48E1。

(7) 灵活的配置模式,支持SPI、multi-boot 功能。

(8) System Monitor 系统监控功能。

(9) 集成PCIe2.0 硬核,支持Gen1/Gen2,×1/×2/×4/×8 模式,具有endpoint和root port 功能。

(10) GTX 收发器支持150Mbit/s 到6.5Gbit/s 传输速率。

(11) GTH 收发器支持2.488Gbit/s 到超过11Gbit/s 传输速率。

(12) 集成10/100/1000Mbit/s 以太网MAC 模块。

应用GTX 可以支持1000BASE-X PCS/PMA 和SGMII。 应用SelectIO 可以支持MII/GMII/RGMII。 支持2500Mbit/s 传输速率。

(13) 40nm 铜工艺、CMOS 技术。

(14) 1.0V 核电压(-1,-2,-3 速度等级)。

(15) 0.9V 核电压的支持(-1L 速度等级)。

(16) 采用Flop-Chip 封装,具有很高的信号完整性。

Virtex-6 内部模块

本节将详细介绍Virtex-6 系列器件的内部模块,以便读者对Virtex-6系列FPGA内部模块有一个较深入的认识,因为,只有深入了解了FPGA 的内部结构,才能有效地利用它,这可以在很大程度上提高设计者的设计优化能力——用较少的资源,实现较多的功能、较高的性能。

可配置逻辑模块(CLB)

CLB是实现时序电路和组合电路的主要逻辑资源。

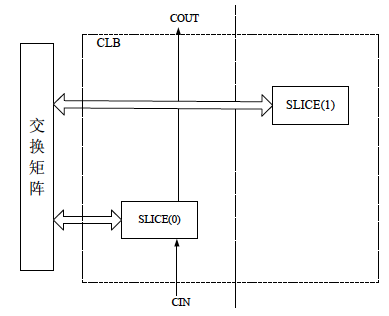

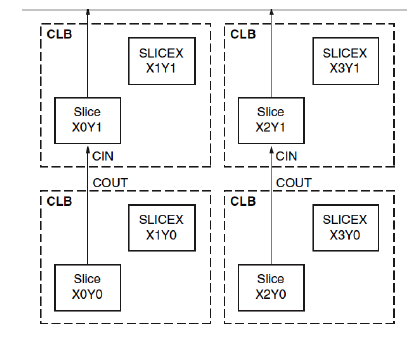

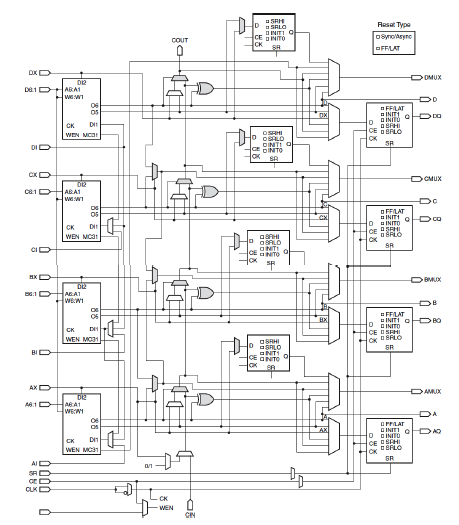

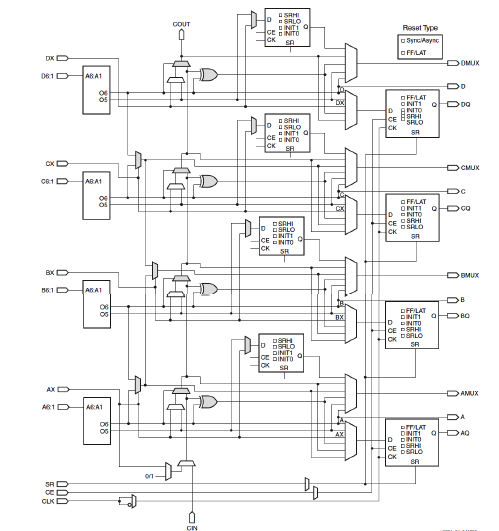

Virtex-6每个CLB模块里包含2个SLICE,每个CLB通过交换矩阵与外部通用逻辑阵列相连,如图5-2和图5-3所示。CLB中的两个SLICE之间没有直接连接。

图5-2 CLB 里的SLICE 排列

图5-2 CLB 里的SLICE 排列  图5-3 CLB 的位置排列

图5-3 CLB 的位置排列

在Virtex-6中,SLICE 分为SLICEX、SLICEL 和SLICEM 三种,SLICEX不具有存储功能,也没有进位链;SLICEL不具有存储功能,但包含进位链;SLICEM 具有存储/移位寄存器功能,也包含进位链。

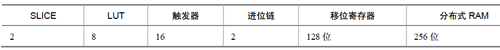

每个SLICE包含4个LUT 和8个存储单元。这些基本单元能提供逻辑、算术和ROM功能。除了这些基本功能,还有一些SLICE具有分布式RAM和移位寄存器功能,这些SLICE又被称为SLICEM。

CLB 可以实现表5-1 所示功能。

表5-1 CLB的功能

表5-1 CLB的功能

SLICE结构图如图5-4(a)和图5-4(b)所示,每个SLICE包含逻辑函数发生器(即LUT)、存储元件、多功能多路复用器(MUXF)、进位逻辑和算法单元(MULT_AND)等资源。

(a)SLICEM

(a)SLICEM  (b)SLICEL 图5-4 SLICE 内部简化结构图

(b)SLICEL 图5-4 SLICE 内部简化结构图

一、 查找表(LUT)

Virtex-6 FPGA的函数发生器由6输入查找表实现。每个LUT有6个独立输入(A1-A6)和2个独立输出(O5 和O6),可以实现任意6 输入布尔函数。同时每个LUT 在相同的输入情况下,也可以实现2 个任意5 输入布尔函数。如果是6 输入函数,仅有O6 输出。

O5 和O6 分别对应两个5 输入函数发生器的输出,在这种情况下,A6 由软件设置为高电平。LUT 的延时与所实现的函数无关。

LUT 可以实现组合逻辑、ROM、分布式RAM、移位寄存器等功能。

(1) 组合逻辑:所有的LUT 可以实现任意6 输入布尔函数。

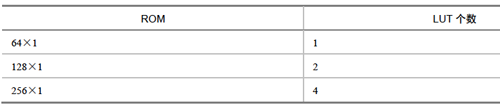

(2) ROM:所有的LUT 可以实现一个64×1 位ROM。有三种配置方式,分别是ROM64×1、ROM128×1 和ROM256×1。SLICEM 和SLICEL 中的ROM 可以级联成更宽或者更深的ROM,配置的表见表5-2。

表5-2 ROM 配置

表5-2 ROM 配置

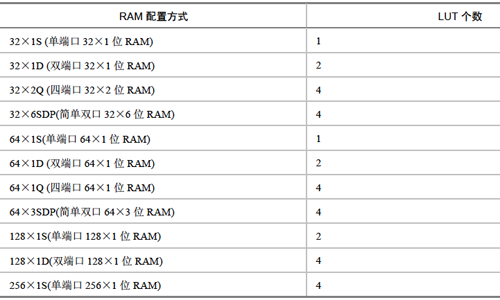

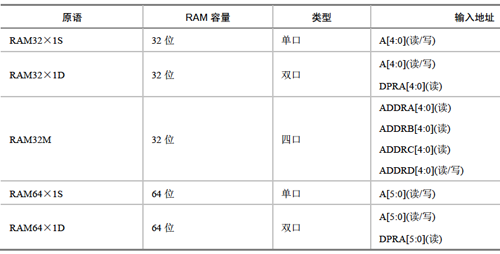

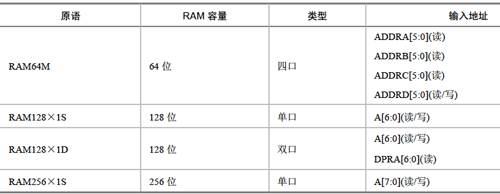

(3) 分布式RAM存储器(只能在SLICEM中使用):SLICEM中的LUT可以配置成一种称为分布式RAM的同步RAM。SLICEM中的多个LUT可以灵活组合起来,以存储更多数据。在SLICEM内可以将RAM元件配置成以下形式,RAM的配置见表5-3。

表5-3 分布式RAM的配置表

表5-3 分布式RAM的配置表

分布式RAM原语如表5-4所示。

表5-4 单口、双口和四口的分布式RAM的原语

表5-4 单口、双口和四口的分布式RAM的原语

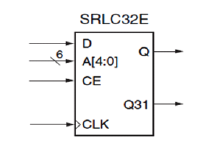

(4) 移位寄存器(只能在SLICEM中使用):SLICEM的LUT还可配置成32位移位寄存器,无需使用SLICE中提供的触发器。以这种方法使用的LUT可以将串行数据延迟1到32个时钟周期之间的任意长度。移位寄存器的移位输入SHIFTIN和移位输出SHITOUT用来将LUT级联成更大的移位寄存器,一个CLB里面的4个LUT可以级联,产生128个时钟周期的延时。CLB之间也可以连接组成移位寄存器,用于平衡数据流水线的时序。移位寄存器原语如图5-5所示。

图5-5 移位寄存器的原语

图5-5 移位寄存器的原语

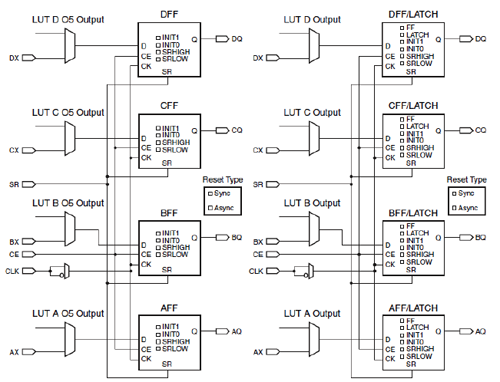

二、 存储元件

Virtex-6每个SLICE都有存储元件,可以实现存储功能,可以配置成边沿触发式的D型触发器或电平敏感型的锁存器,如图5-6所示。

图5-6 SLICE里寄存器/锁存器配置

图5-6 SLICE里寄存器/锁存器配置

三、 多路复用器(MUX)

在一个SLICE中,除了包含LUT外,还包含三个多路复用器(F7AMUX、F7BMUX和F8MUX),用户可以将4个函数发生器组合在一起,构成7输入或者8输入的函数。多于8个输入的函数,可以用多个SLICE实现。

多路复用器F7AMUX、F7BMUX和F8MUX通常和函数发生器或者片上逻辑一起实现多种多路复用器。可以实现以下几种多路复用器。

1个LUT实现4:1多路复用器 2个LUT实现8:1多路复用器 4个LUT实现16:1多路复用器

四、 快速先行进位逻辑(Carry Logic)

Virtex-6每个CLB有2条独立的进位链,用于实现快速算术加减运算,它解决了多位宽加法、乘法从最低位向最高位进位的延时问题。先行进位逻辑有专用的进位通路和进位多路复用器(MUXCY),可用来级联函数发生器(LUT),以实现更宽更复杂的逻辑函数,提高CLB模块的处理速度。Virtex6中的进位链是上行进位链,每个SLICE具有4位的高度。考虑到进位链的上行结构特点,在设计中,要特别注意进位链的长度,因为如果当进位链的长度超出一列时,进位链会导致延时变长很多,影响时序。

五、 算术逻辑(MULT_AND)

算术逻辑包括一个异或门(XOR)和一个专用与门(MULT_AND),一个异或门可以使一个SLICE实现2位全加操作,专用与门提高乘法器的效率。

Virtex-6系列FPGA的CLB相关推荐

- Xilinx 7系列FPGA中CLB结构和内部资源使用

Xilinx 7系列FPGA中CLB结构和内部资源使用 7系列FPGA内部资源更加的更富,性能更强悍,最吸引人的就是28nm工艺使得相同的逻辑资源功耗降低50%,这是一个很大的提升,在单板硬件上仅仅降 ...

- Xilinx-7系列FPGA架构—— CLB

xilinx7系列FPGA主要包括:Spartan®-7/Artix®-7/Kintex®-7/Virtex®-7.其性能/密度/价格也随着系列的不同而提升.其中以Virtex-7有着极高的系统性能和 ...

- 1.4 7系列FPGA IOB

7系列FPGA IOB 1 7系列FPGA IOB 2 IOB的约束方法 3 IOB约束使用注意事项 1 7系列FPGA IOB CLB可以实现FPGA的功能,但要和外界打交道,就必须有和外 界电平兼 ...

- Xilinx 7系列FPGA之Virtex-7产品简介

Xilinx Virtex-7 系列FPGA:高密度.低功耗的28nm技术带来的性能革新 挑战:难以满足的带宽需求 为下一代网络实施高级串行连接标准 提高数据处理性能 让产品更快上市 满足受限的功率预 ...

- FPGA - 7系列 FPGA内部结构之CLB -01- CLB资源概述

前言 本文节选UG474进行整理翻译,用于对CLB进行简单介绍,同时简单介绍了下针对逻辑资源设计的推荐流程. CLB简介 7 系列可配置逻辑块 (CLB) 提供先进的高性能 FPGA 逻辑: 真6 输 ...

- Xilinx 7系列 FPGA CLB资源介绍

赛灵思 7系列 FPGA CLB资源介绍 ---主要来源于官方技术手册ug474_7Series_CLB.pdf FPGA共有6大组成部分:1.可编程输入输出I/O单元:2.基本可编程逻辑单元CLB: ...

- Xilinx 7系列FPGA介绍

2015年11月,Xilinx推出Spartan®-7 FPGA系列 赛灵思公司今天宣布为成本敏感型应用推出灵活的 I/O 密集型器件--Spartan®-7 FPGA系列.该新型系列器件可满足汽车. ...

- 7系列FPGA数据手册:概述------中文翻译版

7系列FPGA数据手册:概述------中文翻译版 总体介绍 7系列FPGA功能摘要 Spartan-7系列FPGA功能摘要 Artix-7系列FPGA功能摘要 Kintex-7系列FPGA功能摘要 ...

- 从底层结构开始学习FPGA----Xilinx 7 系列 FPGA 的逻辑优势

文章目录 摘要 介绍 7系列 FPGA 中的Slice架构 常见的Slice资源用法 控制信号 额外资源的好处 结论 本文主要翻译自<WP405----Xilinx 7 Series FPGAs ...

最新文章

- 这段Python代码让程序员赚300W,公司已确认!网友:神操作!

- Challenges(分组、聚合、连接)

- Spring 详解(四):Spring MVC

- 孙宏斌谈贾跃亭哽咽:“我一定把乐视做成一个好公司”

- html文件本质上是一个,html文件是什么

- button标签设置隐藏和显示_离职后我隐藏一张工作表,老板找了一天没找到

- Delphi第三方组件安装DCU.PAS.DPK.BPL.ActiveX控件

- oracle sequrnce_Oracle Sqlldr简单用法

- go语言 doc转换html,go语言使用wkhtmltopdf工具将html转成pdf

- SQL Server 索引结构及其使用(四)

- 如何让自己的email地址永久有效

- matlab ocx控件,matlabr.ocx控件下载

- 证件阅读设备一般可以识别哪些证件

- 【渝粤教育】电大中专电商运营实操 (2)_1作业 题库

- c语言用if函数如何判断闰年,excel怎么用IF公式判断闰?

- PHOTOSHOP超强磨皮大法 将斑点选出来

- 采用以太坊智能合约技术的报名系统源码

- Android 以图找图功能

- Python 实战之 什么是量化交易?它与python之间的关系

- 数据库SQL:数据更新