【 FPGA 】使用状态机设计一个ADC采样控制电路

以ADC0809为例,设计一个ADC采样控制电路,采用有限状态机的方式。

传统的ADC采样控制的方法是用单片机控制,单片机控制ADC采样具有编程简单,控制灵活的优点,但是采样速度慢,CPU控制的低速极大地限制了ADC器件告诉性能的发挥,在高速ADC控制中,目前基本上都是使用可编程逻辑器件来完成。

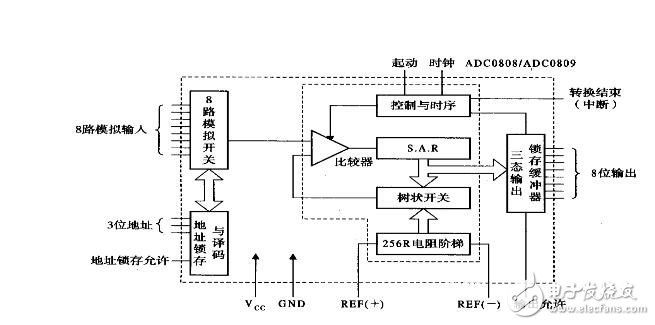

下面是ADC0809的内部电路图:

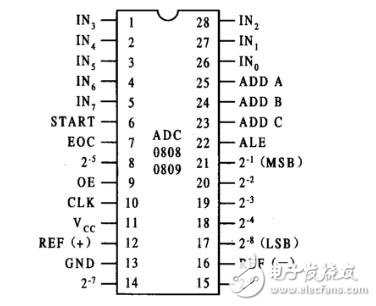

引脚图:

引脚功能:

IN0~IN7:8路模拟量输入端。

D0~D7:8位数字量输出端。

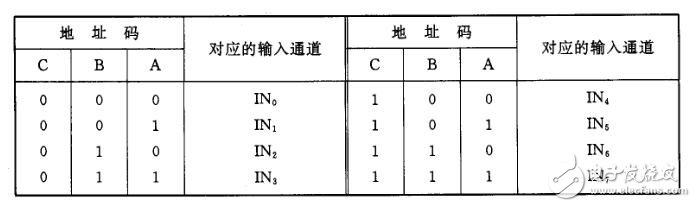

ADDA、ADDB、ADDC:3位地址输入线,用于选择8路模拟通道中的一路,选择情况见表。

ALE:地址锁存允许信号,输入,高电平有效。

START:A/D转换启动信号,输入,高电平有效。

EOC:A/D转换结束信号,输出。当启动转换时,该引脚为低电平,当A/D转换结束时,该线脚输出高电平。

OE:数据输出允许信号,输入,高电平有效。当转换结束后,如果从该引脚输入高电平,则打开输出三态门,输出锁存器的数 据从D0~D7送出。

CLK:时钟脉冲输入端。要求时钟频率不高于640KHZ. REF+、REF-:基准电压输入端。

Vcc:电源,接+5V电源。

GND:地。

地址码与输入通道的对应关系:

时序图:

工作过程:

1.输入3位地址,并使 ALE=1,将地址存入地址锁存器中,经地址译码器译码从8路模拟通道中选通一路模拟量送到比较器。

2.送START一高脉冲,START的上升沿使逐次逼近寄存器复位,下降沿启动A/D转换,并使EOC信号为低电平,转换时间为100us。

3.当转换结束时,EOC信号回到高电平,控制器可以根据此信号了解转换状态。

4.此后,控制器可以通过控制输出使能端OE,通过八位并行数据总线D[7:0]来读取转换结果。

抽象出状态转移图:

分为四个状态,分别为初始化状态s0,启动ADC状态s1,等待ADC转换结束状态s2,转换数据读取状态s3.

ADC0809控制的状态从s0到s1,s1到s2,s3到s0都是在时钟上升沿直接变化,只有s2到s3,根据输入信号EOC来判断状态转移的下一个状态。

下面给出状态机的简图,由于输出较多,下图没有列出输出,具体见代码:

Verilog HDL描述代码为:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2019/01/04 22:30:51

// Design Name:

// Module Name: adc0809

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module adc0809(input clk,input reset, input eoc, //转换结束标志信号output reg start, //ADC转换启动信号output [2:0] addr,//ADC输入通道选择地址output reg ale, //模拟通道地址锁存信号output reg oe //ADC数据输出使能);localparam [1:0]s0 = 2'b00,s1 = 2'b01,s2 = 2'b10,s3 = 2'b11;reg [1:0] current_state, next_state;always @(posedge clk, posedge reset)beginif(reset)current_state <= s0;elsecurrent_state <= next_state;endassign addr = 3'b000; //输入通道设定为通道0always @ *begincase(current_state)s0: next_state = s1;s1: next_state = s2;s2:beginif(eoc) next_state = s3; //转换结束else next_state = s2; //转换未结束,继续等待ends3: next_state = s0;endcaseendalways @ *begincase(current_state)s0:beginale = 0; start = 0; oe = 0;ends1:beginale = 1; start = 1; oe = 0;ends2:beginale = 0; start = 0; oe = 0;ends3:beginale = 0; start = 0; oe = 1;endendcaseendendmodule

RTL电路:

暂时就到这里,可能有的考虑不周,有意见尽管提出,我也会持续更新。

参考文献:电子发烧友

百度百科

搭建你的数字积木

【 FPGA 】使用状态机设计一个ADC采样控制电路相关推荐

- 解读ADC采样芯片(EV10AQ190A)的工作模式(四通道模式)

上篇博文讲了EV10AQ190A这种ADC芯片的工作模式:双通道模式 我十分重视这些内容,因为这是我认识硬件工作模式的起点,当然这也只是理论上的内容,实际采样过程中也许会遇到这样那样的问题,那就需要自 ...

- STM32多通道ADC采样获取MCP9701模拟温度传感器温度输出数据

STM32多通道ADC采样获取MCP9701模拟温度传感器温度输出数据 市面上常见的模拟温度传感器有TI的LM35系列,然后使用中并不简便.MCP9701是Microchip公司推出的相似的模拟温度传 ...

- ev10aq190a采集电路图_解读ADC采样芯片(EV10AQ190A)的工作模式(四通道模式)

上篇博文讲了EV10AQ190A这种ADC芯片的工作模式:双通道模式 我十分重视这些内容,因为这是我认识硬件工作模式的起点,当然这也只是理论上的内容,实际采样过程中也许会遇到这样那样的问题,那就需要自 ...

- HDLBits 系列(15) 如何设计一个双边沿采样的电路?

目录 背景 原题复现 审题 我的设计1 我的设计2 背景 曾经专门写过这个话题,可是今天在练习HDLBits时候,又发现了这个问题,但是以前的思路我已经忘了,不得不回顾. FPGA中如何实现双边沿采样 ...

- FPGA 状态机设计

数字系统有两大类有限状态机(Finite State Machine,FSM):Moore状态机和Mealy状态机. Moore状态机 其最大特点是输出只由当前状态确定,与输入无关.Moore状态机的 ...

- 在matlab中实现累乘,如何利用matlab设计一个线性相位FIR带通滤波器,并在FPGA上实现...

设计要求 利用matlab设计一个线性相位FIR带通滤波器,并在FPGA上实现. 1.滤波器指标:过渡带带宽分别为100~300HZ,500~700HZ,阻带允许误差为0.02,通带允许误差为0.01 ...

- (32)FPGA米勒型状态机设计(三段式)(第7天)

(32)FPGA米勒型状态机设计(三段式)(第7天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA米勒型状态机设计(三段式)(第7天) 5)技术交流 6 ...

- (31)FPGA米勒型状态机设计(二段式)(第7天)

(31)FPGA米勒型状态机设计(二段式)(第7天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA米勒型状态机设计(二段式)(第7天) 5)技术交流 6 ...

- (30)FPGA米勒型状态机设计(一段式)(第6天)

(30)FPGA米勒型状态机设计(一段式)(第6天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA米勒型状态机设计(一段式)(第6天) 5)技术交流 6 ...

最新文章

- 如何利用客户端在CU发博客

- 点标记 高德地图_打尽渣男渣女的查岗神器?高德家人地图实测

- 反射+javacsv+scv文件构建资源获取

- linux的基础知识——信号的概念

- idea搭建maven项目关于数据库连接jar包版本问题解决方案

- Moment.js常见用法总结 1

- 央企如何做好数字化转型战略规划

- PMP考试一定要大量做题吗?

- 简述冯诺依曼计算机体系结构

- Android多国语言的国家代码

- 测试网速和网站加载的速度 - Speedtest by Ookla

- 大数据产品价值主张_大数据对商业模式创新的影响

- 蚁群优化算法之精华蚂蚁系统和排列蚂蚁系统学习笔记

- vue+croppr.js 裁剪圆形图片

- 图的遍历 --- 广度优先搜索【借助队列实现】 + 深度优先搜索【借助递归栈】

- Naive Bayes

- python解压7z压缩包_python使用7z解压软件备份文件脚本分享

- 学习使用iptables

- 【小程序】腾讯云服务配置小程序流程

- 宽带连接常见错误 解决