FPGA开发基本流程

转自:https://www.cnblogs.com/synow/p/5498654.html

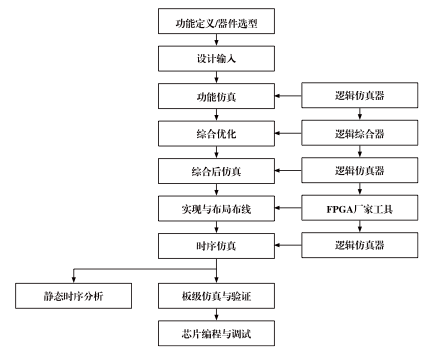

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。典型FPGA的开发流程一般如图1所示,包括功能定义/器件选型、设计输入、功能仿真、综合优化、综合后仿真、实现、布线后仿真、板级仿真以及芯片编程与调试等主要步骤。

图1 FPGA典型设计流程

1、功能定义/器件选型

在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型。 一般都采用自顶向下的设计方法,把系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接使用EDA元件库为止。

2、 设计输入

设计输入是将所设计的系统或电路以开发软件要求的某种形式表示出来,并输入给EDA工具的过程。常用的方法有硬件描述语言(HDL)和原理图输入方法等。原理图输入方式是一种最直接的描述方式,在可编程芯片发展的早期应用比较广泛,它将所需的器件从元件库中调出来,画出原理图。这种方法虽然直观并易于仿真,但效率很低,且不易维护,不利于模块构造和重用。更主要的缺点是可移植性差,当芯片升级后,所有的原理图都需要作一定的改动。目前,在实际开发中应用最广的就是HDL语言输入法,利用文本描述设计,可以分为普通HDL和行为HDL。普通HDL有ABEL、CUR等,支持逻辑方程、真值表和状态机等表达方式,主要用于简单的小型设计。而在中大型工程中,主要使用行为HDL,其主流语言是Verilog HDL和VHDL。这两种语言都是美国电气与电子工程师协会(IEEE)的标准,其共同的突出特点有:语言与芯片工艺无关,利于自顶向下设计,便于模块的划分与移植,可移植性好,具有很强的逻辑描述和仿真功能,而且输入效率很高。 除了这IEEE标准语言外,还有厂商自己的语言。也可以用HDL为主,原理图为辅的混合设计方式,以发挥两者的各自特色。

3、 功能仿真

功能仿真也称为前仿真是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有延迟信息,仅对初步的功能进行检测。仿真前,要先利用波形编辑器和HDL等建立波形文件和测试向量(即将所关心的输入信号组合成序列),仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用的工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS和Cadence公司的NC-Verilog以及NC-VHDL等软件。

4、 综合优化

所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。就目前的层次来看,综合优化(Synthesis)是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。为了能转换成标准的门级结构网表,HDL程序的编写必须符合特定综合器所要求的风格。由于门级结构、RTL级的HDL程序的综合是很成熟的技术,所有的综合器都可以支持到这一级别的综合。常用的综合工具有Synplicity公司的Synplify/Synplify Pro软件以及各个FPGA厂家自己推出的综合开发工具。

5、 综合后仿真

综合后仿真检查综合结果是否和原设计一致。在仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去,可估计门延时带来的影响。但这一步骤不能估计线延时,因此和布线后的实际情况还有一定的差距,并不十分准确。目前的综合工具较为成熟,对于一般的设计可以省略这一步,但如果在布局布线后发现电路结构和设计意图不符,则需要回溯到综合后仿真来确认问题之所在。在功能仿真中介绍的软件工具一般都支持综合后仿真。

6、 实现与布局布线

布局布线可理解为利用实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件(如配置文件与相关报告),实现是将综合生成的逻辑网表配置到具体的FPGA芯片上,布局布线是其中最重要的过程。布局将逻辑网表中的硬件原语和底层单元合理地配置到芯片内部的固有硬件结构上,并且往往需要在速度最优和面积最优之间作出选择。布线根据布局的拓扑结构,利用芯片内部的各种连线资源,合理正确地连接各个元件。目前,FPGA的结构非常复杂,特别是在有时序约束条件时,需要利用时序驱动的引擎进行布局布线。布线结束后,软件工具会自动生成报告,提供有关设计中各部分资源的使用情况。由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

7、 时序仿真

时序仿真,也称为后仿真,是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规(即不满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等)现象。时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。由于不同芯片的内部延时不一样,不同的布局布线方案也给延时带来不同的影响。因此在布局布线后,通过对系统和各个模块进行时序仿真,分析其时序关系,估计系统性能,以及检查和消除竞争冒险是非常有必要的。在功能仿真中介绍的软件工具一般都支持综合后仿真。

8、 板级仿真与验证

板级仿真主要应用于高速电路设计中,对高速系统的信号完整性、电磁干扰等特征进行分析,一般都以第三方工具进行仿真和验证。

9、 芯片编程与调试

设计的最后一步就是芯片编程与调试。芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generation),然后将编程数据下载到FPGA芯片中。其中,芯片编程需要满足一定的条件,如编程电压、编程时序和编程算法等方面。逻辑分析仪(Logic Analyzer,LA)是FPGA设计的主要调试工具,但需要引出大量的测试管脚,且LA价格昂贵。目前,主流的FPGA芯片生产商都提供了内嵌的在线逻辑分析仪(如Xilinx ISE中的ChipScope、Altera QuartusII中的SignalTapII以及SignalProb)来解决上述矛盾,它们只需要占用芯片少量的逻辑资源,具有很高的实用价值。

补充:基于FPGA的SOC设计方法

目前,由于FPGA性能提升价格下降,同时嵌入越来越多内核,很自然地,很多IC设计公司将FPGA用于ASIC原型验证,把FPGA可编程的优点带到了SOC领域,其系统由嵌入式处理器内核、DSP单元、大容量处理器、吉比特收发器、混合逻辑、IP 以及原有的设计部分组成。

SOC 平台的核心部分是内嵌的处理内核,其硬件是固定的,软件则是可编程的;外围电路则由FPGA的逻辑资源组成,大都以IP 的形式提供,例如存储器接口、USB接口以及以太网MAC层接口等,用户根据自己需要在内核总线上添加,并能自己订制相应的接口IP 和外围设备。

FPGA开发基本流程相关推荐

- 【FPGA-F3】阿里云FAAS平台,极大简化FPGA开发部署流程

摘要: 阿里FPGA云服务器平台FaaS(FPGA as a Service)在云端提供统一硬件平台与中间件,可大大降低加速器的开发与部署成本.普惠开发者 FPGA (现场可编程门阵列)由于其硬件并行 ...

- FPGA开发基本流程详解

FPGA是一种可编程逻辑器件,与传统的硬连线电路不同,它具有高度的可编程性和灵活性.FPGA的设计方法包括硬件设计和软件设计两部分,硬件设计包括FPGA芯片电路.存储器.输入输出接口电路等等,软件设计 ...

- DE1-SoC笔记(二)—SoC FPGA开发设计流程总结(de1教程2.1节)

文章目录 1.所需要的软件 1.1 硬件设计部分 1.2 软件设计部分 1.3 putty 2.各软件的作用 3.SoC FPGA设计流程 3.1.用Qsys构建Hardware系统 3.2.生成Pr ...

- Xilinx FPGA开发基本流程

目录 一.创建工程 二.添加源文件 三.RTL描述与分析 一.创建工程 双击Vivado图标,进入到Vivado启动界面,如图所示: 在上述界面中有三个分栏,即:Quick Start.Tasks.L ...

- FPGA开发流程(详述每一环节的物理含义和实现目标)

<div class="htmledit_views"> 需求说明:Verilog设计 内容 :FPGA开发基本流程及注意事项 来自 :时间的诗 ...

- FPGA的设计艺术(8)最佳的FPGA开发实践之严格遵循过程

文章目录 前言 如何花费更少的时间去调试? 为什么使用过程? 需要多少过程? 最小的过程 明确需求 数字设计方案 逻辑设计 功能仿真 板上验证 版本控制 编码指南:简短的技术组合,可最大程度地减少错误 ...

- FPGA开发第一弹:Vivado软件安装、开发使用与工程建立

FPGA开发第一弹:Vivado软件安装.开发使用与工程建立 文章目录 FPGA开发第一弹:Vivado软件安装.开发使用与工程建立 软件安装 工程建立(软件使用) 新建工程 设计输入 功能仿真 创建 ...

- FPGA的设计艺术(2)FPGA开发流程

前言 注:本文首发易百纳技术社区,文章链接:FPGA的设计艺术(2)FPGA开发流程 本文介绍整个FPGA设计流程以及设计FPGA所需的各个步骤-从一开始到可以将设计下载到FPGA的阶段.但是在此之前 ...

- (78)FPGA内部资源与FPGA开发流程-面试必问(二)(第16天)

(78)FPGA内部资源与FPGA开发流程-面试必问(二)(第16天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA内部资源与FPGA开发流程-面试必问 ...

最新文章

- 箱线图怎么判断异常值_原创【六西格玛工具解读】02——箱线图(Boxplot)

- 使用MSBuild实现完整daily build流程 .

- TemplateSyntaxError at XXXX或页面样式未生效

- 65 SD配置-交货凭证配置-定义相关项目类别的拣配相关

- ApacheCN 数据科学译文集 20210313 更新

- Amazon WorkSpaces现支持Amazon Linux 2 Desktop

- excel : 如何快速跳到某一行

- 《机器学习实战》原书数据与代码(基于Python3)汇总

- VC++ 求绝对值函数

- vb红绿灯自动切换_vb教程之用VB编写“红绿灯”程序

- FFMPEG实现RTSP中H264数据流解码 并且实时播放

- 容器化 RDS:借助火焰图定位Kubernetes性能问题

- JsDroid2开发教程

- 详解高速缓存存储器的3种映射方式

- 经典Java练习题 Mars Rover

- Titan XP值不值?一文教你如何挑选深度学习GPU

- Congestion 问题怎么解决?

- 基于Zookeeper的分布式锁

- 微信小程序开发:腾讯地图集成详细步骤

- 亚商投资顾问 早餐FM/0928 养老金抵扣个税优惠来了