开发自定义AXI总线外设IP核——以LED和开关为例

http://www.eefocus.com/nightseas/blog/12-10/287343_15762.html

ZedBoard学习手记(二) 开发自定义AXI总线外设IP核——以LED和开关为例

想要发挥ZYNQ芯片的特长,让整个系统协同工作起来,就需要将PS与PL两部分结合在一起,在Cortex-A9核和FPGA逻辑资源之间建立通信的通道,这条通道就是AXI总线。ZedBoard推出的官方例子中已经介绍了如何将Xilinx做好的AXI总线IP(如AXI_Timer、AXI_GPIO等)添加到工程中,而下面就让我们一起来自己编写一个简单的AXI总线设备——读取板上的8个Swtich状态,并控制8个LED的开关。

有人会问我不了解AXI总线啊怎么办,无须担心,Xilinx已经为我们设计了建立向导,可以自动生成一个设备模板,即使不了解AXI协议,也可以轻松完成设计工作。

首先通过PlanAhead建立一个系统工程,导入ZedBoard的xml文件:zedboard_RevC_v2.xml。这步操作还不清楚的童鞋请在ZedBoard官网上下载ZedBoard_CTT_v14.1资料并跟随该文档进行扫盲。这个资料很详细,也是Step By Step的,可以帮助完成基本的操作学习。

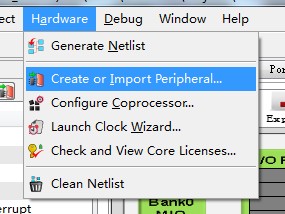

工程建好后,进入XPS界面,选择Hardware→Create or Import Peripheral,开始创建外设。

(看不清图的话可以点击小图放大,下同)

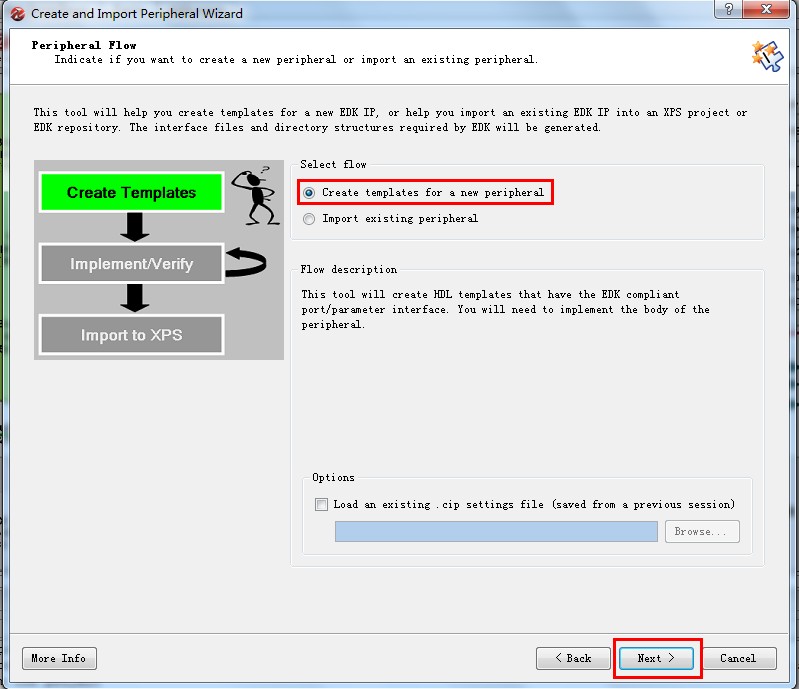

在弹出的窗口中选择新建模板,建立一个外设。

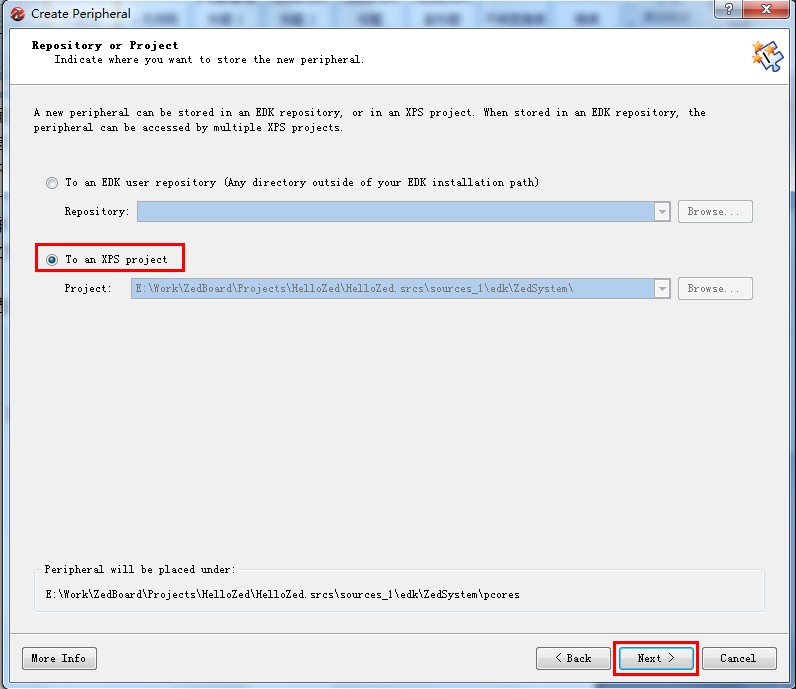

Next后选择集成到XPS系统中,这样新建的外设就会保存在edk目录下的pcores文件夹中。

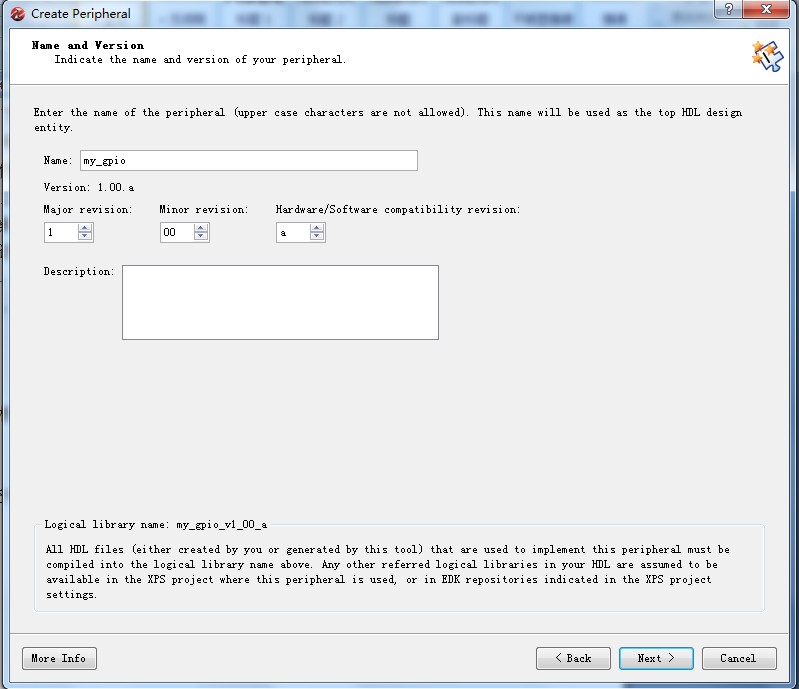

接着Next,为自己的IP起个名字,这里叫my_gpio,全称就是my_gpio_v1_00_a了,注意这里的名字不能用大写字母。

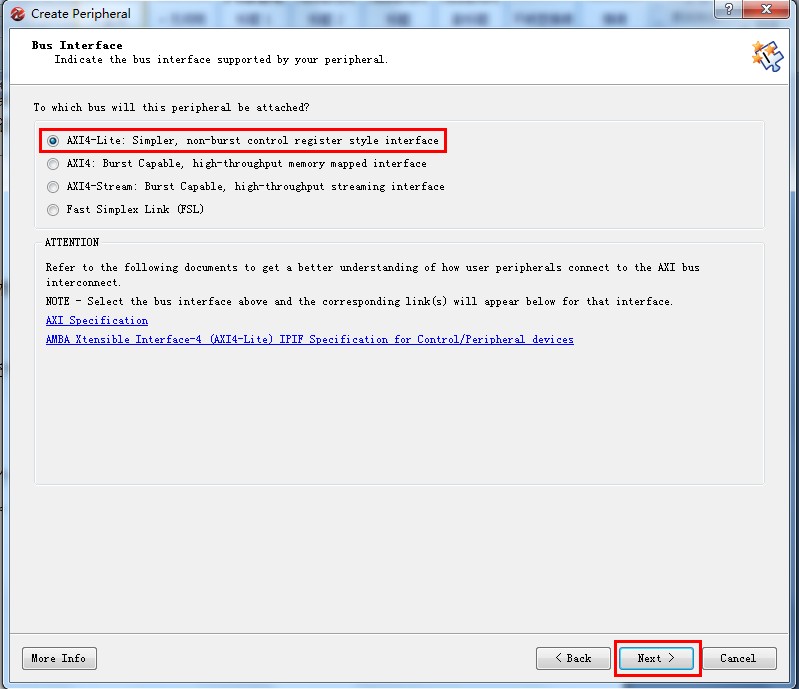

之后选择总线的类型,可以看出这里提供了几个AXI总线设备的变种形势,可以使设备具备猝发操作及大量数据传输的能力,这里我们选AXI4-Lite形式,也就是最简单的类型。

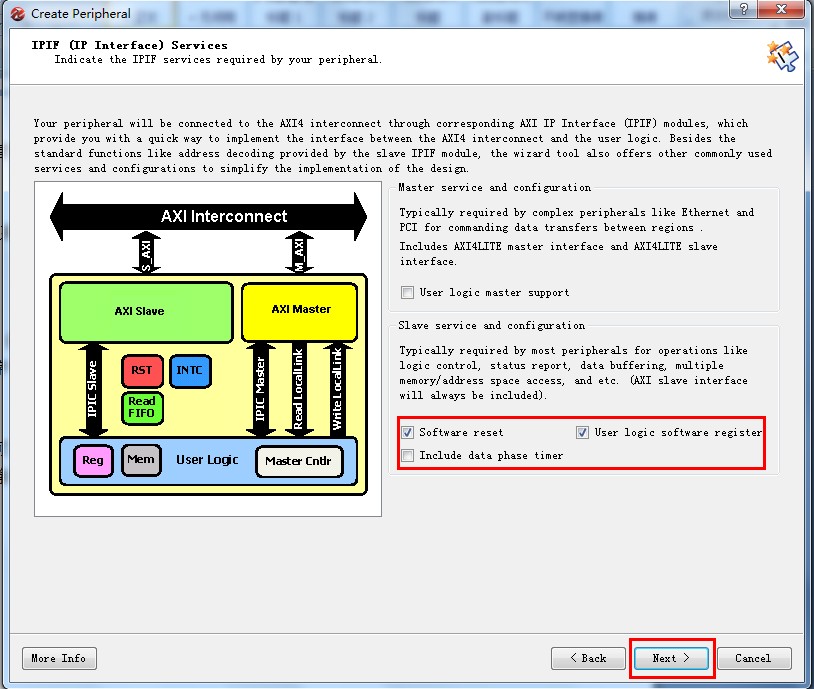

下一步进行几个可选项配置,包括软件复位、主从模式等,勾选中间两项即可,虽然现在用不到软件复位。

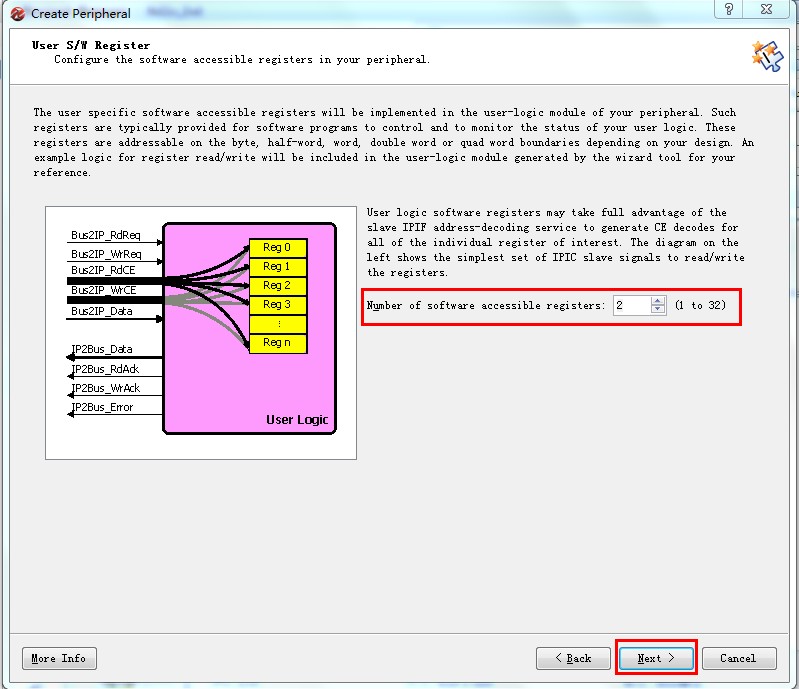

设置寄存器数量,这里我们设置两个32位寄存器(实际使用低8位,其它部分Not Care),一个用来控制LED,另一个用来读取SW状态。

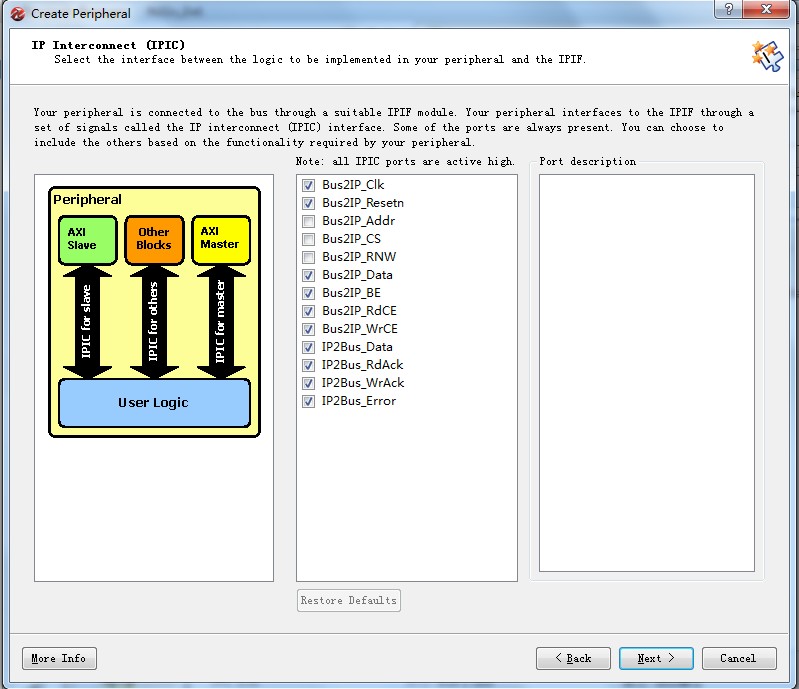

选择需要的IP连接信号,这些是与用户逻辑对接的信号,保持默认即可。

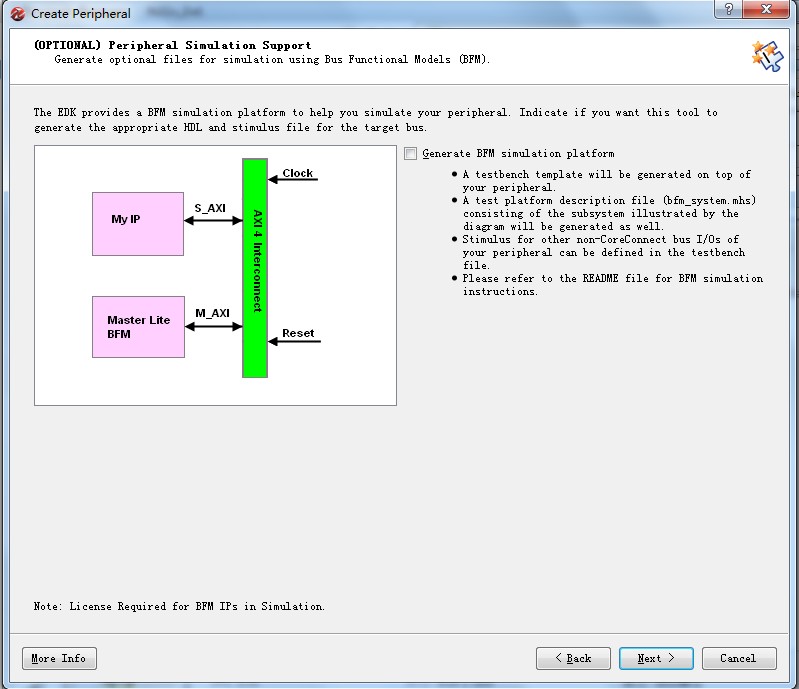

这一步可以建立一个总线上的仿真设备,不需要,直接Next。

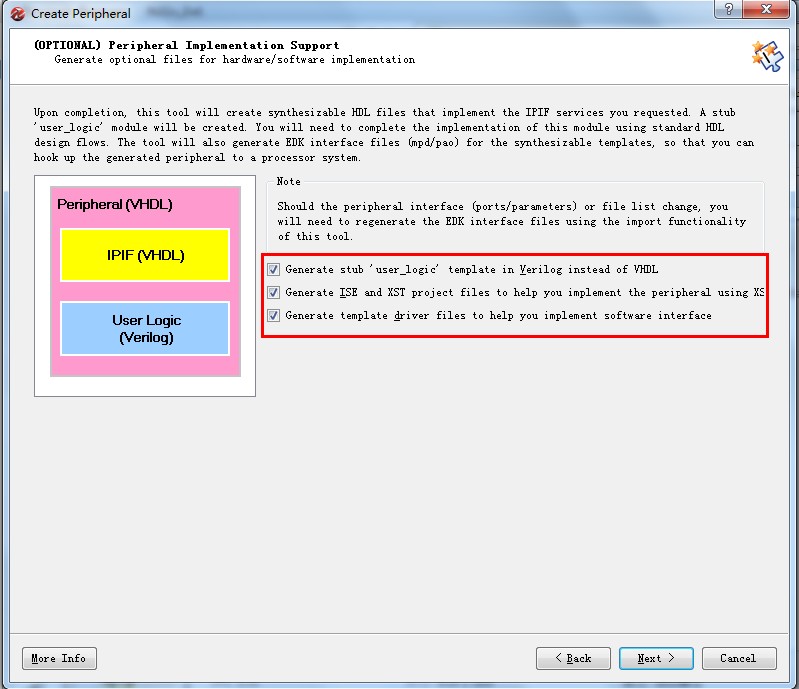

来到另一个配置画面,第一个选项是使用Verilog来设计用户逻辑;第二个选项建立一个ISE的工程文件,方面写代码;第三个选项让XPS自动生成底层的控制代码。

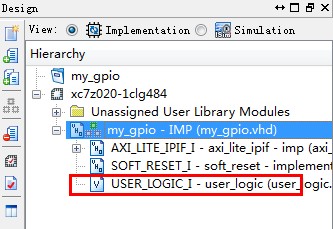

设置结束以后,在XPS的工程目录下就能找到IP的文件夹了,兔子这里的路径是” .\Hello_Zed.srcs\sources_1\edk\module_1\pcores\my_gpio_v1_00_a”。里面有三个文件夹,hdl文件夹包含了user_logic.v和my_gpio.vhd。前者就是我们要修改的用户逻辑文件,后者则是用来连接AXI与用户逻辑,并封装IP核的VHDL文件。这个文件只能是VHDL的,所以像兔子这样只会Verilog的就很苦闷了,还好里面的内容很简单,看一下就能明白。在devl\projnav文件夹下可以找到刚生成的ISE工程,用Project Navigator打开my_gpio.xise,这样就可以开始编辑user_logic了。

user_logic中除了一些定义和信号连接以外,就是两个always块,第一个实现AXI总线向用户寄存器写入数据,第二个则是总线从寄存器中读取数据。需要注意的是,这里的AXI总线已经通过Xilinx的AXI Lite IP Interface进行了中转,到用户这里就变成了非常简单的读写逻辑。

为了控制板上的硬件,我们定义两组信号和相应的寄存器:SW_In信号连接8个Switch,LED_Out连接8个LED。

input [7:0] SW_In;

output [7:0] LED_Out;

在这里,规定寄存器0为Swtich状态寄存器,寄存器1为LED控制寄存器。添加一个always块,使写入寄存器1的数据在LED_Out上更新。

always @( posedge Bus2IP_Clk )

begin

if ( Bus2IP_Resetn == 1'b0 )

begin

LED_Out <= 0;

end

else begin

LED_Out[7:0] <= slv_reg1[7:0];

end

end // LED_OUTPUT_PROC

同时添加逻辑让Switch的状态通过简单的同步(不是去抖啊)写入寄存器0。

// implement slave model register read mux

always @( slv_reg_read_sel or slv_reg0 or slv_reg1 )

begin

case ( slv_reg_read_sel )

2'b10 : slv_ip2bus_data <= slv_reg0;

2'b01 : slv_ip2bus_data <= slv_reg1;

default : slv_ip2bus_data <= 0;

endcase

end // SLAVE_REG_READ_PROC

always @( posedge Bus2IP_Clk )

begin

if ( Bus2IP_Resetn == 1'b0 )

begin

SW_Reg0 <= 0;

SW_Reg1 <= 0;

slv_reg0 <= 0;

end

else begin

SW_Reg0 <= SW_In;

SW_Reg1 <= SW_Reg0;

slv_reg0[7:0] <= SW_Reg1[7:0];

end

end // SWTICH_INPUT_PROC

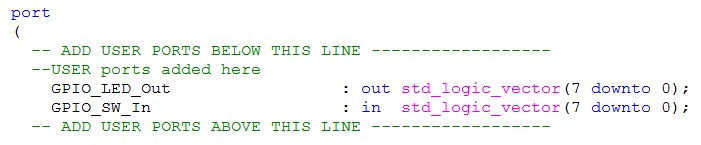

之后还要修改读写逻辑,将case ( slv_reg_write_sel )下的2'b10项注释掉,令寄存器0只读(对写入的数据Not Care),寄存器1则可以读写。如此,我们的用户逻辑就完成了,简单吧。别忘了还要在my_gpio.vhd中为用户逻辑添加端口,两组信号在整个IP的对外接口中分别命名为GPIO_LED_Out和GPIO_SW_In。

具体的代码内容在此:

my_gpio_hdl.rar

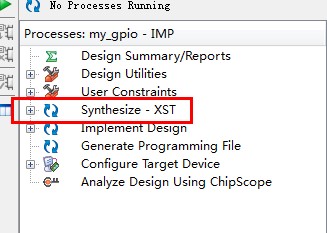

双击Synthesize,检查一下有没有问题,没问题的话就可以关掉Project Navigatorl 。

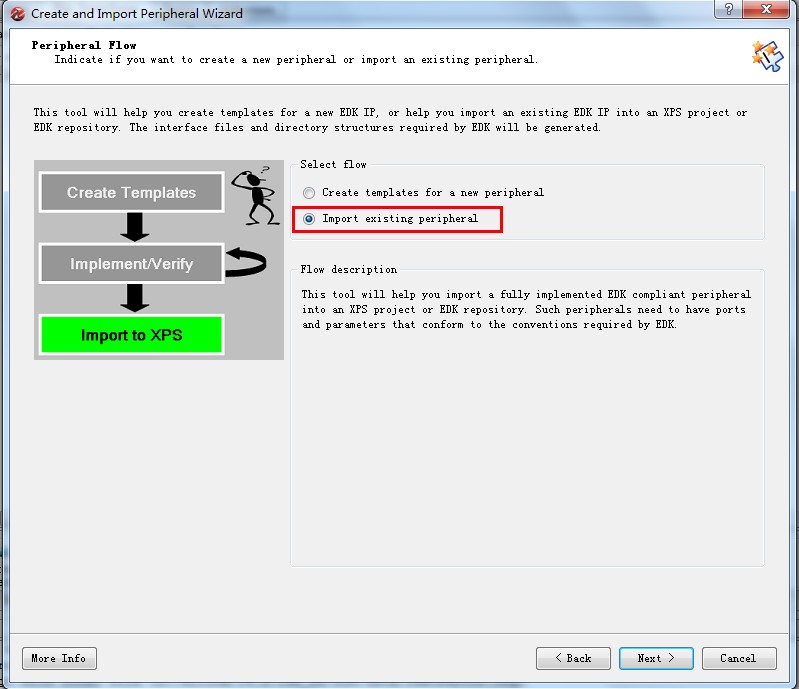

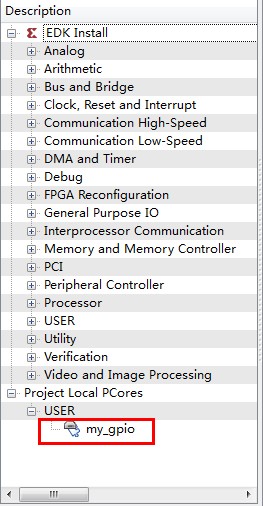

回到XPS界面,我们的自定义IP已经在列表中了,但是这个时候将IP添加到工程中,刚才进行的编辑并不生效,GPIO端口并没有显示在IP核的框图中,这点兔子没有搞明白是为什么,可能要手动修改MPD文件吧。于是我选择将这个IP再添加一次(不得已而为之,有什么好办法望不吝赐教),还是刚才的方法,只不过这回选择导入已有的外设,这种方法也可以用于导入其他已有的IP核。

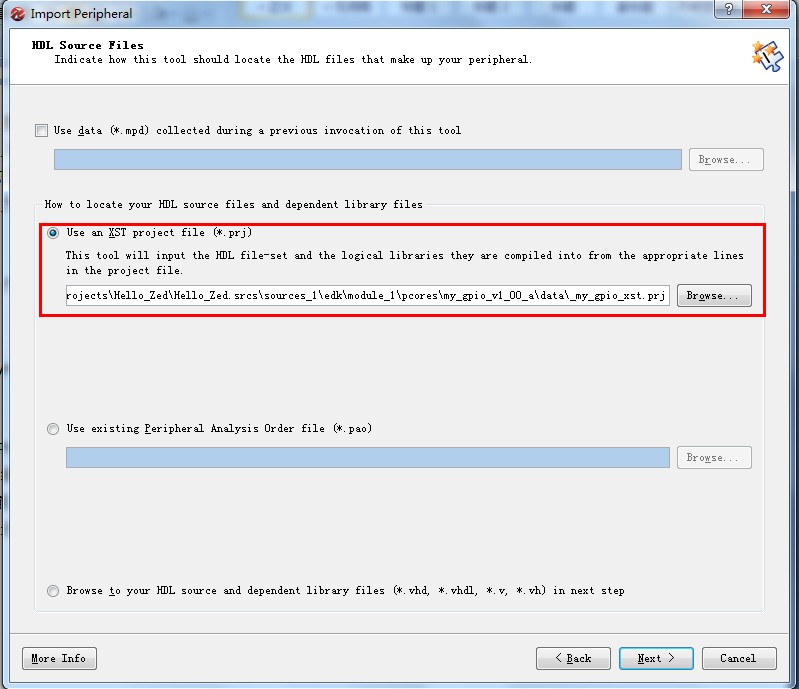

依旧起名为my_gpio,在弹出的提示中选Yes覆盖,之后一路Next到HDL Source Files窗口,选择IP核的\data\_my_gpio_xst.prj文件。

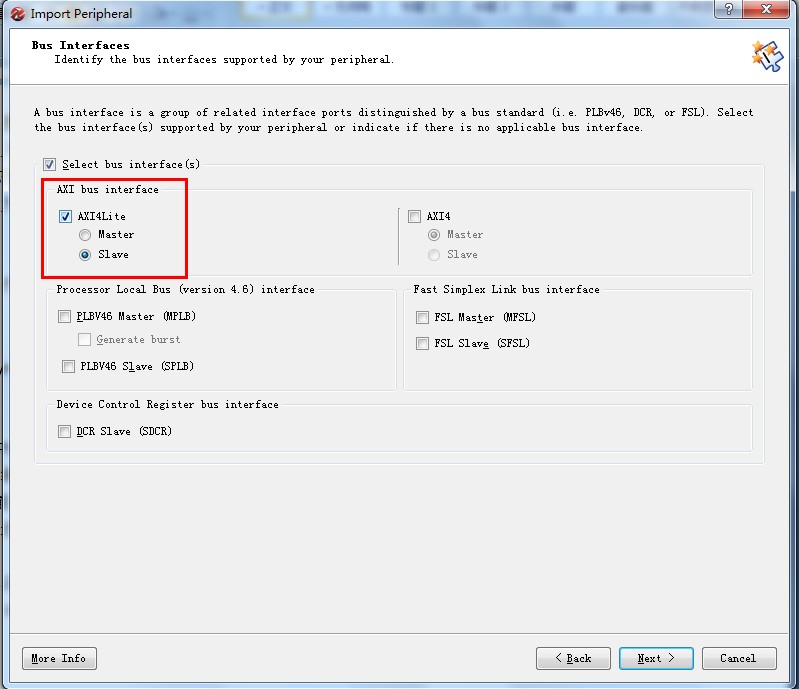

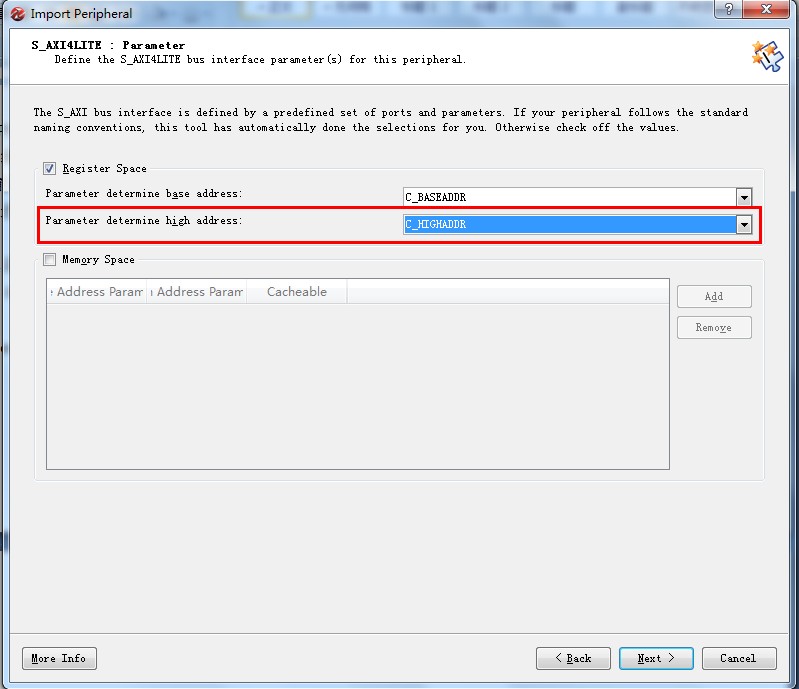

继续Next,直到这里选择总线类型为AXI4-Lite Slave类型。

接着在参数窗口中指定High Address的参数为C_HIGHADDR。

好了,Next到结束,这时刚才进行的修改已经生效并被成功导入了,现在双击my_gpio,保持默认选项不管,将其添加到系统中。

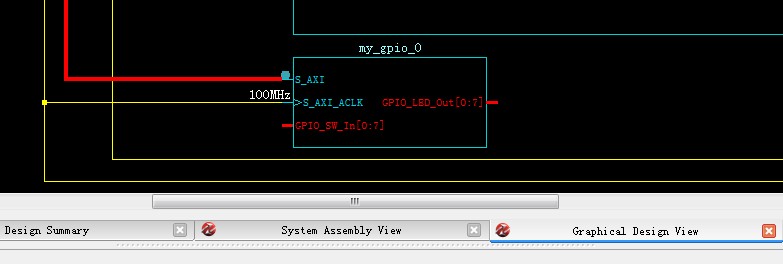

在Graphic视图中,可以看到my_gpio的框图,包括一组已经连接的AXI总线,和两组我们刚才定义的端口。

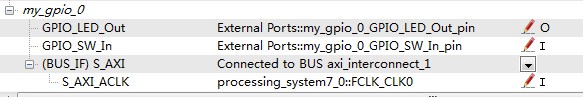

进入Port界面,将LED和SW端口设置为对外,确保最后看起来是这个样子。

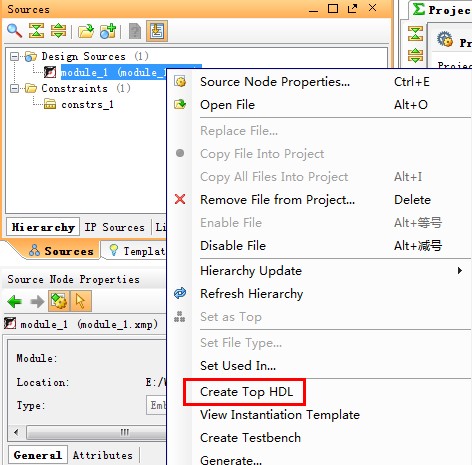

好了,关闭XPS,回到PlanAhead,生成Top HDL(如果之前做了可忽略)。

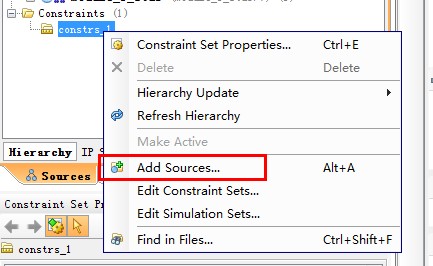

新建一个约束文件,并设置SW和LED的端口约束。

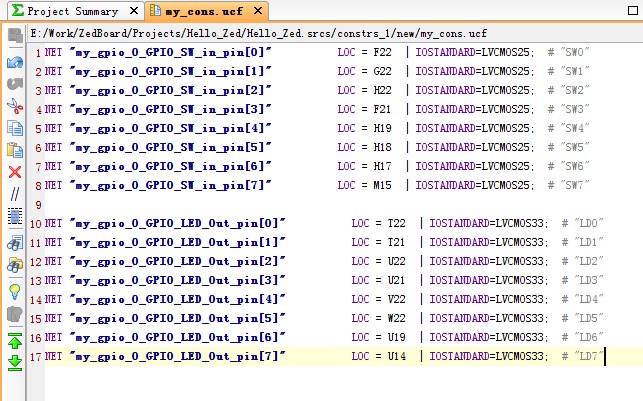

约束内容如下(建议手动输入,如果Copy了什么非法字符是很麻烦的,害我查了好久):

选择Generate Bitstream,系统会自动完成编译综合工作,最后生成包含PL配置信息的System.bit文件。

至此,my_gpio自定义外设就完成了,这个PL现在可以通过AXI总线与PS通信——让然还需要软件支持了,呵呵。

下篇将会介绍如何裸机软件调试外设,其步骤与ZedBoard_CTT文档中大同小异。

以上。

欢迎大家在美信DIY大赛专区论坛讨论问题:

http://maxim.eefocus.com/bbs/forumall_1237.html

更多ZedBoard资料请见美信社区:

http://maxim.eefocus.com

开发自定义AXI总线外设IP核——以LED和开关为例相关推荐

- Modelsim 仿真 DDR2 IP核 测试 和自定义仿真平台搭建 IP核仿真

说明:本文分为两部分,第一部分仿真QuartusII自己生成的DDR2 example, 第二部分为添加自己写的tesetbench文件仿真DDR2 关键词:DDR2仿真.Modelsim 软件:Qu ...

- PYNQ-Z1自制ip核(以呼吸灯为例)

设计框图如下,参考了正点原子的教程. 通过AXI控制PL端的led 1.创建ip核第一步 点击finsh.创建ip核 选择默认 Add....把ip添加到工程 弹出一个ip核的界面编辑 添加pl端的代 ...

- niosII的那些事--基于AVALON总线的IP核定制

简介 NIOS II是一个建立在FPGA上的嵌入式软核处理器,除了可以根据需要任意添加已经提供的外设外,用户还可以通过定制用户逻辑外设和定制用户指令来实现各种应用要求.这节我们就来研究如何定制基于Av ...

- 基于AVALON总线的IP核定制 PWM

简介 NIOS II是一个建立在FPGA上的嵌入式软核处理器,除了可以根据需要任意添加已经提供的外设外,用户还可以通过定制用户逻辑外设和定制用户指令来实现各种应用要求.这节我们就来研究如何定制基于Av ...

- Microblaze添加自定义IP核,挂AXI总线实现SSD1306 OELD驱动

Microblaze添加自定义IP核,挂AXI总线,SSD1306 OELD驱动 前言 本着好好学习,认真负责的态度,我计划在空闲时间把自己用到的一些模块的使用方法与心得总结下与大家分享下,技术交流的 ...

- AXI总线基本知识:(基于uart_lite IP核)

1.属于片内总线 2.Uart_lite IP核接口描述: ACLK 主从设备交换数据的时钟信号 ARESETN 从模块复位信号 INTERRUPT 中断信号 AWADDR[3:0] 写地址 AWVA ...

- ZYNQ学习之路3. 定制AXI IP核

ZYNQ最大的优点就是硬核A9处理器与FPGA的结合,处理器可以扩展出任何使用者想要的外设(数字逻辑外设),FPGA与处理器通过AXI高速总线进行连接,提供了处理器到FPGA的高速带宽(ZYNQ700 ...

- (原创)LEON3入门教程(四):基于AMBA APB总线的七段数码管IP核设计

摘要:这一小节将介绍下如何设计用户自定义的APB IP,并将IP嵌入到SOPC中去.一个APB IP核的主要分为三个部分:逻辑单元.寄存器单元和接口单元.所设计的IP是一个简单的七段数码管显示IP,只 ...

- 【Xilinx AX7103 MicroBalze学习笔记6】MicroBlaze 自定义 IP 核封装实验

目录 实验任务 实验框图 创建自定义 IP 封装 IP IP 封装界面配置 硬件设计(Vivado部分) Block Design搭建 添加 IP 库 约束文件 软件设计(SDK部分) 往期系列博客 ...

最新文章

- C++中extern使用

- win7 安装Redis

- Windows10下编译NCNN安卓NDK

- ROBOT STUDIO 学习笔记

- 计算机系统基础 数据的表示和存储

- 算法测试及对比度进一步增强

- 每日一道shell练习(09)——sed处理

- docker启动redis并使用java连接

- php--学习封装类 (一)(操作mysql数据库的数据访问)

- Ubuntu 上安装 Node.js

- Operation,Tensor, Variable

- JMeter接口测试工具基础 — Badboy工具

- ubuntu三行命令更新谷歌浏览器版本

- 【微信小程序】微信小程序基础知识篇

- a到z的ascii码值是多少_c语言 ASCLL码中 A~Z和a~z是多少

- SEO外链收录:锚文本外链代发排名

- 架构师教你:如何实现两个完全独立闭环业务系统的融合。

- 2019微信公开课 同行With Us 听课笔记及演讲全文

- sa结构组网方式_SA和NSA这两种组网模式?哪个才是5G最佳选择?

- 数据库排行榜|当 DB-Engines 遇见墨天轮国产数据库排行