计算机组成原理——存储系统(超详细,必看!!)

- 本篇文章是对王道考研的2021计算机组成原理学习笔记,希望对大家有所帮助。

文章目录

- 三、存储系统

- 3.1 基本概念

- 1.存储器的层次结构

- 2.存储器的分类

- 3.存储器的性能指标

- 3.2主存储器

- 3.2.1主存储器的基本组成

- 3.2.2 随机存取存储器RAM

- 1.存储元件不同导致的特性差异

- 2.DRAM的刷新

- 3.DRAM的地址线复用技术

- 3.2.3 只读存储器ROM

- 3.2.4 主存储器和CPU的连接

- 1.单块存储芯片与CPU的连接

- 2.多块存储芯片与CPU的连接

- 3.2.5 双端口RAM和多模块存储器

- 1.双端口RAM

- 2.多模块存储器

- 3.应用

- 3.3 Cache

- 3.3.1 Cache的基本概念和原理

- 3.3.2 Cache和主存的映射方式

- (1)全相联映射

- (2)直接映射

- (3)组相联映射

- 3.3.3 Cache替换算法

- 1.随机算法(RAND)

- 2.先进先出算法(FIFO)

- 3.近期最少使用(LRU)

- 4.最近不经常使用(LFU)

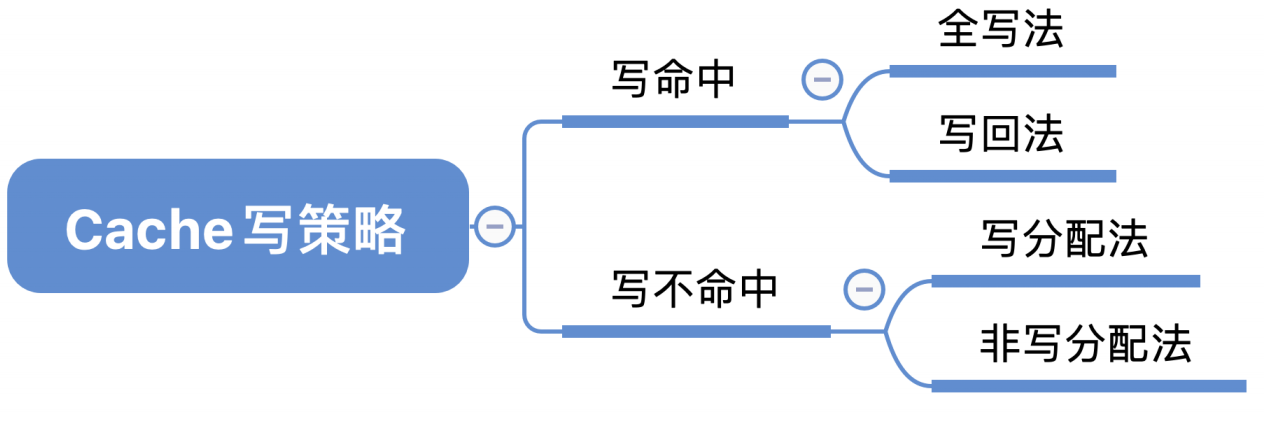

- 3.3.4 Cache写策略

- 1.写命中

- 2.写不命中

- 3.多级Cache

- 3.4 虚拟存储系统

- 3.4.1 页式存储

- 3.4.2 虚拟存储器

- 1.页式虚拟存储器

- 2.段式虚拟存储器

- 3.段页式虚拟存储器

三、存储系统

3.1 基本概念

知识总览:

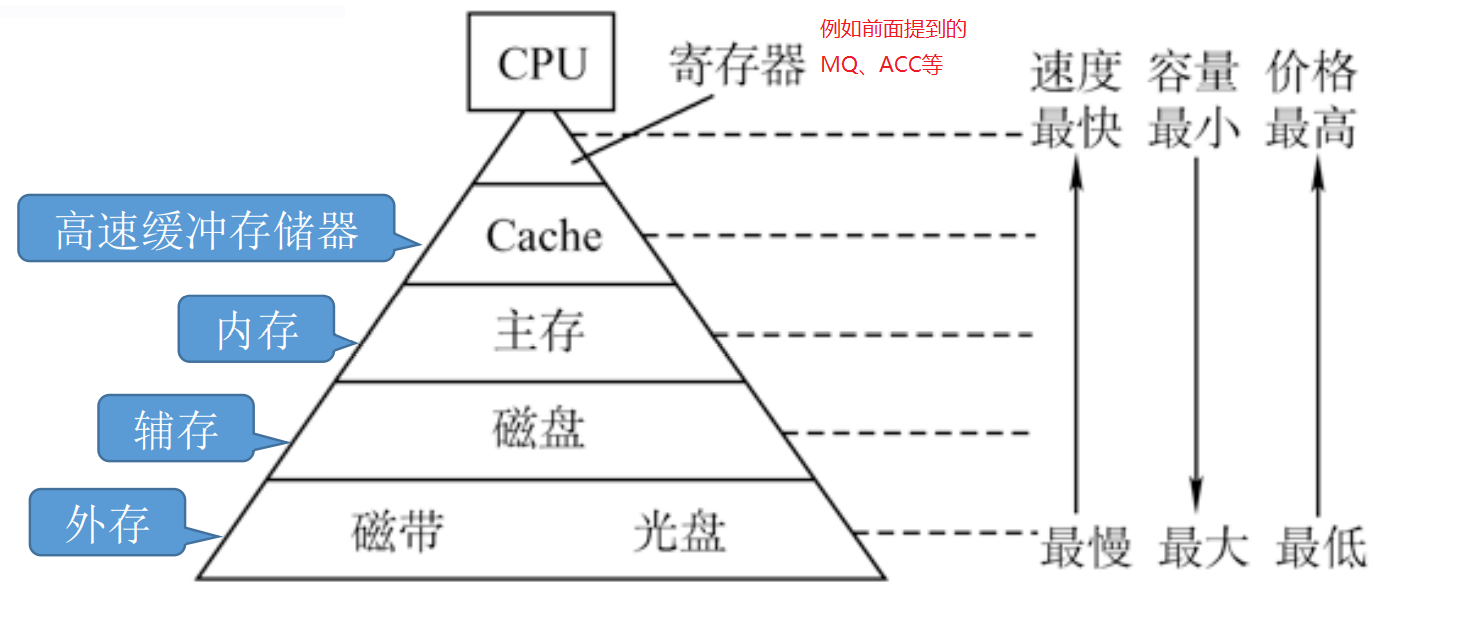

1.存储器的层次结构

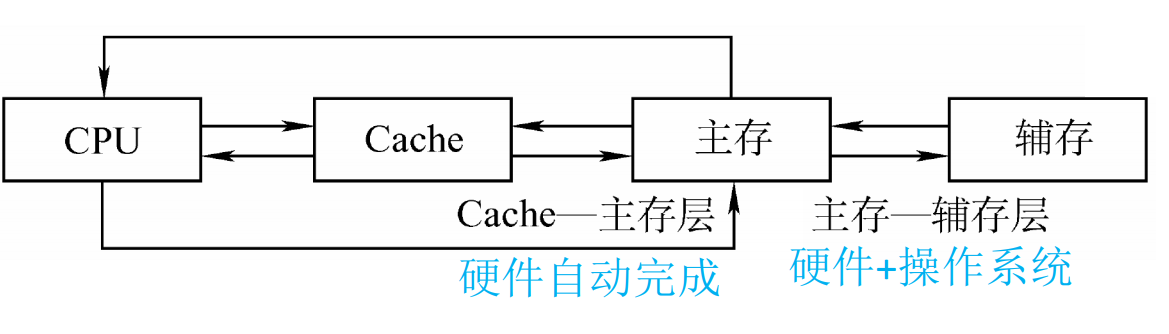

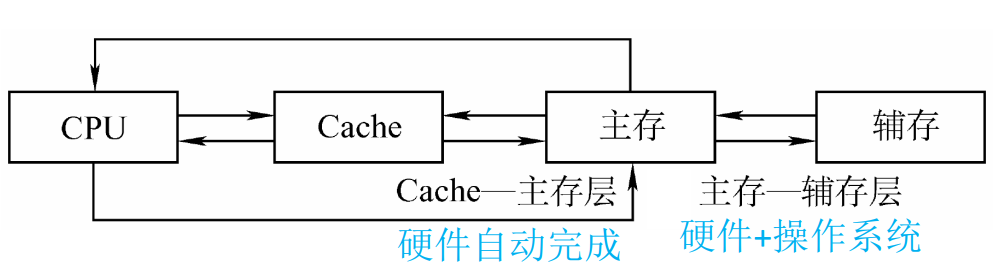

主存——辅存:解决了主存容量不够的问题。

Cache——主存:解决了主存与CPU之间速度不匹配的问题。

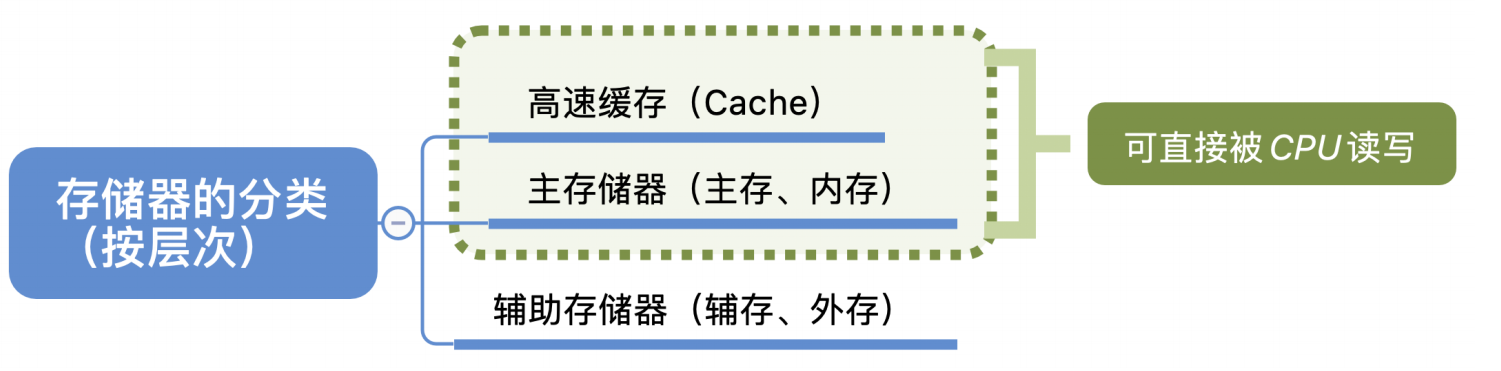

2.存储器的分类

(1)按层次进行分类

(2)按传输介质进行分类

- 半导体:主存、Cache

- 磁表面存储器: 磁盘,磁带

- 光存储器

(3)按存取方式进行分类

- 相联存储器:可以按照内容检索到存储位置进行读写。

- 随机存取存储器(RAM):读写任何一个存储单元所需的时间都相同,与位置无关。(内存 )

- 顺序存取存储器(SAM):读写一个存储单元所需的时间取决于存储单元所在的位置。(磁带)

- 直接存取存储器(DAM):既有随机存取特性,也有顺序存取特性。先直接选取信息所在区域,然后按顺序方式进行存取。(机械硬盘)

顺序存取存储器和直接存取存储器都归为串行访问存储器(读取时间和数据位置有关)。

(4)按信息的可更改性进行分类

- 读写存储器:可读可写(如内存,硬盘等)

- 只读存储器:只能读,不能写(如电影使用的光碟)

(5)按信息的可保存性进行分类

- 易失性存储器:断电后数据消失(主存,Cache)

- 非易失性存储器:断电依然保存(磁盘、光盘)

- 破坏性读出:读出数据后要进行重写(如DRAM芯片)

- 非破坏性读出:读出数据后原数据没被破坏(如SRAM芯片、磁盘、光盘)

3.存储器的性能指标

- 存储容量:存储字数 x 存储字长(如 1M x 8位 )。

MAR反映存储字数,MDR反映了存储字长。

单位成本:每位价格 = 总成本/总容量(某条内存条价格为259,容量为8GB,则单位成本 = 259 / (8*8) )。

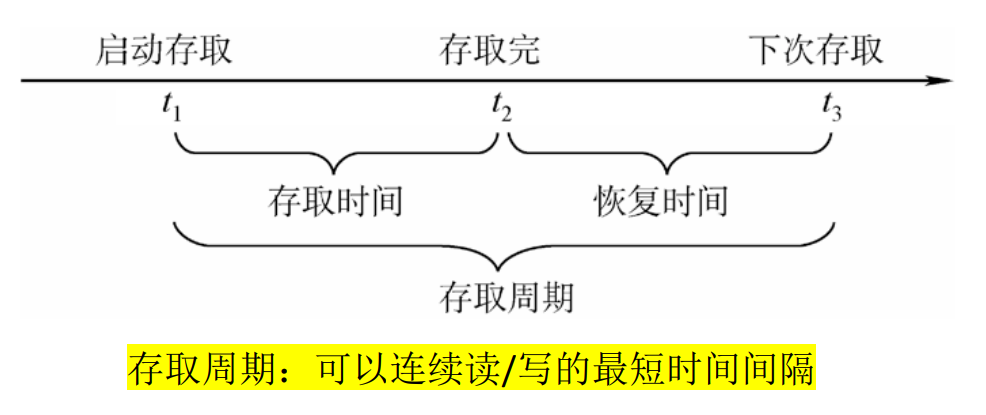

存储速度:数据传输率 = 数据的宽度/存储周期

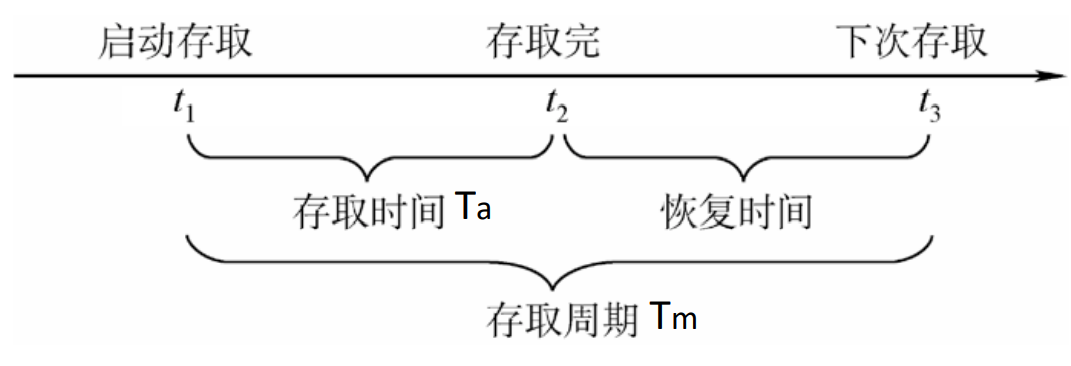

存取时间:存取时间 + 恢复时间 = 存取周期,计算机进行一次读写操作后需要一段恢复时间才能进行下一次的读写操作。

主存带宽:就是上面的数据传输率,表示每秒从主存进出信息的最大数量,单位为字/秒,字节/秒,位/秒。

3.2主存储器

3.2.1主存储器的基本组成

知识总览:

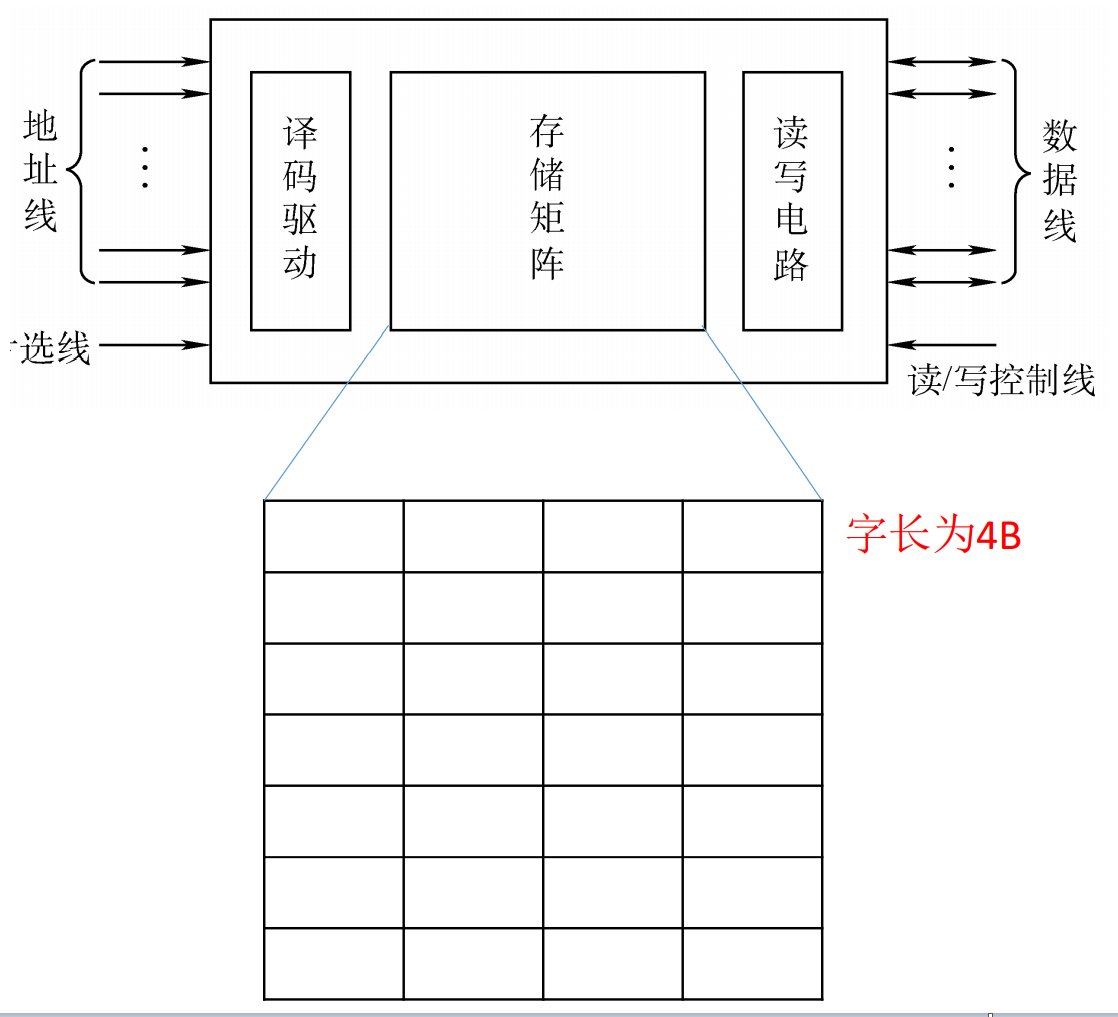

(1)存储体

存储体由多个存储单元构成,每个存储单元由多个存储元构成。

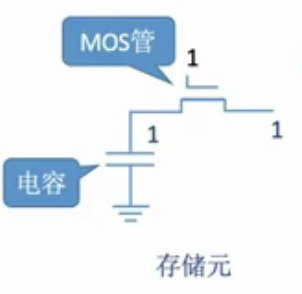

存储元:能够存储一位比特。

电容:存储电荷,有电压差表示比特1,无电压差表示比特0。

MOS管:一个电控开关,当输入电压到达某个阀值时,MOS管就可以接通,电容中的电荷就可以跑出来。(相当于一个电路的开关)

将多个存储元组合起来就构成了存储单元,同个存储单元的存储元共用一根MOS管。

将多个存储单元组合起来就构成了存储体。

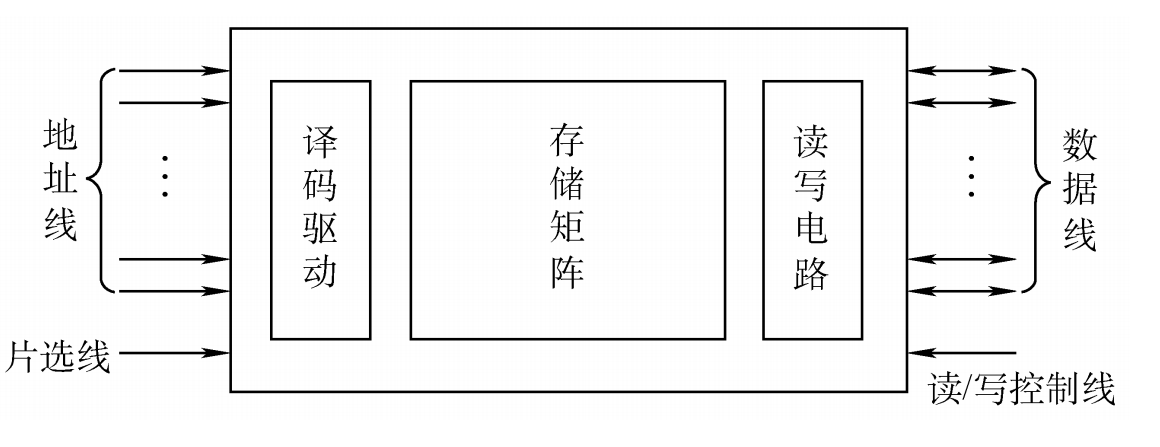

(2)地址寄存器和数据寄存器

通过 译码器来选择哪一个存储单元进行读写。

并通过数据总线传送数据。

(3)控制电路:

控制电路控制着 MAR,译码器和MDR的数据处理。

同时存储芯片还需要对外提供 片选线,读选择线,写选择线。

片选线:芯片的总开关,低电平有效时表示选择了这块芯片进行工作了。

读选择线,写选择线:分别用来控制是读还是写。有时候会将这两根线合为一条,用低电平表示写,用高电平表示读。

(4)从总体上来看:

这里也表明了片选线的作用,上述的内存条是由多个存储芯片构成,假设每个存储芯片为1GB,则这条内存条条就为8GB,在进行读写数据时,需要通过片选线来选取不同的存储芯片进行存储。

寻址:

假设该存储体中的存储字长为4B,总容量为1KB,则存储单元为256个。

寻址方式可分为四种:

- 按字节寻址:则有1K个地址,需要10根地址线

- 按字寻址:则有256个地址,字节地址等于字地址乘于字长。

- 按半字寻址

- 按双字寻址

3.2.2 随机存取存储器RAM

知识总览:

RAM主要分为两种:

SRAM:静态RAM,用于Cache

DRAM:动态RAM,用于主存

1.存储元件不同导致的特性差异

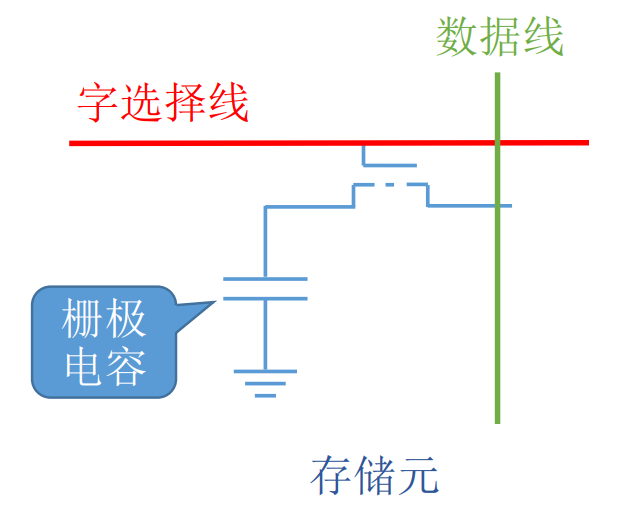

DRAM芯片:使用栅极电容来存储信息

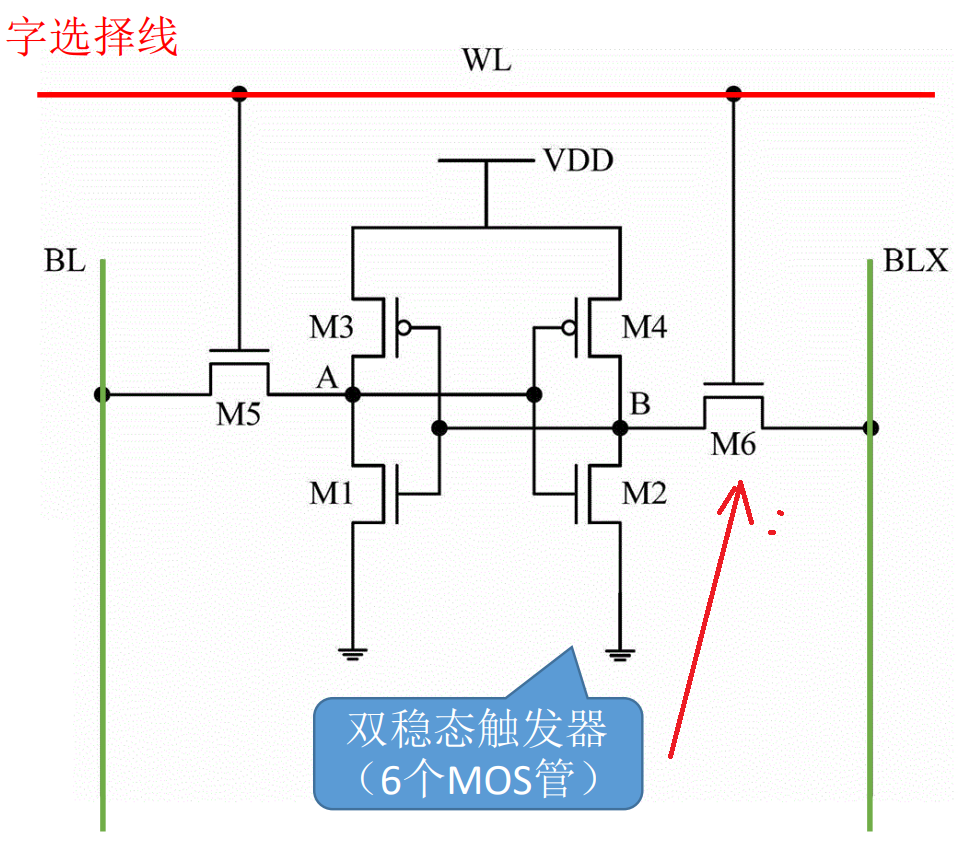

SRAM芯片:使用双稳态触发器来存储信息

(1)栅极电容:

1:电容内存储了电荷

0:电容内未存储电荷

破坏性读出:电容放电后相当于电荷跑了出来,导致信息破坏,所以读出后需要有重写操作,也称为再生。这也是DRAM读写速度比SRAM慢的原因。

电容内的电荷只能维持2ms,即便不断电,2ms后信息也会消失。所以在2ms之内必须刷新一次,给电容充电。

每个存储元制造成本更低,集成度高,功耗低。

(2)双稳态触发器:

1:A处为高电平并且B处为低电平

0:A处为低电平并且B处为高电平

非破坏性读出:读出数据后,触发器状态保持稳定,无需重写。读写速度更快。

只要不断电,触发器的状态就不会改变。

每个存储元制造成本更高,集成度低,功耗高。

2.DRAM的刷新

(1)多久刷新一次:一般为2ms

(2)每次刷新多少个存储单元:以行为单位,每次刷新一行存储单元。

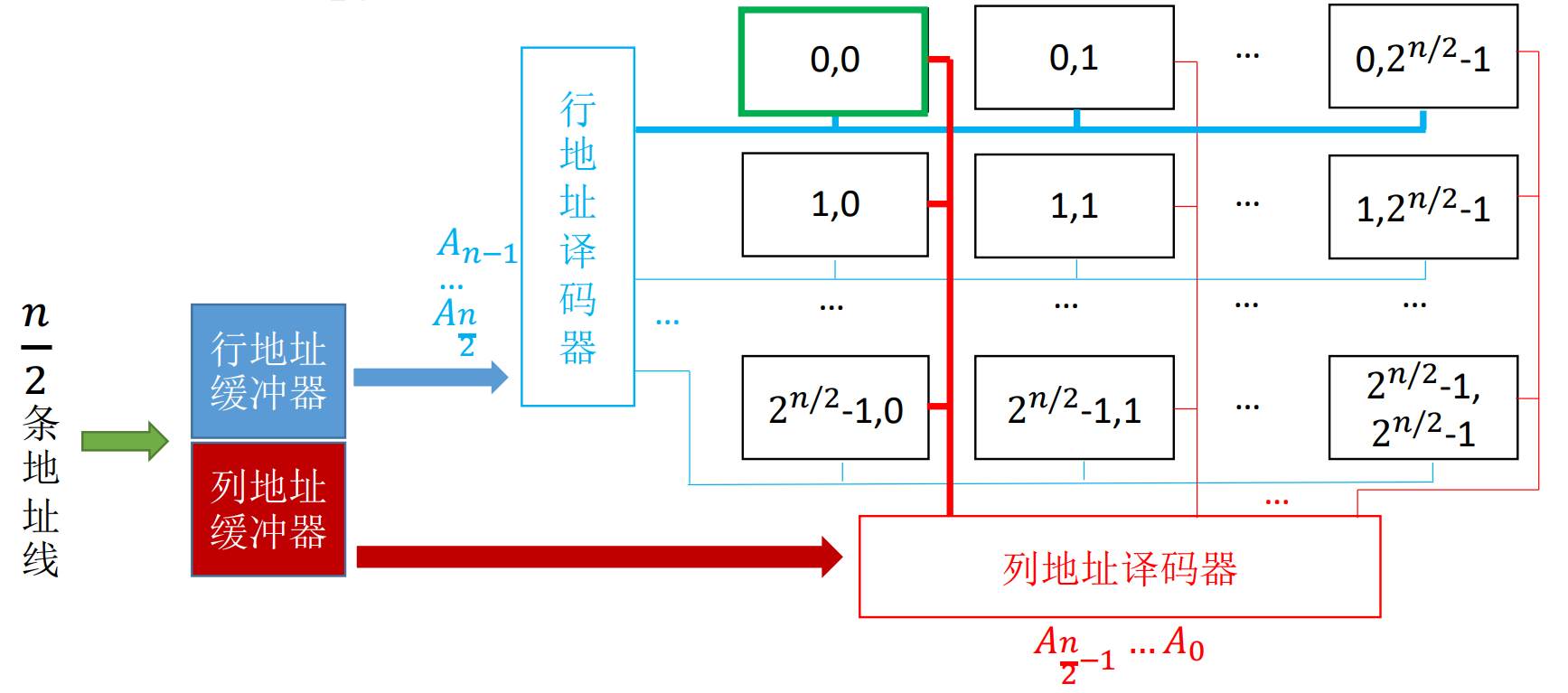

存储器中存储单元的排列是由 行地址译码器 和 列地址译码器 共同选择。

如果只使用一个译码器来进行地址选择的话,那么8位地址需要使用 28=256 条选通线,而使用行地址译码器和列地址译码器共同工作的话,只需要 24+24=32 条选通线,也就是行译码器16条选通线,列译码器16条选通线。

(3)如何刷新:有硬件支持,读出一行的信息后重新写入,占1个读/写周期。

(4)什么时候进行刷新?

假设DRAM内部结构排列成 128x128 的形式,读/写周期为 0.5us ,则 2ms 内共有 2ms/0.5us=4000个 读/写周期。

于是刷新的时间选择可以有以下三种思路:

3.DRAM的地址线复用技术

由于DRAM存储容量较大,存储单元数目多,所需地址线也就比较多,为了简化硬件,采用地址线复用技术,行地址和列地址分成两次进行传送到译码器中。

总结:

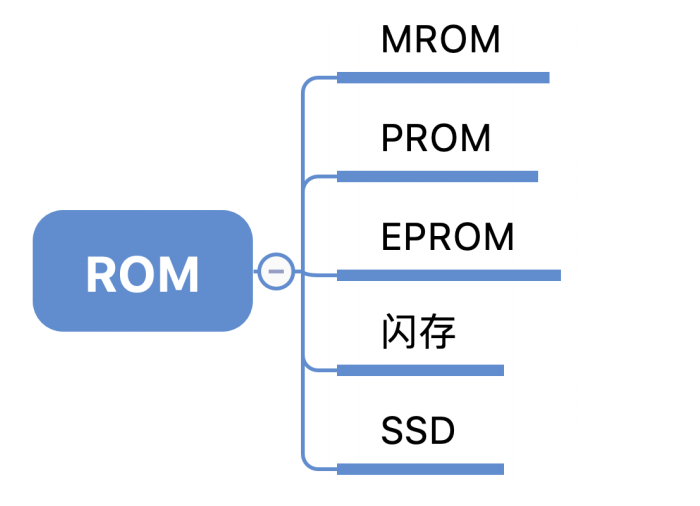

3.2.3 只读存储器ROM

- ROM芯片虽然叫做“Read Only”,但是很多ROM也可以写。

- 闪存的写速度一般比读速度慢,因为写入之前需要先擦除。

- 事实上很多ROM也是具有随机存取的特性的。

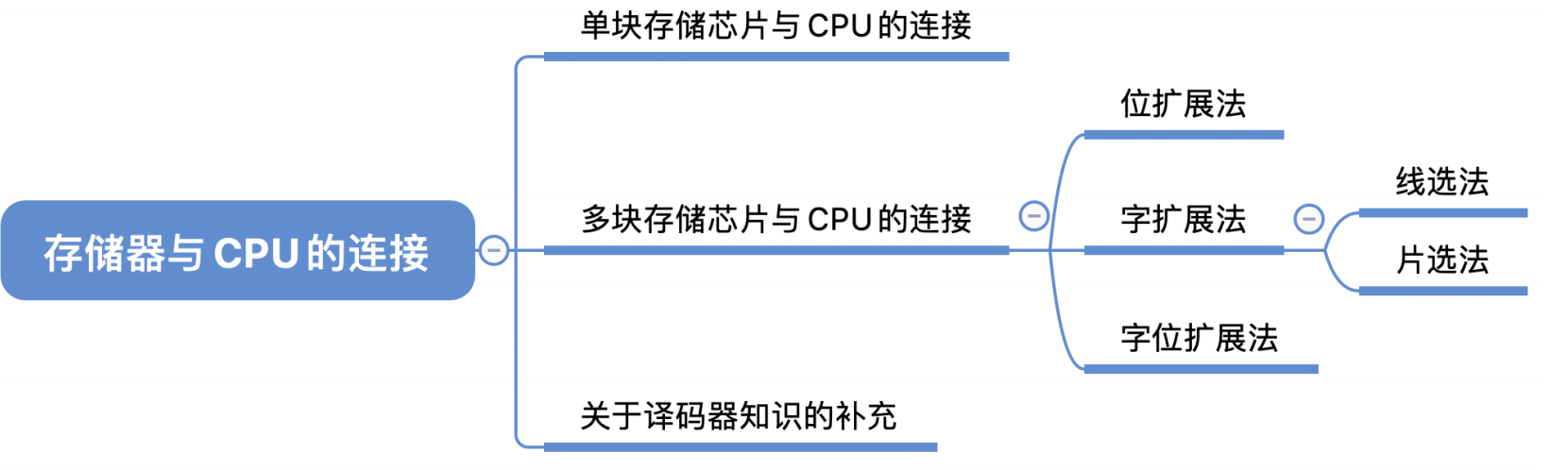

3.2.4 主存储器和CPU的连接

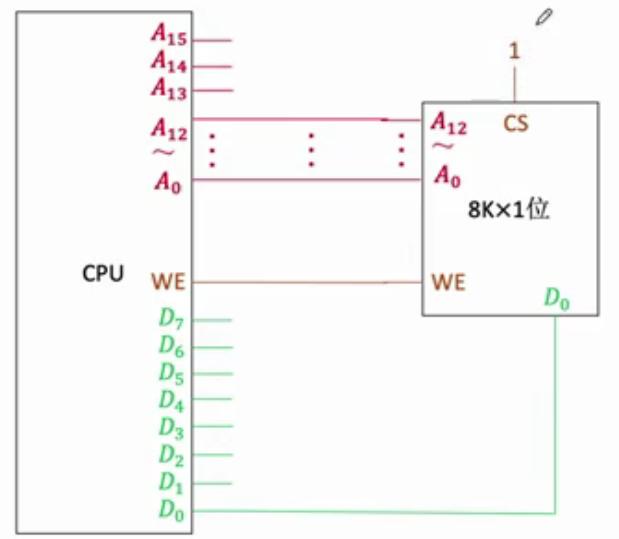

1.单块存储芯片与CPU的连接

假设有一块 8Kx1位 的存储芯片,说明此芯片需要 13根地址线,CPU有8个数据线和16根地址线,从上面可以看出,CPU每次只能传送1位数据到该芯片中,这会导致CPU的数据线没有得到充分利用,并且会有需要扩展主存容量的情况。

于是,就需要通过多个存储芯片的合理连接来扩展主存容量。

可以有两种方式:

- 位扩展:扩展存储单元的字长

- 字扩展:扩展存储单元的个数

2.多块存储芯片与CPU的连接

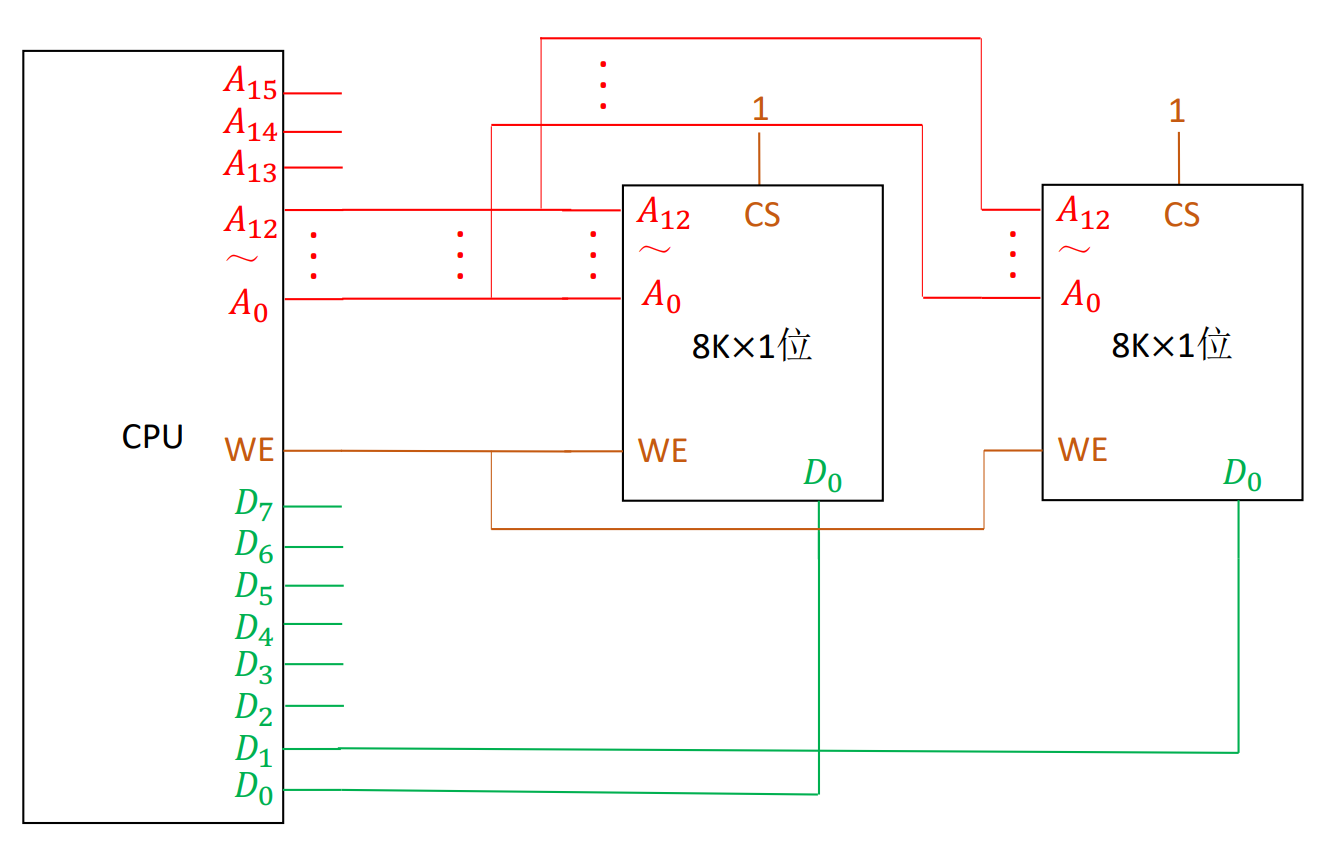

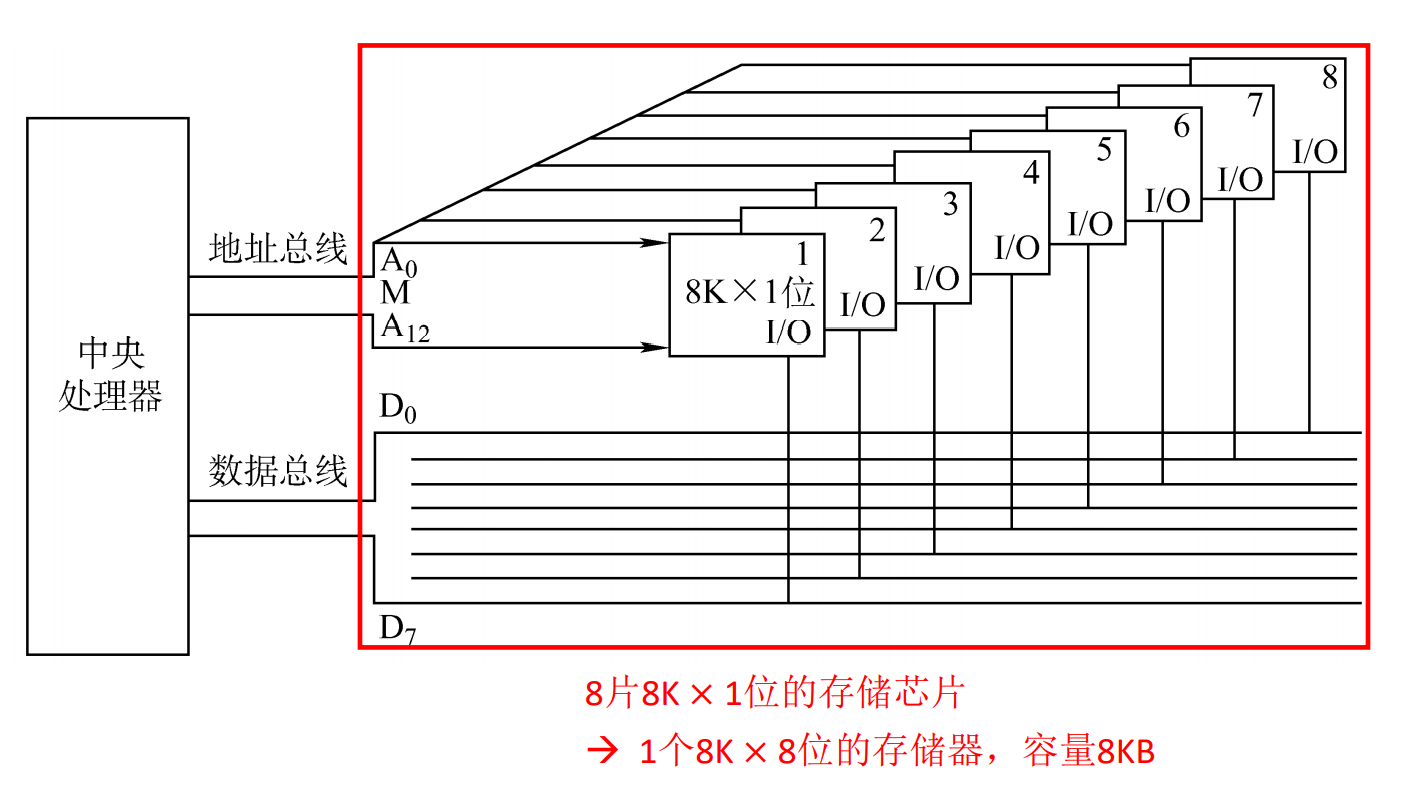

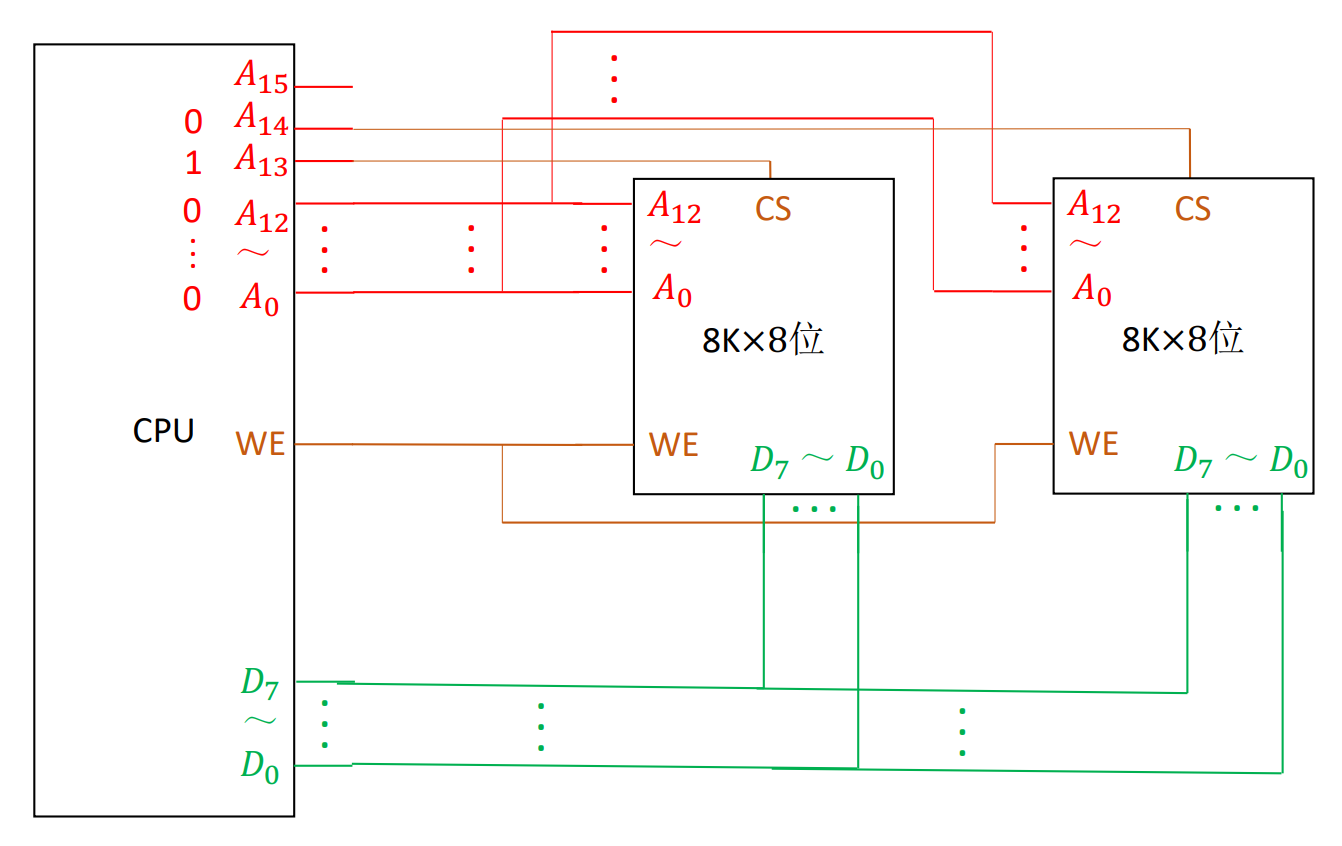

(1)位扩展:

如上图,将两片存储芯片进行连接,CPU地址总线A0~A12会一起发送给这两块芯片,而第二块芯片的数据线D0会和CPU的数据线D1进行相连。这样就扩展成了8Kx2位的存储器了。

同样,CPU中一共有D0~D7个数据线,因此可以总共连接8个图中所示的存储芯片,扩展成 8Kx8位的 存储器。

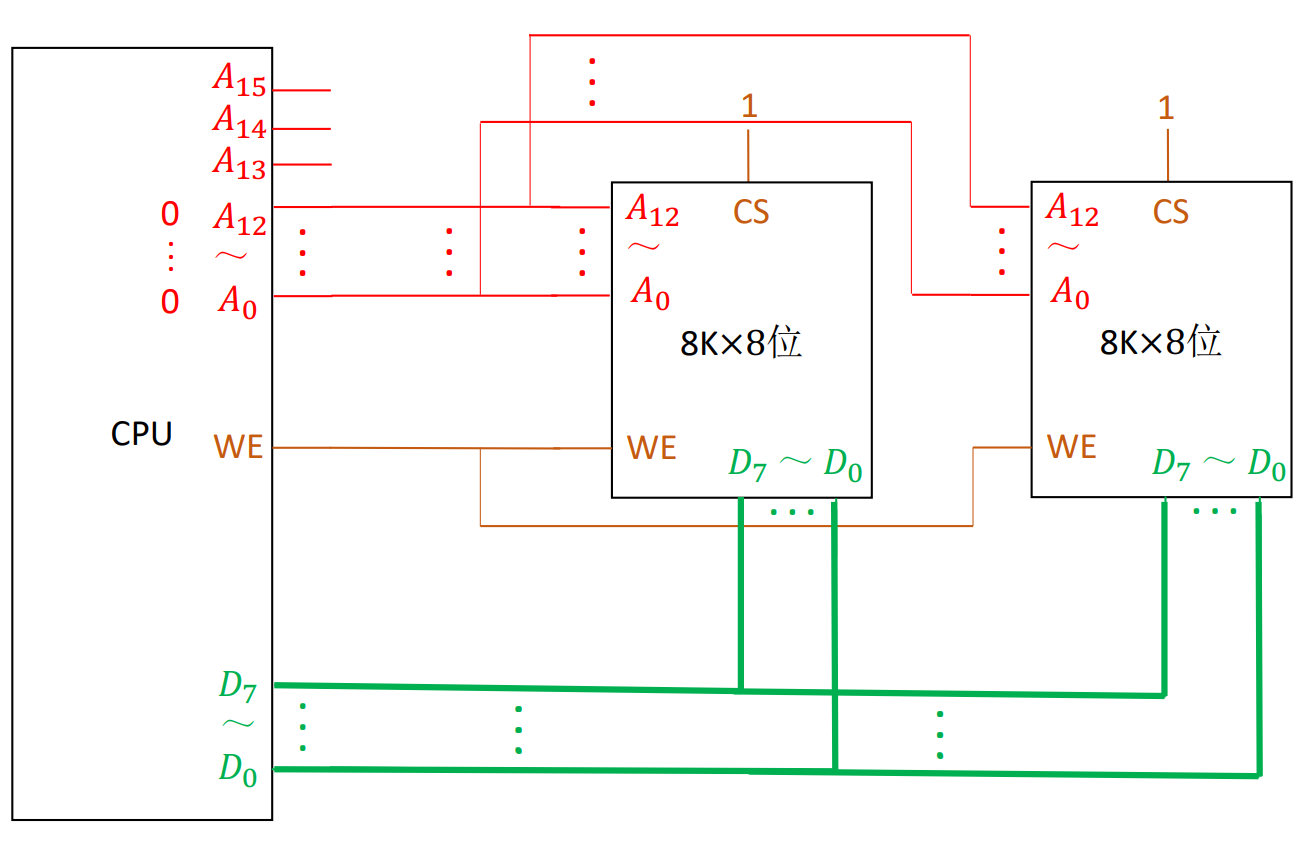

(2)字扩展:

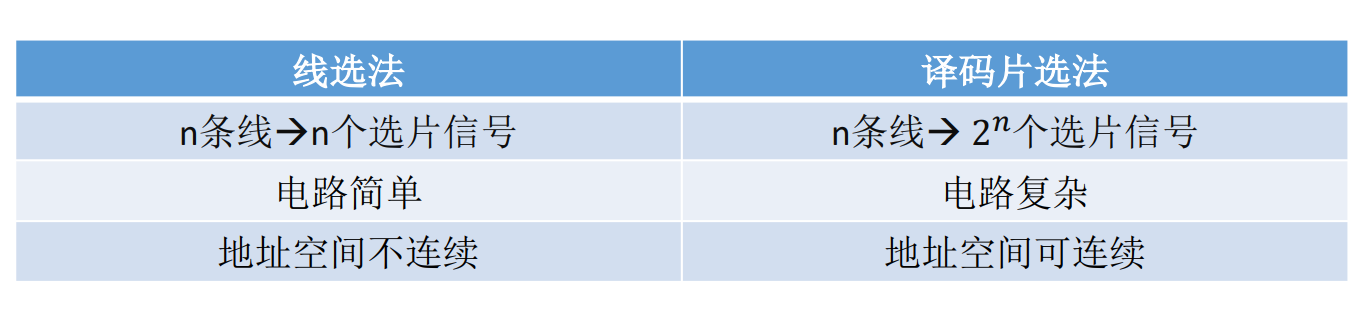

字扩展可分为两种:

- 线选法

- 片选法

如图中是一块 8Kx8位 的存储芯片,由于该芯片的存储单元字长等于CPU的数据总线数,因此不需要进行位扩展。而地址线并没有被完全利用到,因此可以考虑进行字扩展。

- 线选法:

用专门的地址线作为片选线,进行选择某一块存储芯片。

如图中:A13为第一块存储芯片的片选线,A14为第二块存储芯片的片选线,当A13 A14分别为01或10时,代表选中了第一块存储芯片或第二块存储芯片,这样就能扩展存储单元的个数。

此时第一块存储芯片的最低地址为:01 0000 0000 0000,最高地址为 01 1111 1111 1111

第二块存储芯片的最低地址为:100 0000 0000 0000,最高地址为 101 1111 1111 1111

但是线选法有一个缺陷:A13和A14不能取00或者11,因为取00时会导致两快存储芯片都没有被选中,11会导致两块存储芯片都被选中。并且需要n个片选信号。

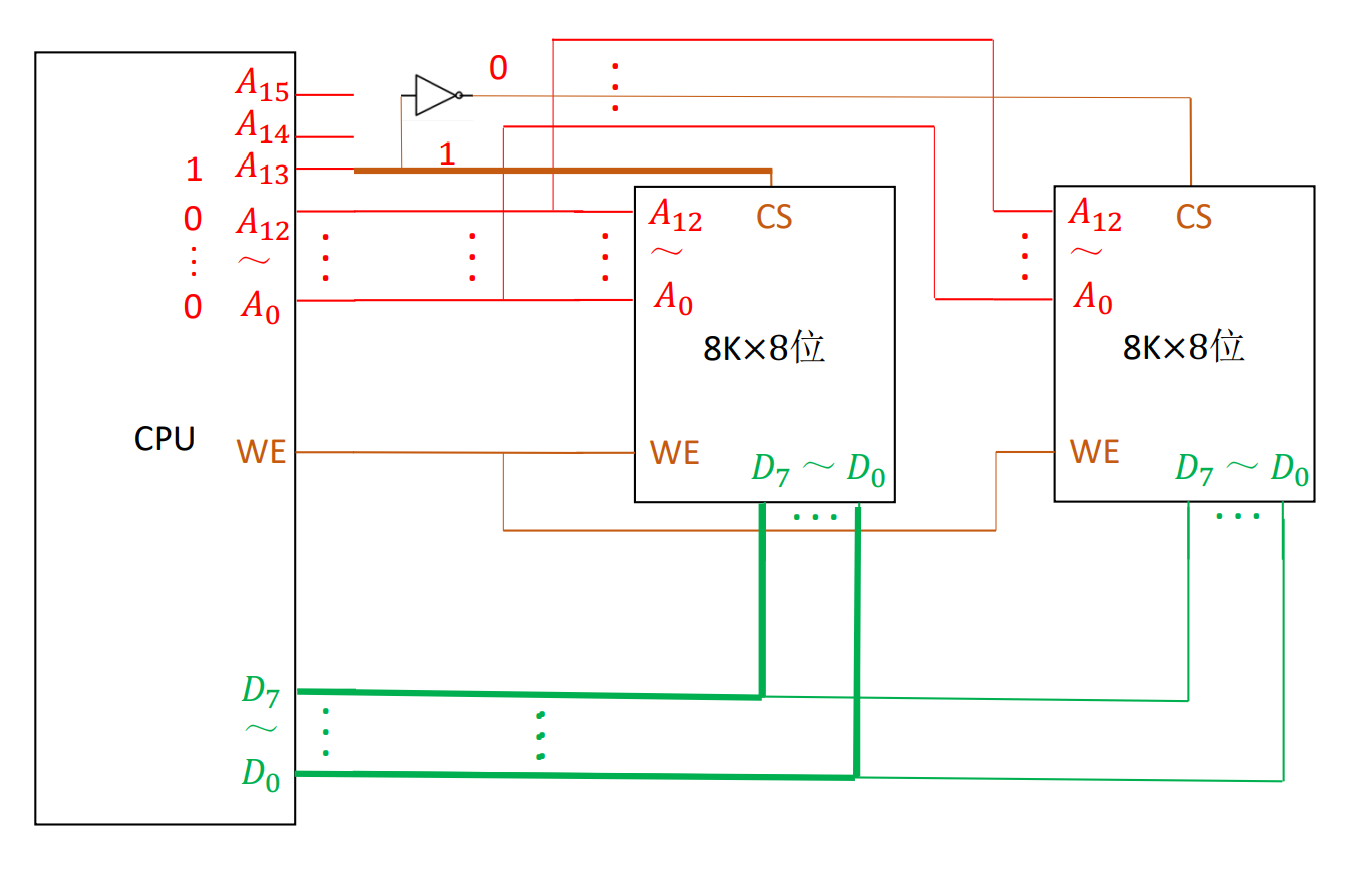

可以进行优化:

只通过A13和一个非门来进行选择。

此时第一块芯片的最低地址为10 0000 0000 0000,最高地址为11 1111 1111 1111

第二块芯片的最低地址为00 0000 0000 0000,最高地址为01 1111 1111 1111

- 片选法:

总结:

(3)位扩展和字扩展 同时扩展

3.2.5 双端口RAM和多模块存储器

知识总览:

- 存取周期 = 存取时间 + 恢复时间

前面讲到,DRAM由于电容的特性,每次进行读操作后需要进行重写,也就是需要一定的恢复时间,导致DRAM的存取周期比较长,并且这个恢复时间往往还比存取时间长。

这样会引出以下两种问题:

对于现如今的计算机,很多都是具有多核CPU,那么不同的CPU访问主存时,后续的CPU是否需要等待这么长的恢复时间呢?

CPU的读写速度比主存快很多,主存恢复时间太长怎么办?

这两个问题分别对应接下来的内容:双端口RAM 和 多模块存储器。

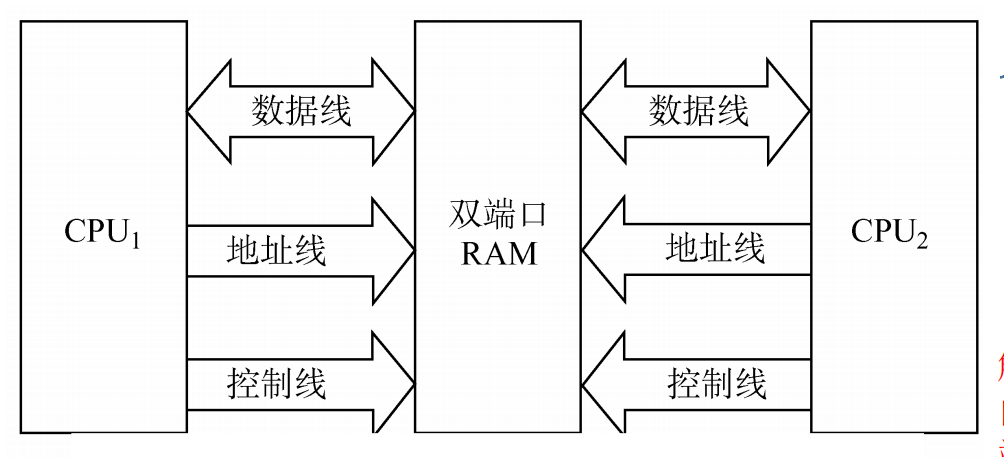

1.双端口RAM

**需要两组完全独立的数据线,地址线, 控制线。**CPU和RAM中也要有更复杂的控制电路。

两个端口对同一主存操作有以下4种情况:

当发生冲突时,会发出忙信号,有判断逻辑决定暂时关闭一个端口(即被延时),未被关闭的端口正常访问,被关闭的端口延长一个很短的时间断后再访问。

2.多模块存储器

(1)多体并行存储器:

图中每个方格表示一个存储单元。

高位交叉编址:每个存储体遍历完了之后再遍历下一个存储体。仅仅相当于扩容。

低位交叉编址:以横向方式遍历存储体,也就是每次都是遍历不同存储体的不同存储单元。这样,在读取其他存储体的存储单元时,之前读取过的存储单元可以利用这段时间进行恢复,达到一种并行的效果。

在模块数的选取上需要保证模块数 m >= T/r,这样才能保证存储体有足够的时间进行恢复。

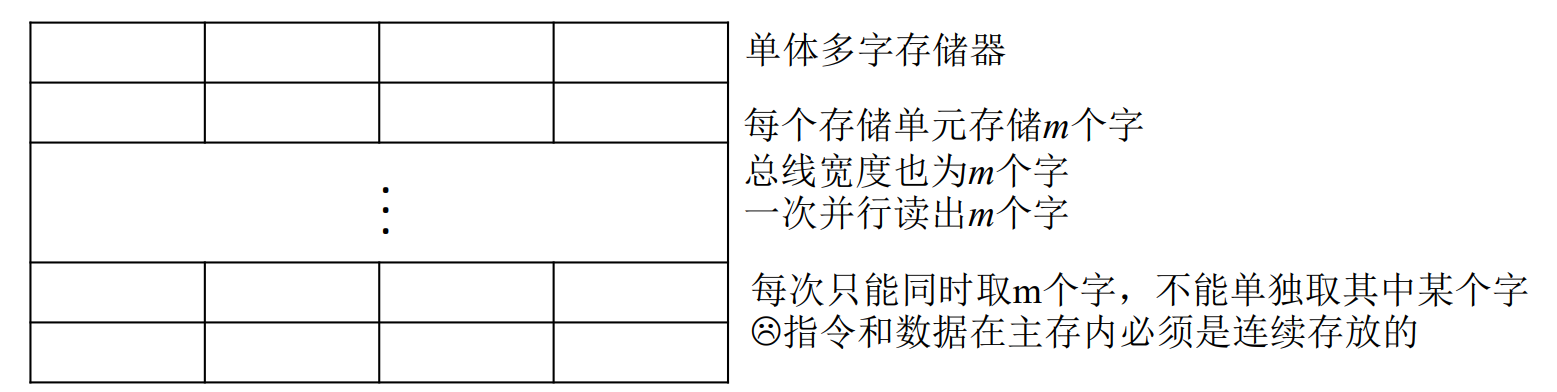

(2)单体多字存储器:

和多体并行存储器相反,单体多字存储器将多个存储体进行了合并,每次只能同时取m个字,不能单独取其中某个字,当某次读写的数据在不同行时,需要读入多余的信息。

3.应用

双通道内存:

原理:低位交叉编址的多体并行存储器。

3.3 Cache

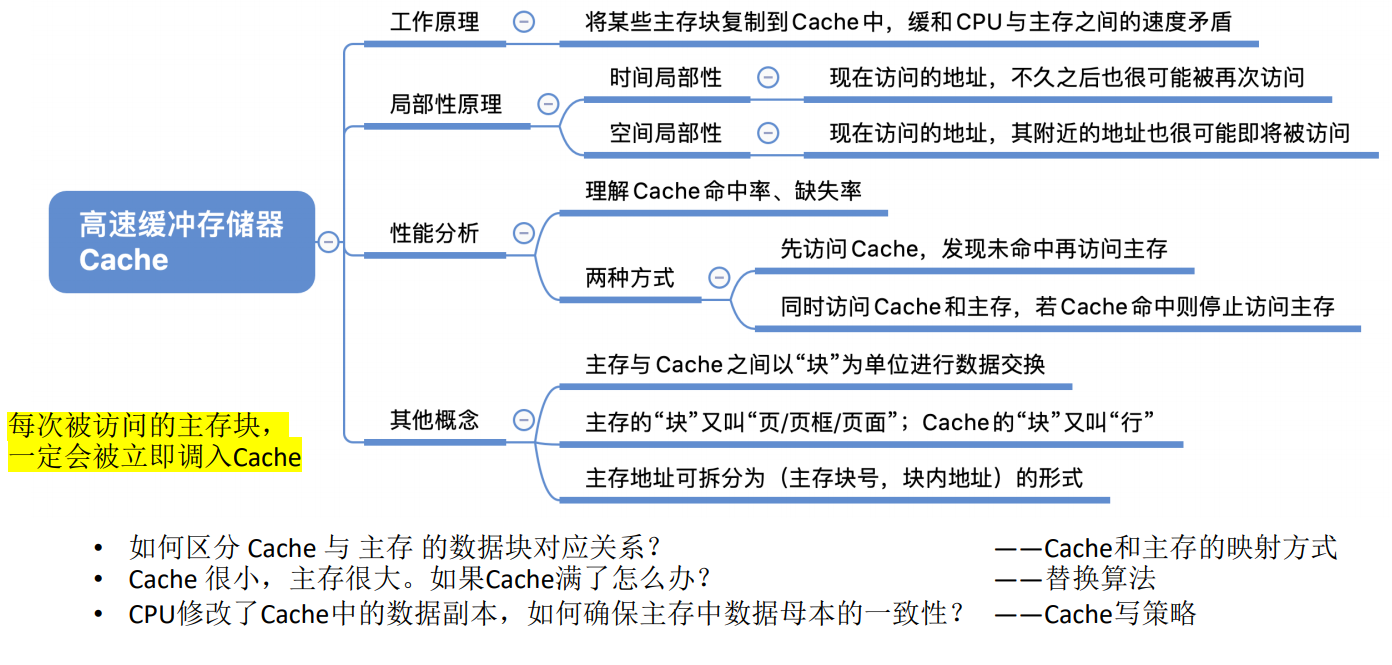

3.3.1 Cache的基本概念和原理

知识总览:

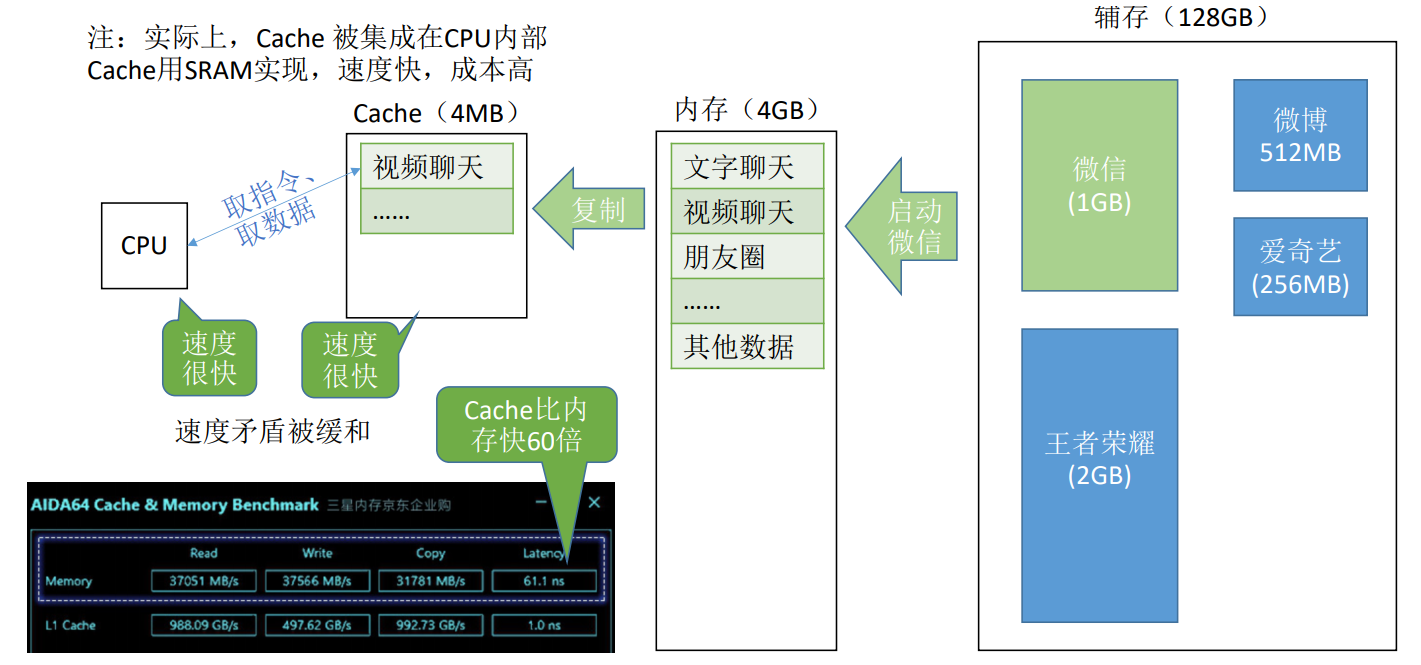

虽然 双端口RAM和多模块存储器已经提高了存储器的工作速度,但是和CPU的差距依然很大,于是就产生了缓存Cache,其价格更高,容量更低。

(1)工作原理:

**空间局部性:**在最近的未来要用到的信息,很有可能与闲杂i正在使用的信息在存储空间上是临近的。(信息的存储一般都是顺序的)

**时间局部性:**在最近的未来要用到的信息,很可能是现在正在使用的信息。(程序中很可能存在大量的循环结构,需要重复访问)

故Cache能够工作的理论依据:从上面两个局部性可以分析到,我们可以把CPU目前访问的地址周围的部分数据放到Cache中。

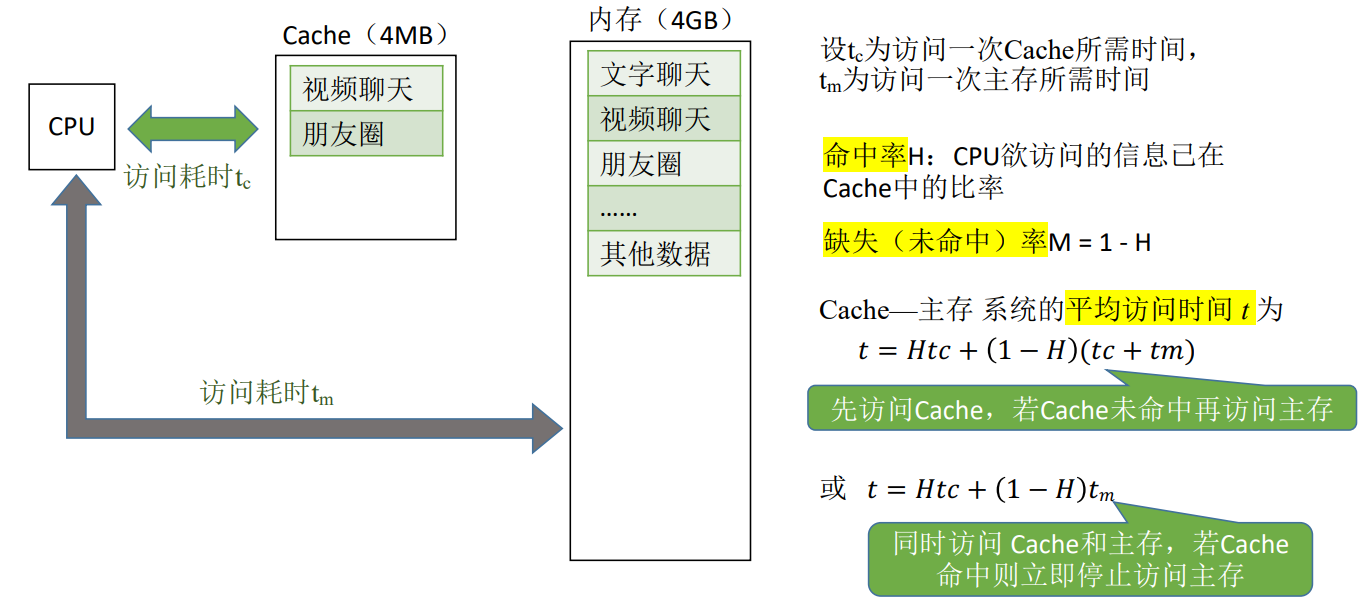

(2)性能分析:

设 **tc**为访问一次Cache所需时间,**tm**为访问一次主存所需时间。

CPU能够直接在Cache中找到所需信息,称为命中。

**命中率 H:**CPU欲访问的信息已在Cache中的比率。

**缺失率(未命中率)M:**M = 1 - H

**CPU平均访问时间 t 为:**t = H tc + ( 1-H ) ( tc+tm )

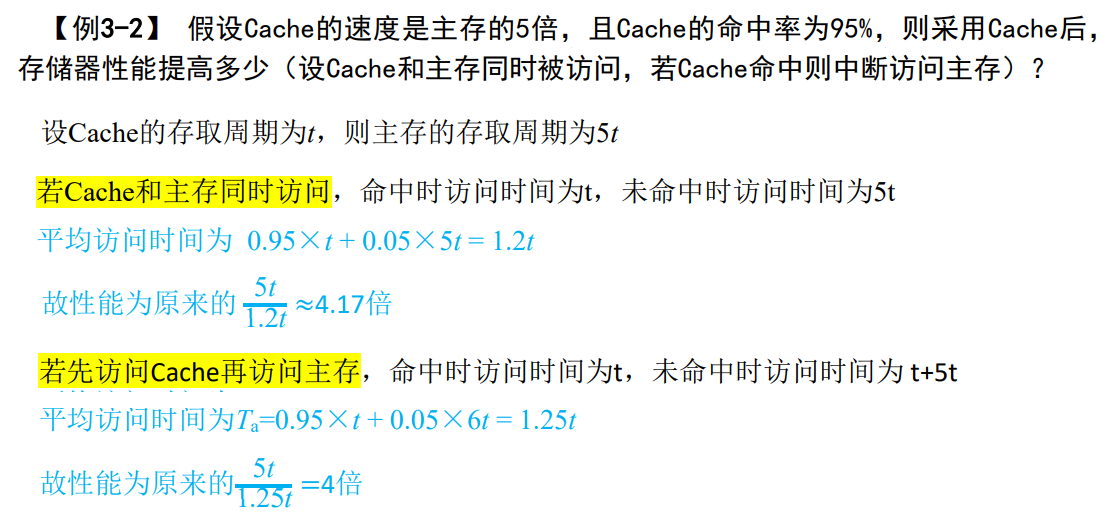

例题:

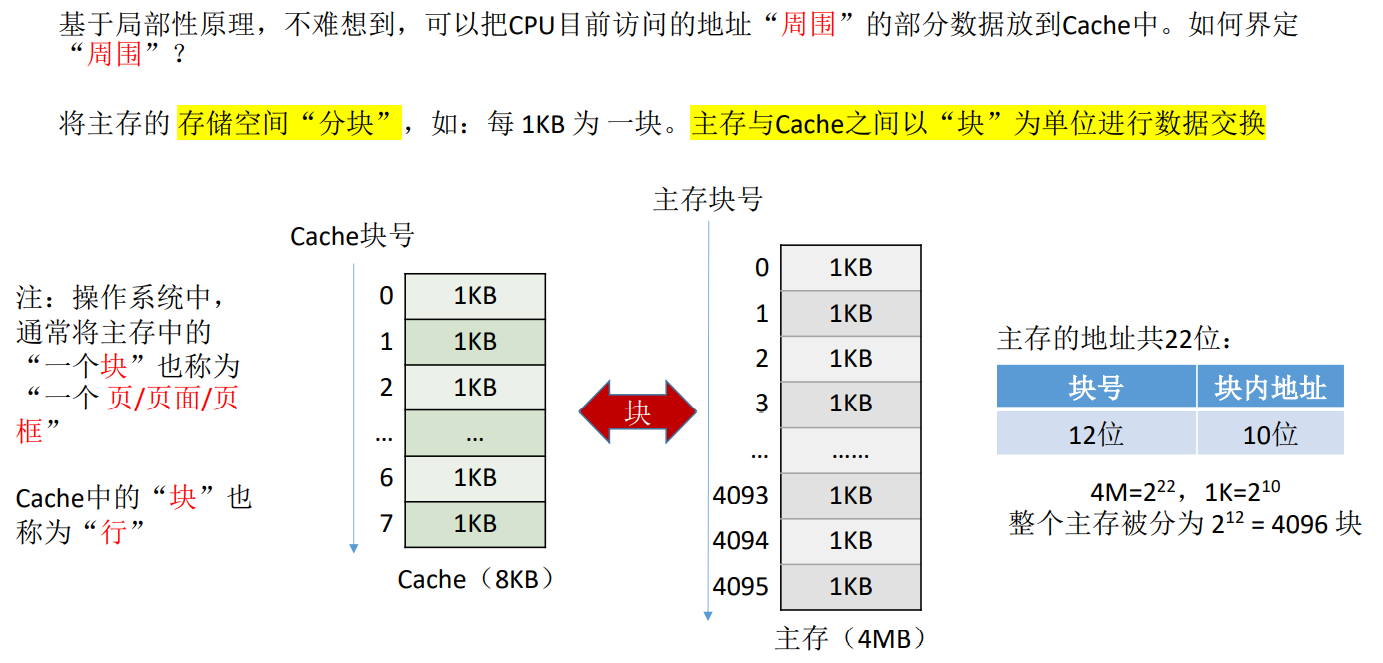

(3)如何界定“周围”:

将主存的存储空间进行分块,主存与Cache之间以块为单位进行数据交换。

这样主存地址就可分为两部分:块号 和 块内地址。

在操作系统中,通常将主存中的 “一个块” 也称为 “一个页/页面/页框” 。

Cache中的 “块” 也称为 “行” 。

Cache和主存之间仍然存在一些问题:

- 如何区分Cache和主存之间的数据块对应关系? ——Cache和主存的映射方式

- Cache很小,主存很大。如果Cache满了怎么办? ——替换算法

- CPU修改了Cache中的数据副本,如何确保主存中数据母本的一致性? ——Cache写策略

以上问题请继续看下面内容。

总结:

3.3.2 Cache和主存的映射方式

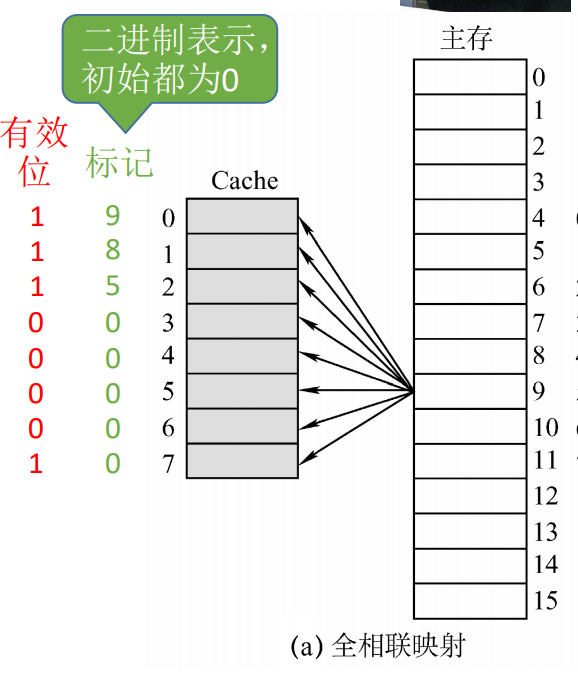

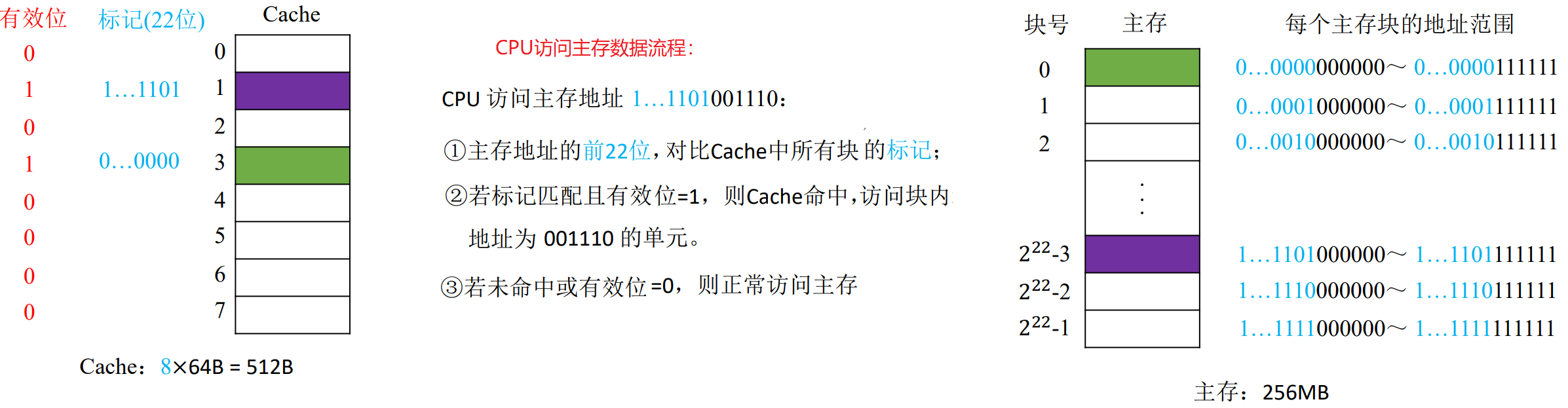

(1)全相联映射

任何一个主存块可以放在Cache的任意位置。

给每一个Cache块增加一个标记位,记录对应的主存块号。

还需要一个有效位,有效位为1时表示标记位有效,有效位为0时表示标记位无效。

以上图为例,主存中任意一块数据都可以存放在Cache任意一块中,只要标记好和主存数据的对应就行。例如主存中第9号块数据可以存放在Cache中0号到1号任意一个位置。

优点:Cache存储空间利用充分,命中率高。

缺点:查找速度较慢。

故CPU访问主存数据的流程如下:

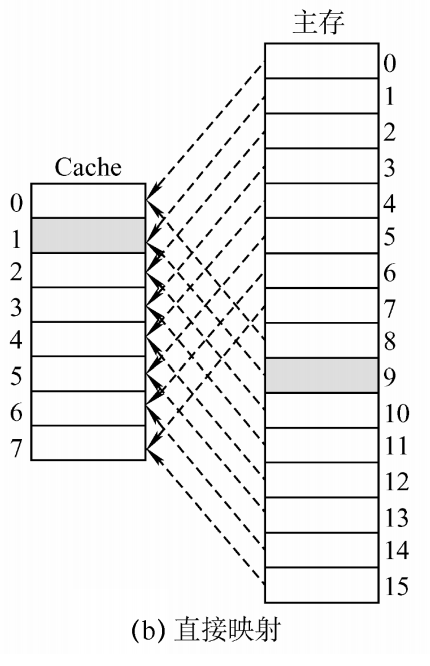

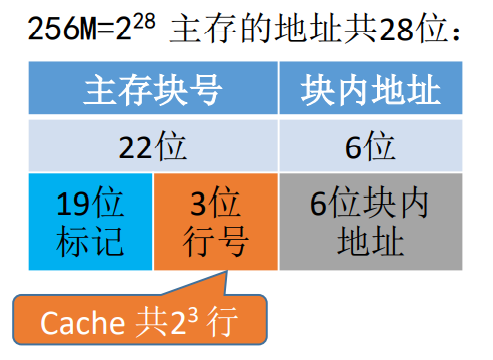

(2)直接映射

每个主存块只能放到特定的一个位置:Cache块号 = 主存块号 % Cache总块数。

以上图为例,8块为一个循环。主存中0号和8号块数据可以存放在Cache第0号块中,主存中1号和9号块数据可以存放在Cache第1号块中,以此类推。

**若Cache总块数 = 2n,则主存块号末尾 n 位直接反映它在Cache中的位置。**这是因为Cache块号 = 主存块号 % Cache总块数 = 主存块号末尾 n 位。

于是对于Cache所保存的标记号可以不用保存主存中对应的整个地址,可以只保留主存块号m前面(m-n)个二进制数。

故CPU访问主存数据流程如下:

优点:只需要对比一个标记,速度最快。

缺点:Cache存储空间不充分,命中率低。

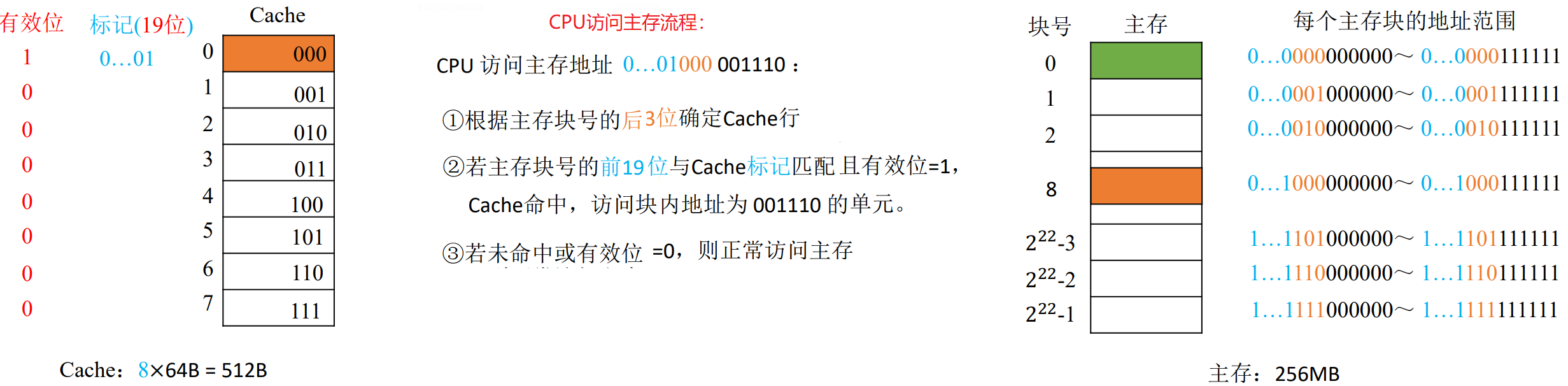

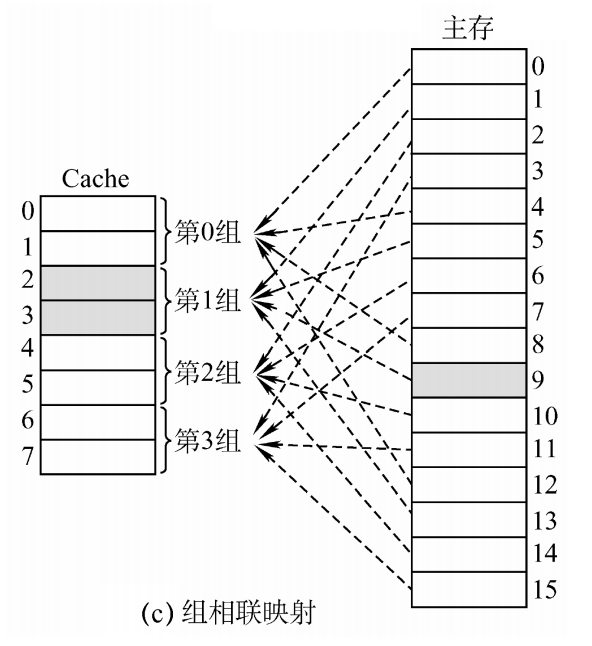

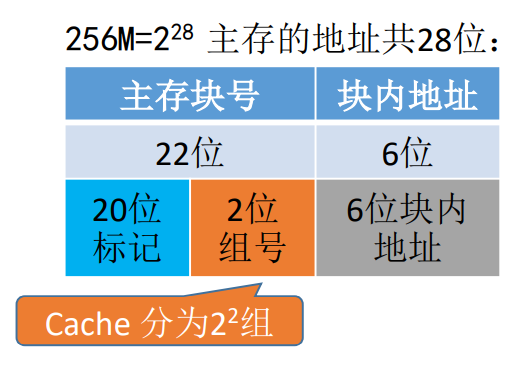

(3)组相联映射

将Cache块分为若干组,每个主存块可放到特定分组中的任意一个位置。

每个主存块对应的组号 = 主存块号 % 分组数

以上图为例,8块为一个循环组。0号和8号同属于第0组,0号和8号数据可以存放在第0组的任意一个位置,只要做好标记就行。

和直接映射一样,若Cache总分组数 = 2n,则主存块号末尾 n 位直接反映它在Cache中是第几组。

故CPU访问主存数据流程如下:

假设以下采用2路组相联映射,也就是 2块为一组,分四组。

优点:上面两种方法的折中,综合效果较好。

总结:

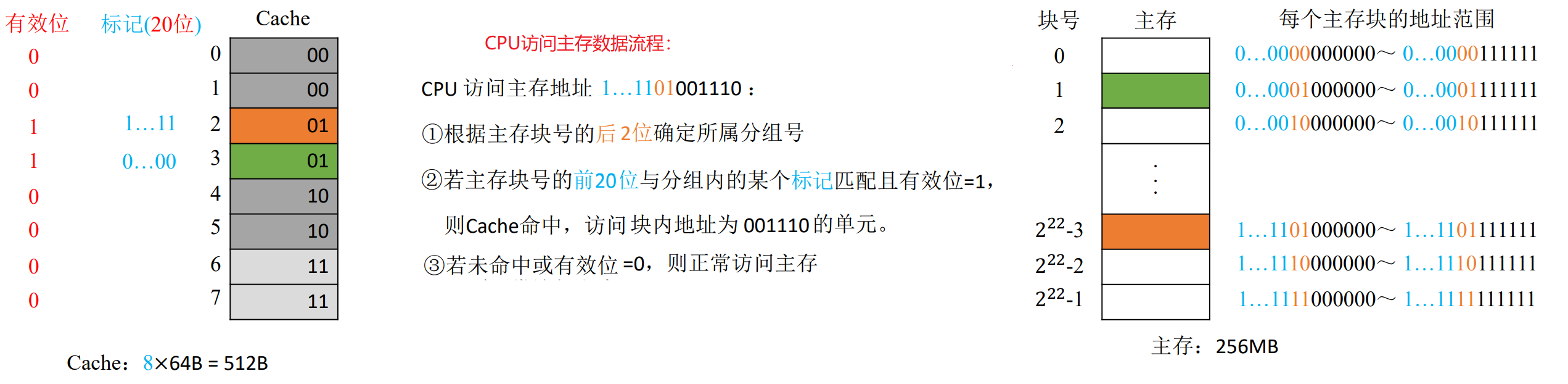

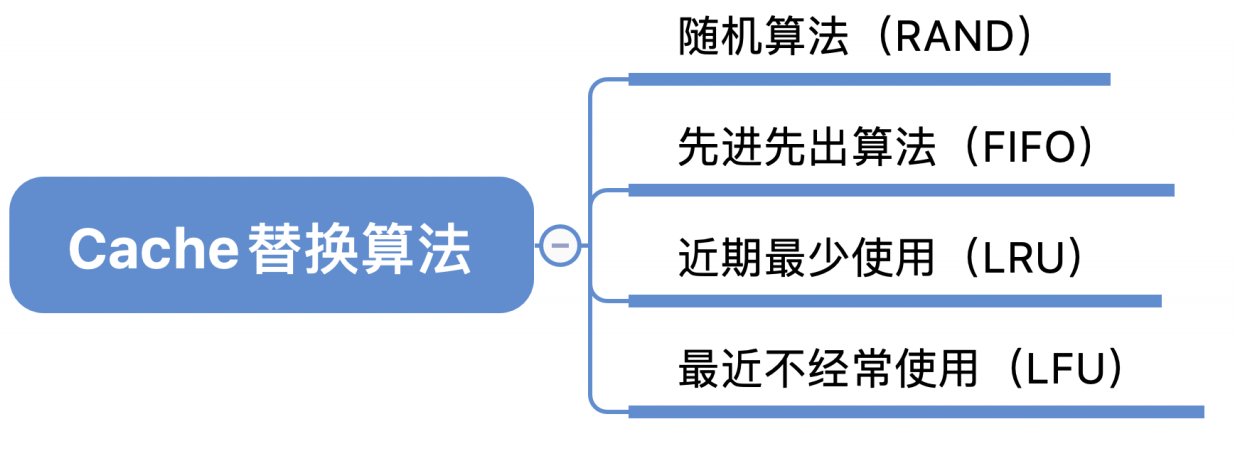

3.3.3 Cache替换算法

知识总览:

直接映射方式 由于主存数据块对应的Cache块是固定的,所以没得选择,不需要使用替换算法。

而全相联映射和组相联映射方式 由于可以选择不同位置进行替换,所以需要用到替换算法进行替换。

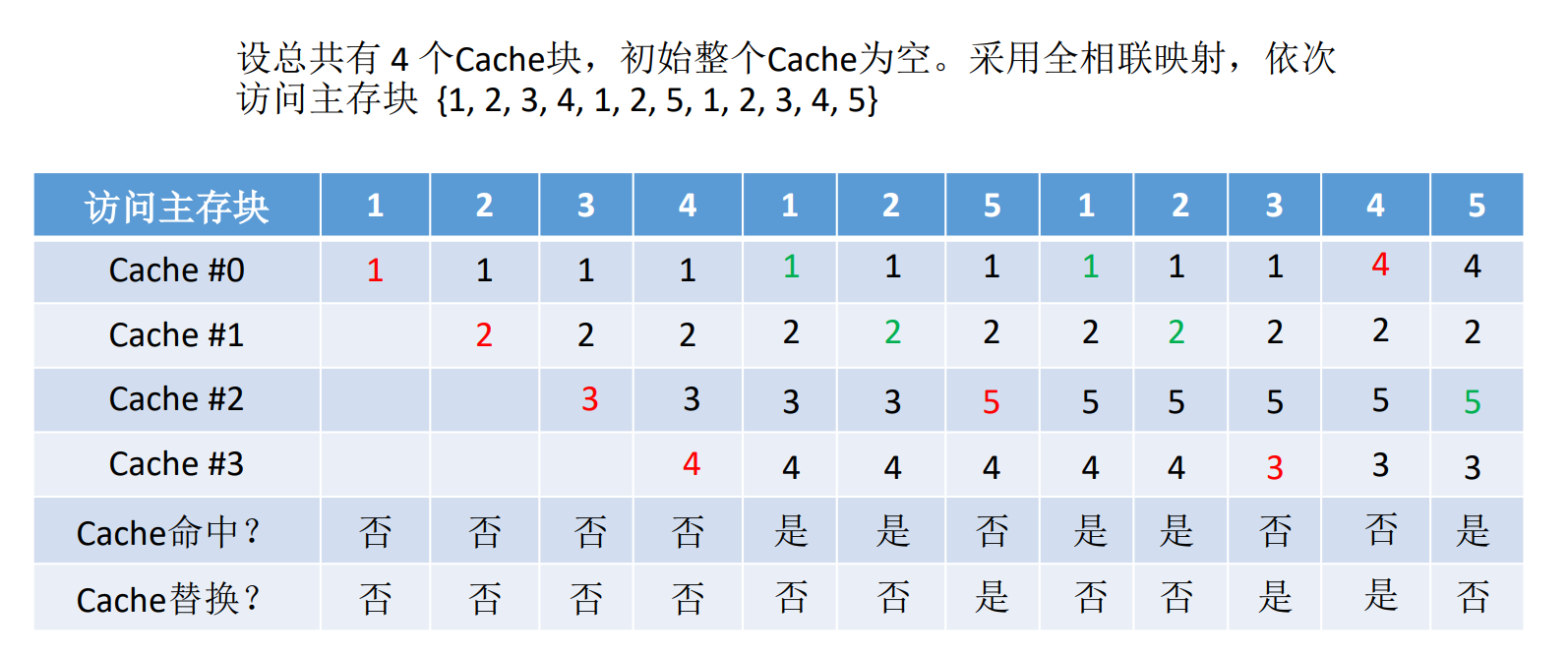

下面例子以全相联映射方式进行举例。

1.随机算法(RAND)

若Cache已满,则随机选择一块替换。

举例:

图中红色表示该位置被重新替换成新的块。

图中绿色表示命中该缓存块。

- 随即算法实现简单,但完全没考虑局部性原理(时间局部性),命中率低,实际效果很不稳定。

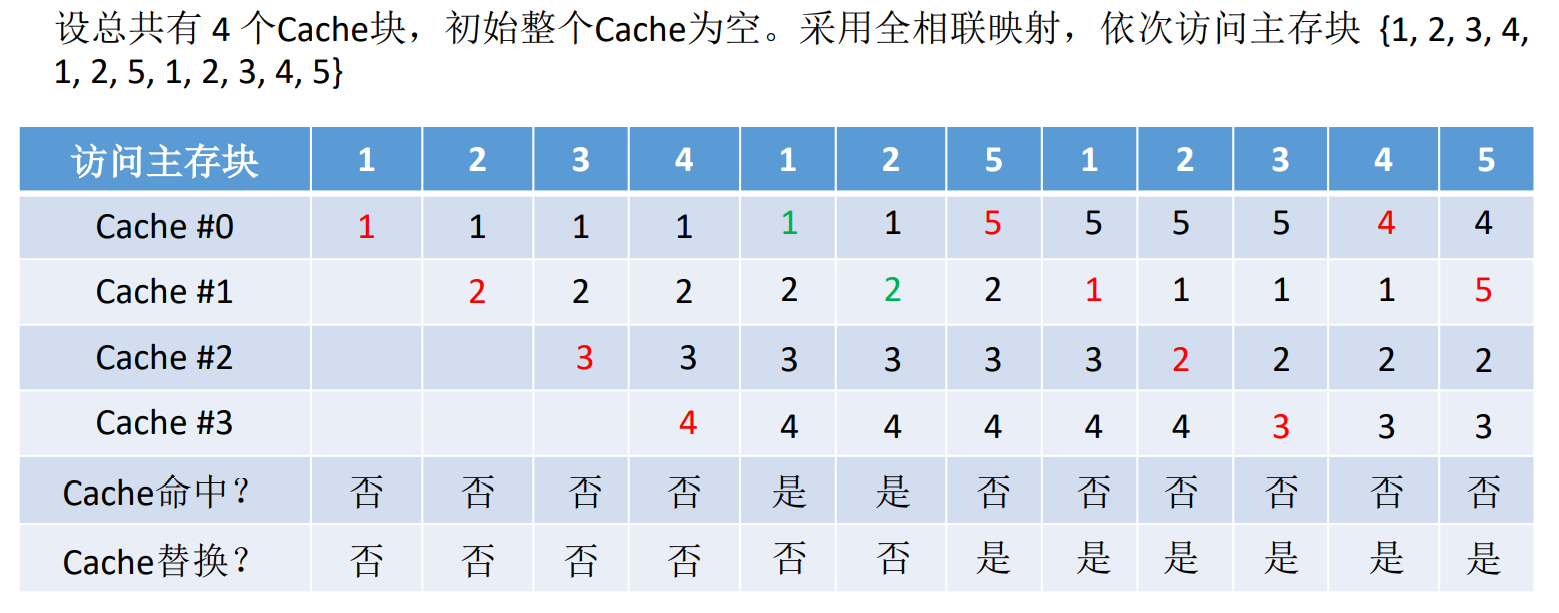

2.先进先出算法(FIFO)

- 若Cache已满,则替换最先被调入Cache的块。

举例:

从上图可以看到,红色出现很多次,这表明缓存块被频繁地替换,刚被替换的块很快又被重新调入,这称为抖动现象。

- 先进先出算法实现简单,但是依然没考虑局部性原理(时间局部性),因为最先被调入Cache的块也可能是被频繁访问的。

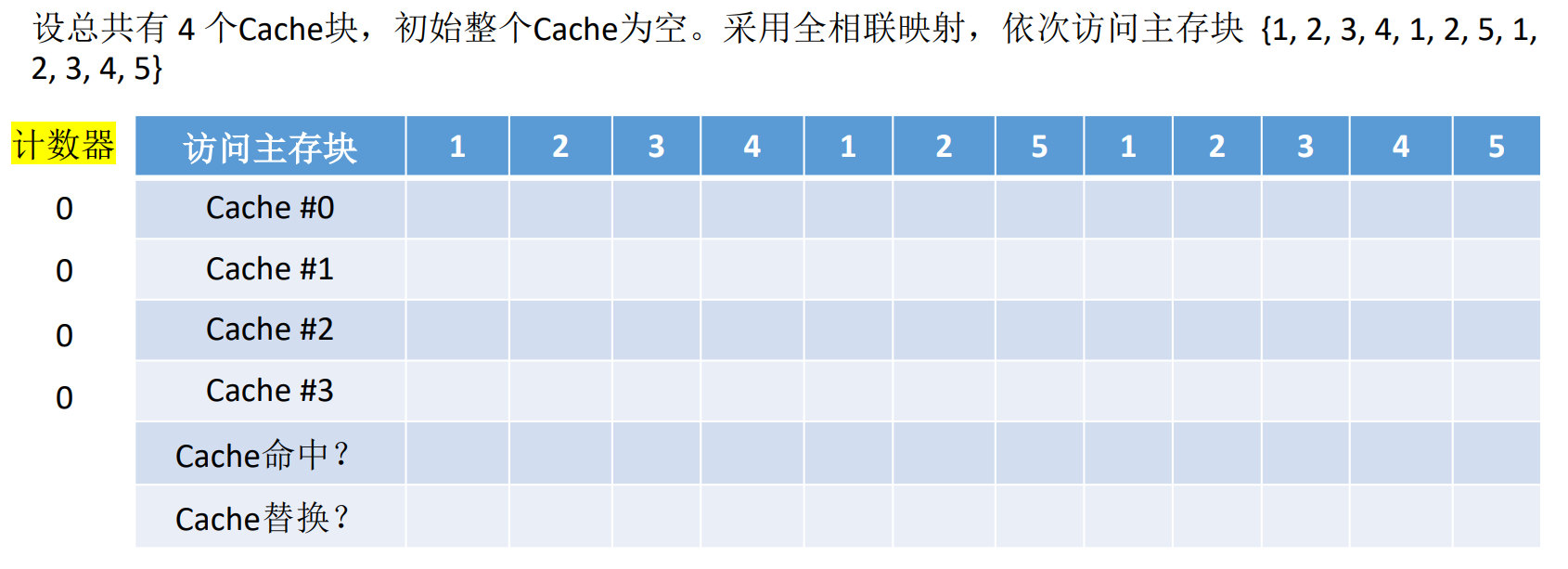

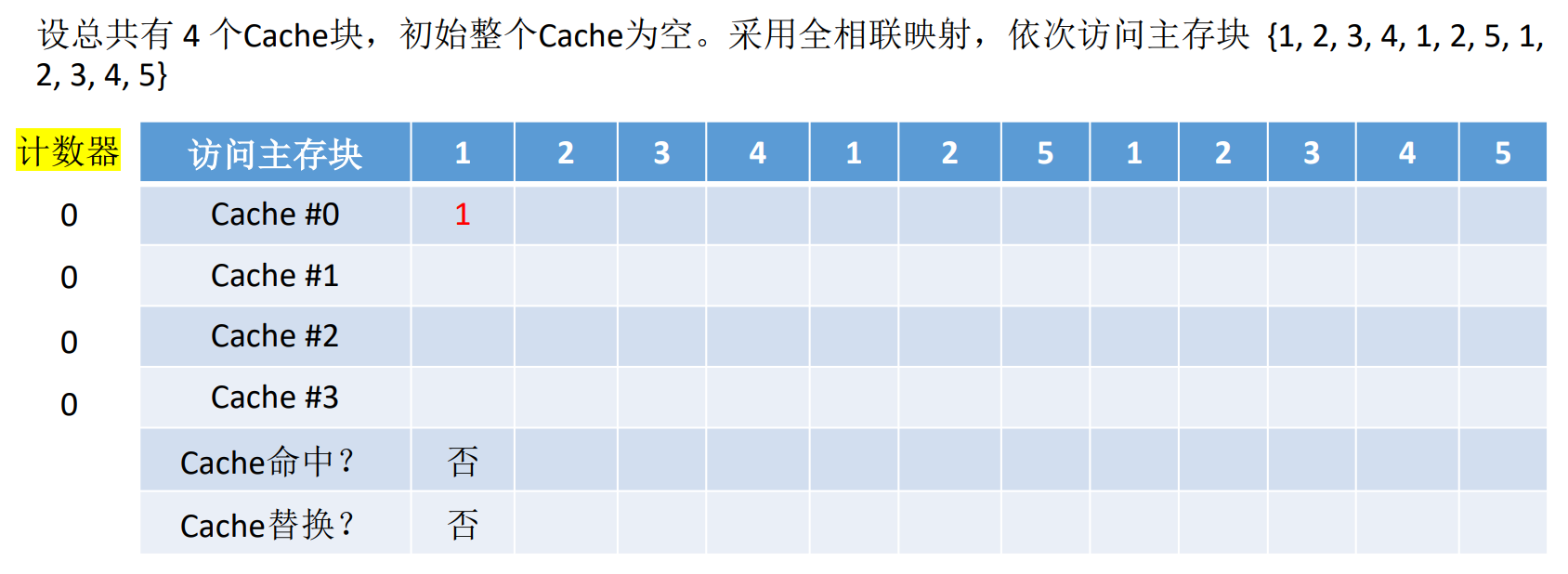

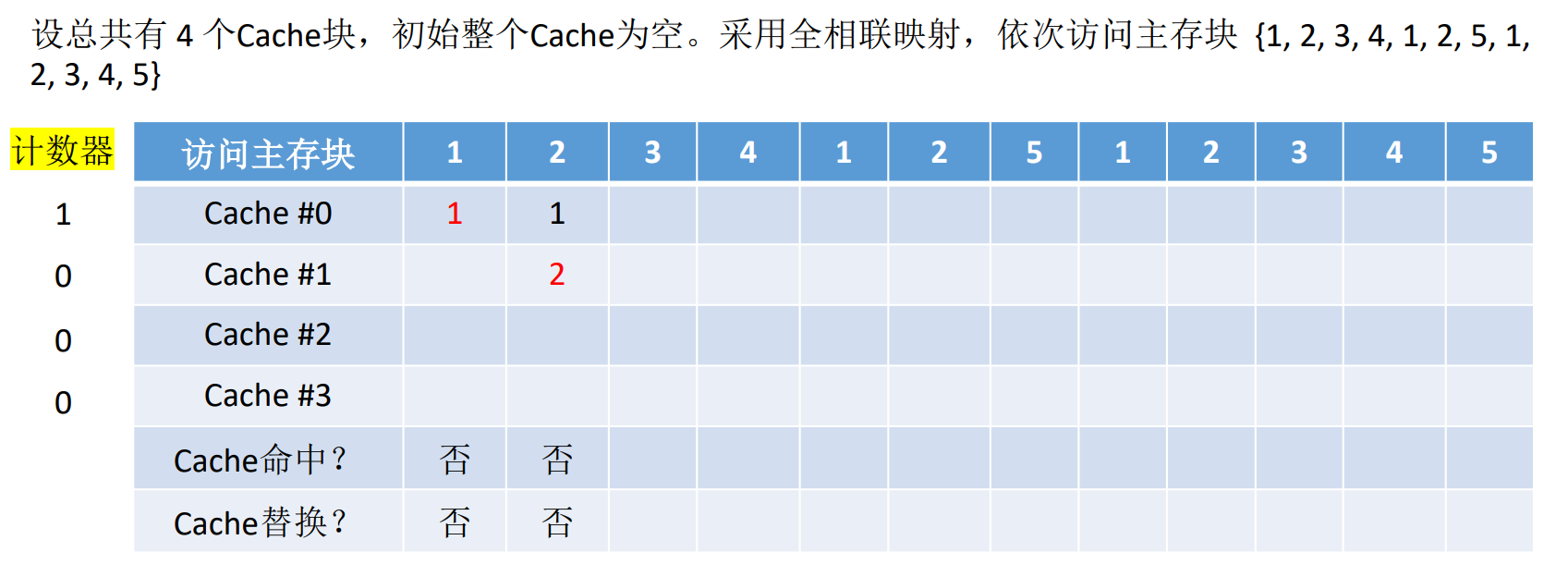

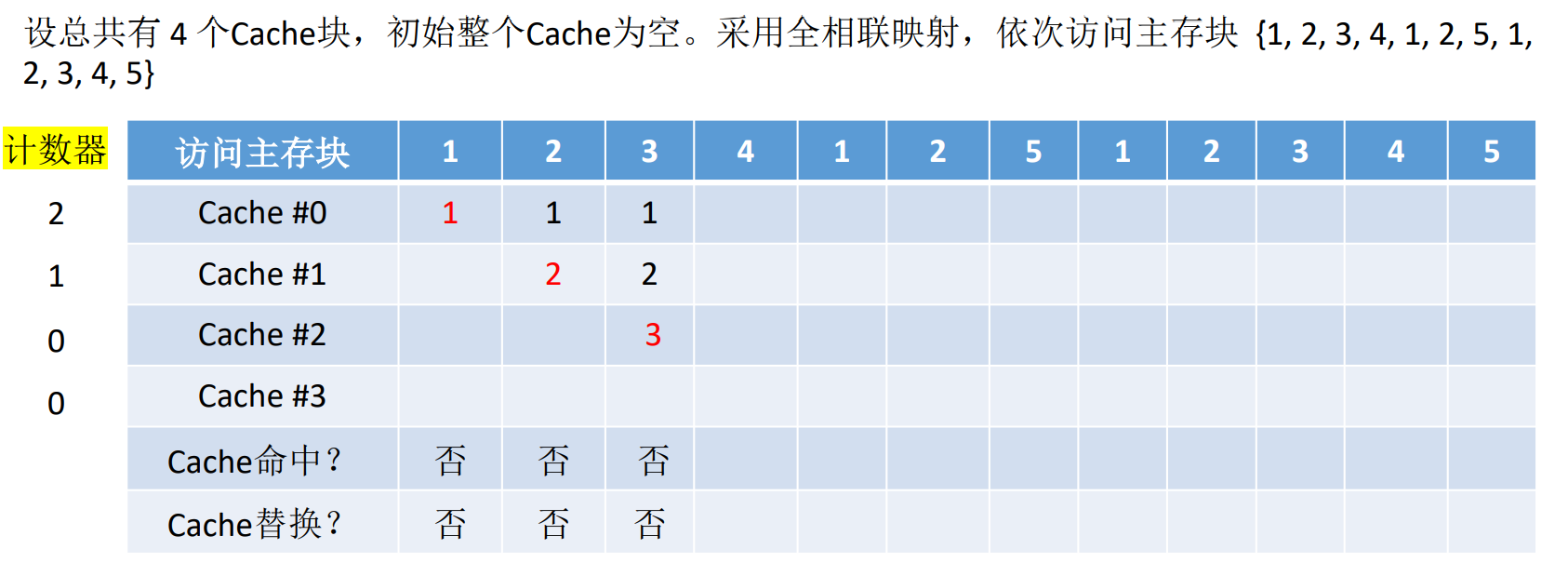

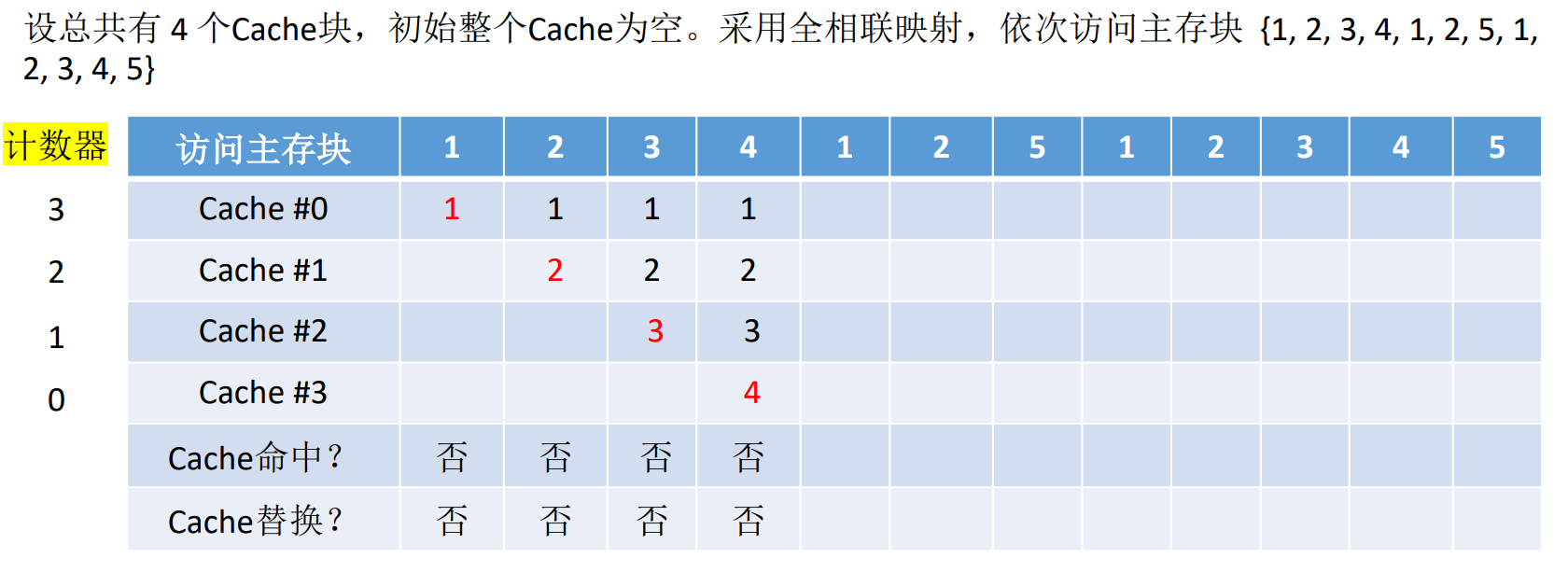

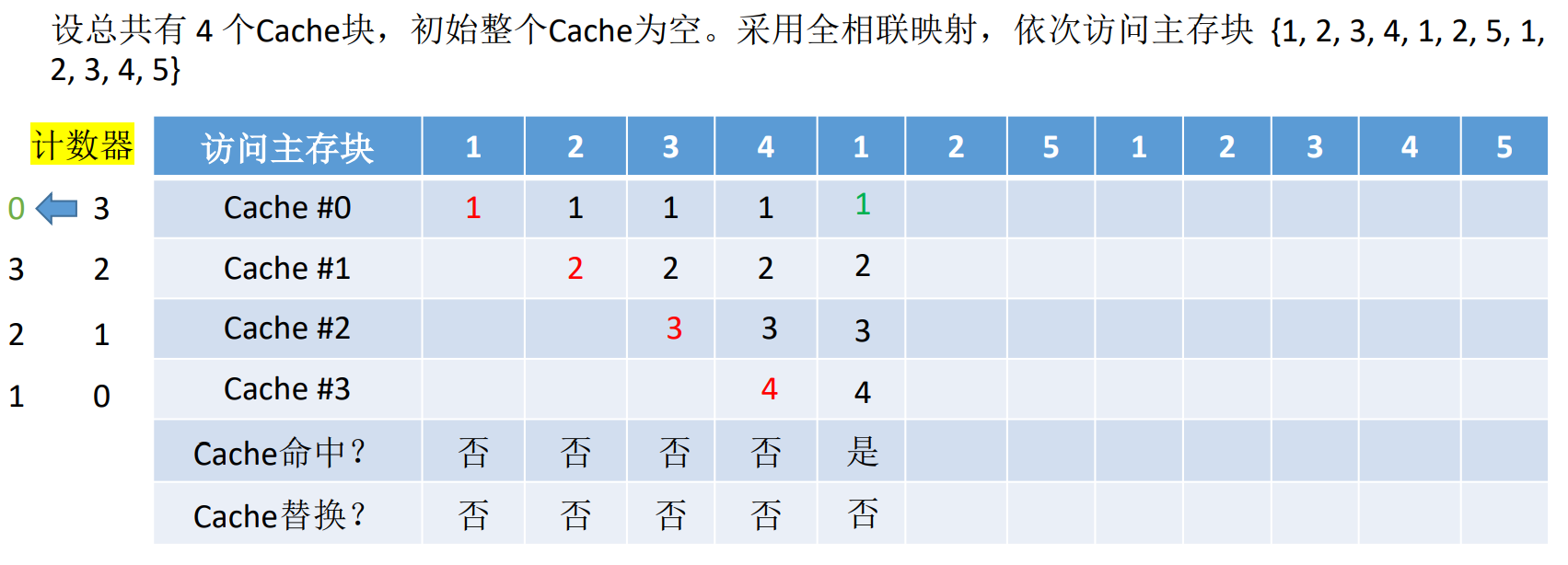

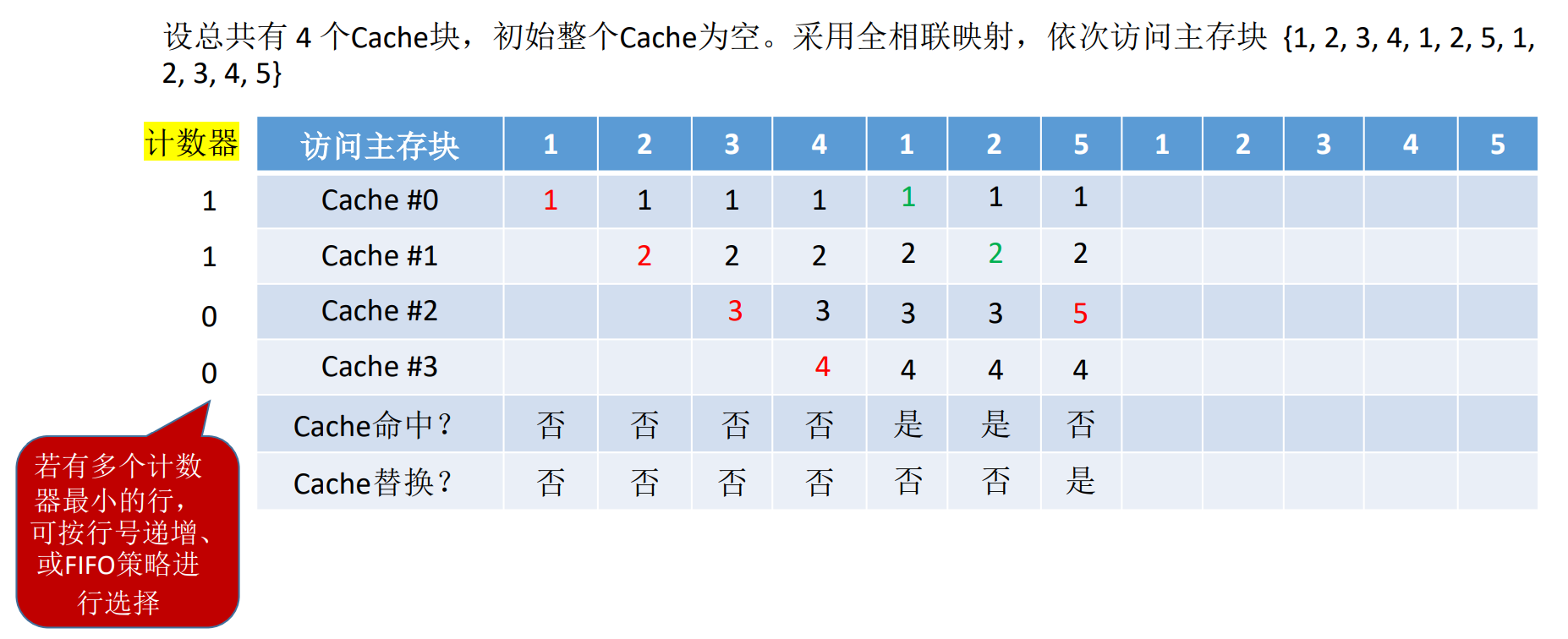

3.近期最少使用(LRU)

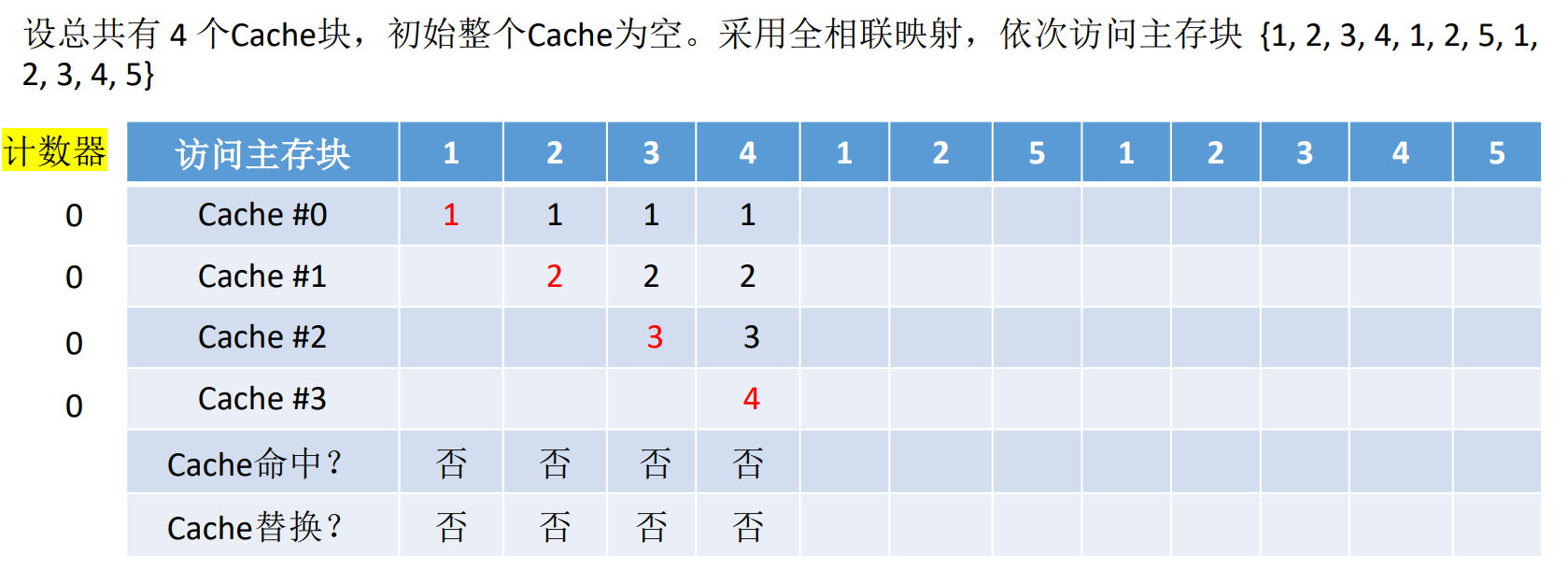

- 为每一个Cache块设置一个”计数器“,用于记录每个Cache块已经多久没被访问过了。当Cache满了之后替换”计数器“最大的。

- 计数规则:

- 命中时,所命中的行的计数器清零,比其低的计时器加1,其余不变(加一没有意义)。

- 未命中且还有空闲行时,新装入的行的计数器置0,其余非空闲行全加1。

- 未命中且没有空闲行时,计数值最大的行的信息块被淘汰,新装行的块的计数器置0,其余全加1。

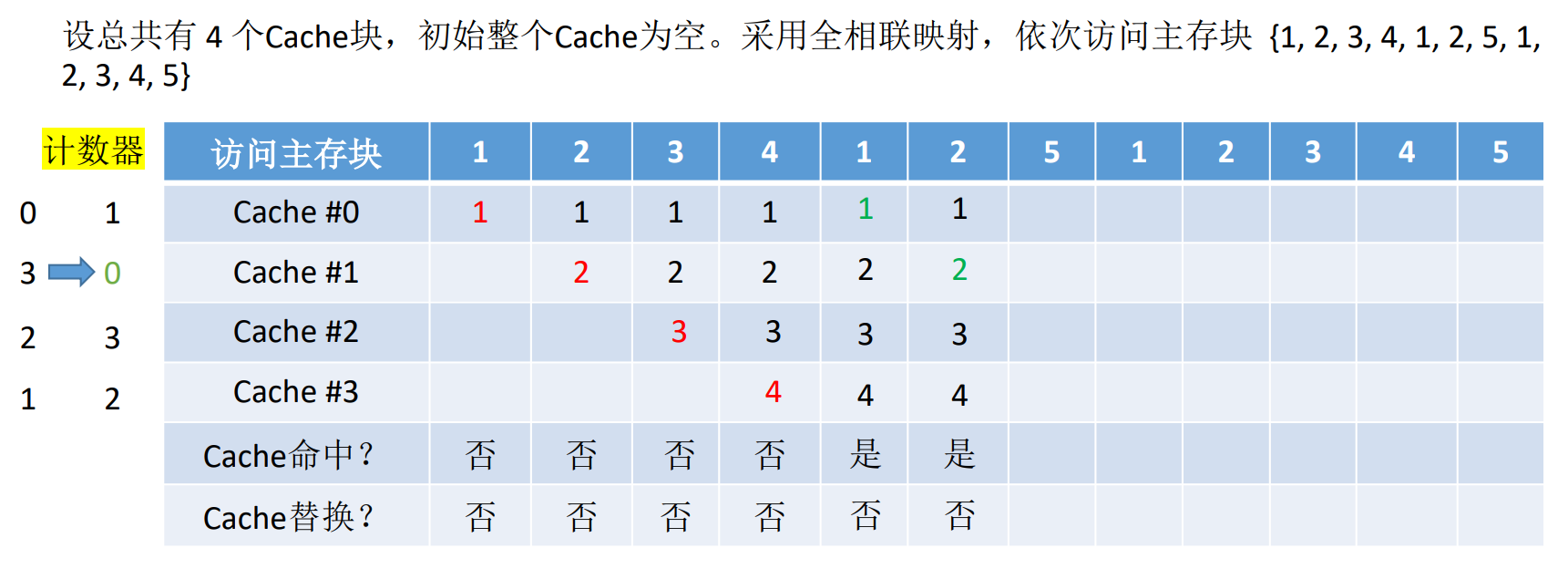

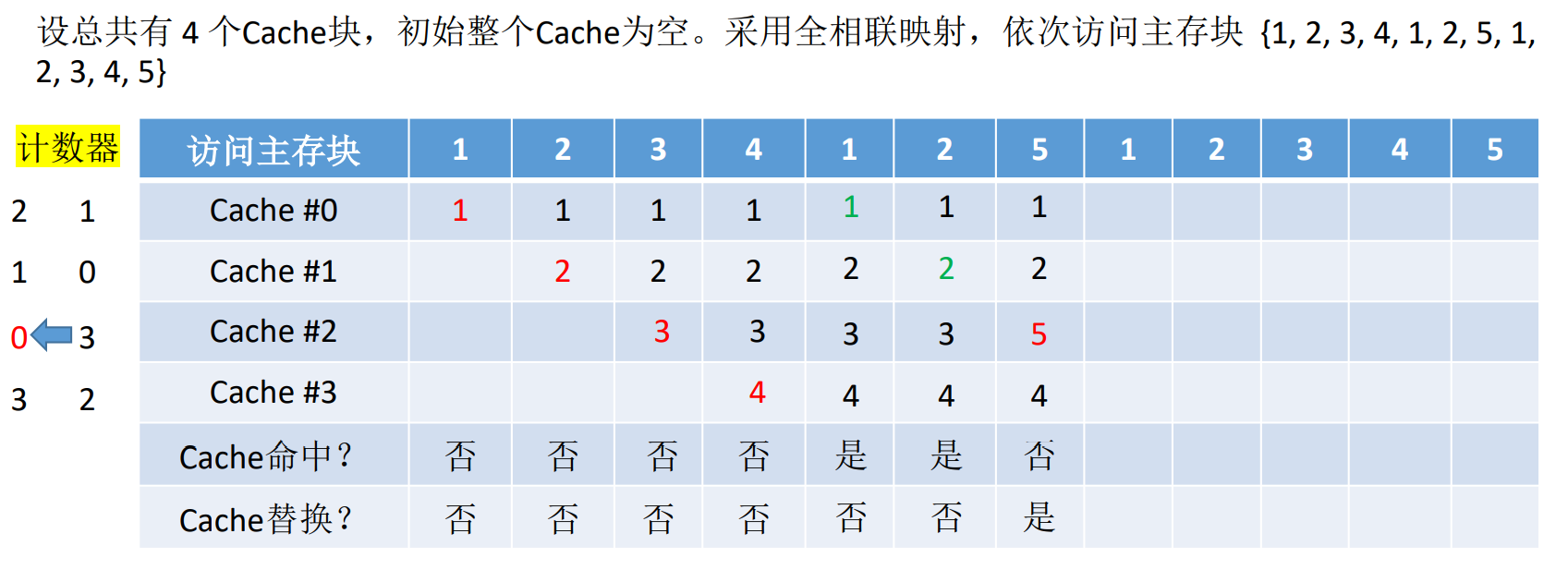

举例:

一开始,缓存块中并没有存储数据,计数器均为0。

访问主存块1

访问主存块2

访问主存块3

访问主存块4

访问主存块1,命中缓存,Cache0计数器重新清零

访问主存块2,命中,Cache1计数器重新清零

访问主存块5,此时未命中,将会采取下先进先出算法,替换计数值最大的块,图中替换Cache2

接下来的流程和上面类似,只需要根据计数规则自行模拟即可,这里不再赘述。

- 近期最少使用算法 基于 局部性原理,近期被访问过的主存块,在接下来的时间内很可能还会被访问,因此淘汰最久没被访问过的块是合理的,该算法实际运行效果优秀,Cache命中率很高。

- 若被频繁访问的主存块的数量 > Cache行的数量,则还是有可能发生抖动。

4.最近不经常使用(LFU)

为每一个Cache块设置一个”计数器“,用于记录每个Cache块被访问过几次。当Cache满后替换“计数值”最小的。

新调入的块计数器=0,之后每被访问过一次计数器+1。

举例:

访问了主存块1号,2号,3号,4号后,Cache的状态:

访问主存块1号和2号时均命中,Cache0和Cache1计数器加一。当访问主存块5号时,未命中,于是会替换计数值最小的Cache2(这里Cache2和Cache3均为0,会按行号递增或者FIFO策略来进行选择哪一个被替换)

接下来的流程和上面类似,根据 最不经常使用算法 自行模拟即可,这里不再赘述。

- 评价:曾经被经常访问的内存块在未来并不一定仍然被访问,并没有很好地遵循局部性原理(时间局部性原理),因此实际效果并不如 近期最少使用算法 LRU。

总结:

3.3.4 Cache写策略

知识总览:

为何不讨论读命中,读不命中的情况?

因为读不会导致主存和Cache的数据不一致。

1.写命中

(1)写回法:

当CPU对Cache写命中时,只修改Cache的内容,而不立即写入主存,只有当此Cache块被替换时才写回主存。

需要增加一位脏位,用于标记该Cache块是否被修改了。

减少了访存的次数,但存在数据不一致的隐患。

(2)全写法:

- 当CPU对Cache块写命中时,必须把数据同时写入Cache和主存中,一般使用写缓冲(write buffer)。

- 访存次数增加,速度变慢,但能保证数据的一致性。

- 使用写缓冲,CPU写的速度很快,若写操作不频繁,则效果很好,若写操作很频繁,可能会因为写缓冲饱和而发生阻塞。

2.写不命中

(1)写分配法:

- 当CPU对Cache写不命中时,把主存中的块调入Cache中,在Cache中修改,通常搭配写回法使用。也就是发生替换时才写回主存。

(2)非写分配法:

- 当CPU对Cache写不命中时,只写入主存,不调入Cache中。搭配全写法使用。

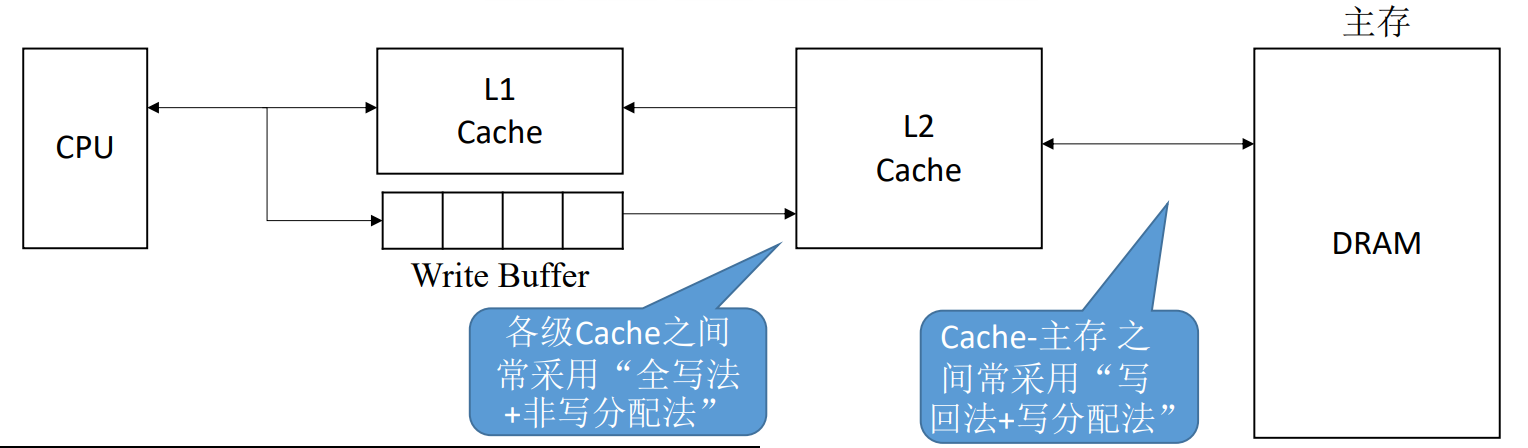

3.多级Cache

现代计算机常采用多级Cache:

离CPU越近的速度越快,容量越小

离CPU越远的速度越慢,容量越大。

各级Cache之间常采用 全写法 + 非写分配法。

Cache 和 主存 之间常采用 写回法 + 写分配法。

总结:

3.4 虚拟存储系统

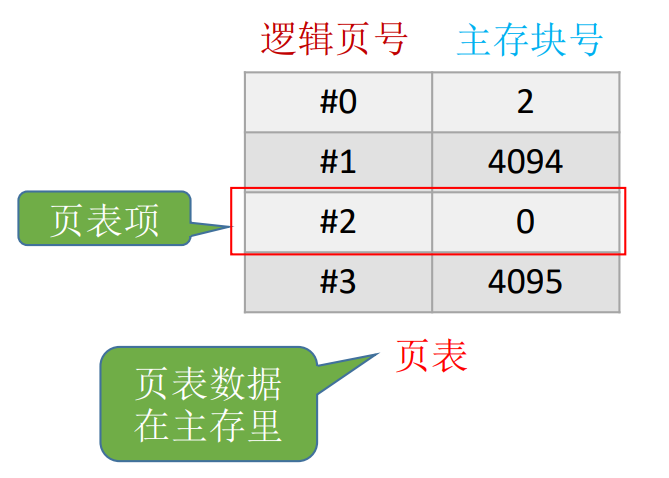

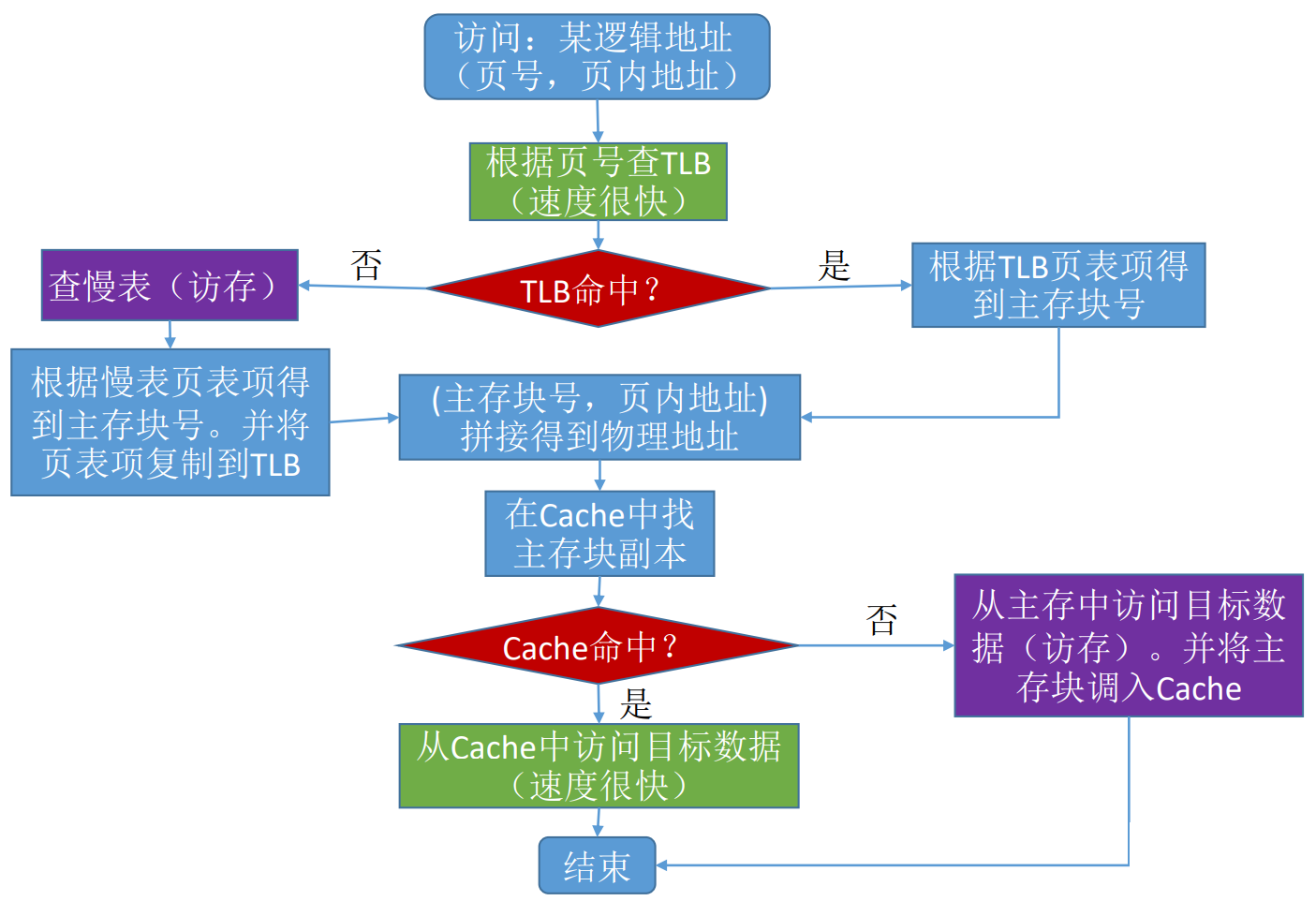

3.4.1 页式存储

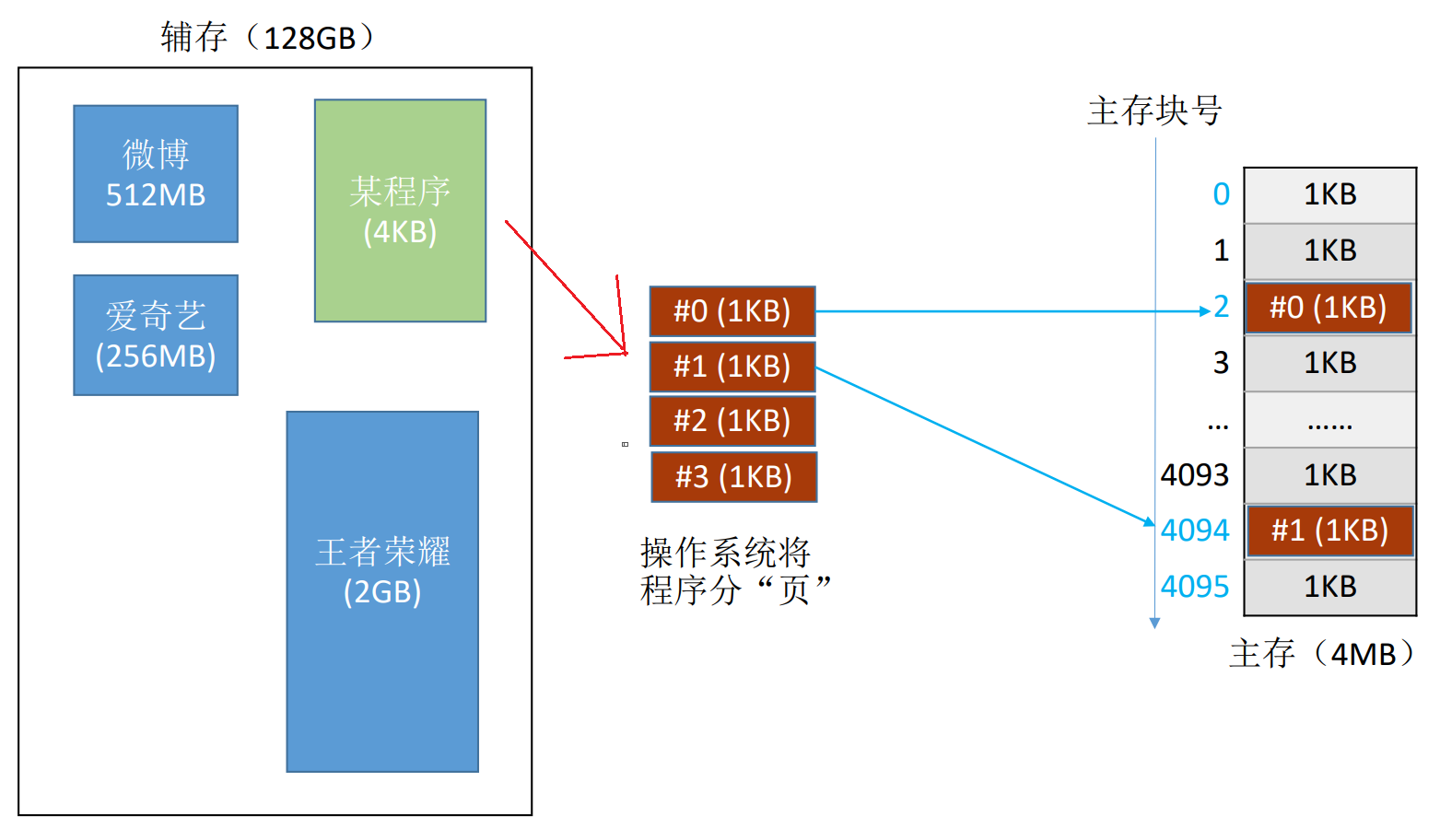

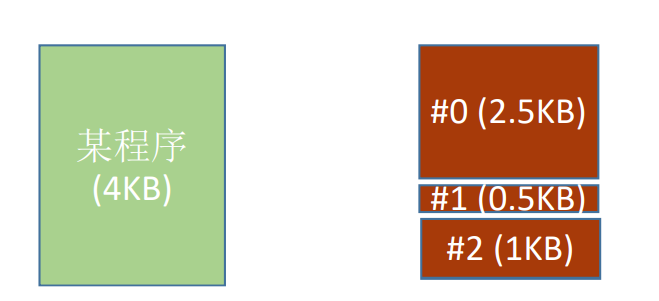

有时候一个程序比较大,无法将它顺序地存放在主存中的各个块中,因此操作系统会将它分成若干个页面,页面的大小和块的大小相同,每个页面可以离散地放入不同的主存块中。

逻辑地址(虚地址):程序员看到的地址。

物理地址(实地址):实际在主存中的地址。

对于一条机器指令:000001 001000000011(操作码+地址码),其地址码所使用的就是 逻辑地址。

页表:记录了每个逻辑页面存放在哪个主存块中,页表的数据放在主存中。

地址变换过程:举例

假设此时执行一条取指令操作,该指令为 000001 001000000011,所以要取的数据的逻辑地址为 001000000011

- 首先将逻辑地址拆分成 逻辑页号 和 页内地址。

- 在主存中找到 页表,然后通过 逻辑页号 进行查表,查出对应的 主存块号。

- 将 主存块号 拼接 页内地址 得到最终的 物理地址。

- 到Cache中查找该物理地址,找不到的话再到主存找。

但是由于页表是存放在主存中的,而根据时间局部性原理,刚使用的数据很可能在接下来还会使用,这样在下一次使用该数据时又得访问一次主存进行查表,为了更快地查表,会将近期访问的页表项放入更高速的存储器中,称为 快表。

**快表:**快表是一种相联存储器,可以按照内容进行寻访,并且其采用的是SRAM,访问速度更快。

快表 和 Cache 的区别:

- 快表 存储的是 页表项的副本

- cache 存储的是 主存块的副本

总结:

3.4.2 虚拟存储器

**虚拟存储系统:**辅存中的数据并不是一次性全部加载到主存中的,而是和 Cache——主存 类似,根据局部性原理加载一部分数据到主存中。

举例:打游戏时的“Loading”界面背后可能就是在 将游戏地图相关数据调入内存中。

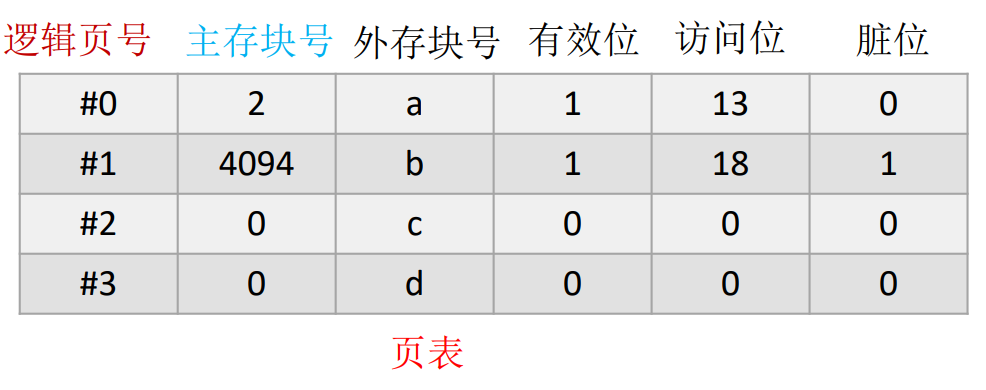

1.页式虚拟存储器

和Cache、主存类似,辅存中数据也被分为一个一个的块。

为了实现只加载一部分数据到主存中,需要对页表补充一些信息。

逻辑页号:逻辑地址中的页号

主存块号:物理地址中的主存块号

外存块号:辅存中对应的块号

有效位:这个页面是否被调入主存中

访问位:用于页面替换算法,主存也有用完的时候,需要进行替换,例如可以使用最不经常使用算法,统计访问次数。

脏位:这个页面是否被修改过,修改主存后会导致主存和辅存之间数据不一致。

由于主存和辅存之间的数据调入是由操作系统来调控的,因此具体细节请看操作系统相关内容,以上仅做粗略介绍。

- **主存——辅存:**实现虚拟存储系统,解决了主存容量不足的问题。

- **Cache——主存:**解决了主存和CPU之间速度不匹配的问题。

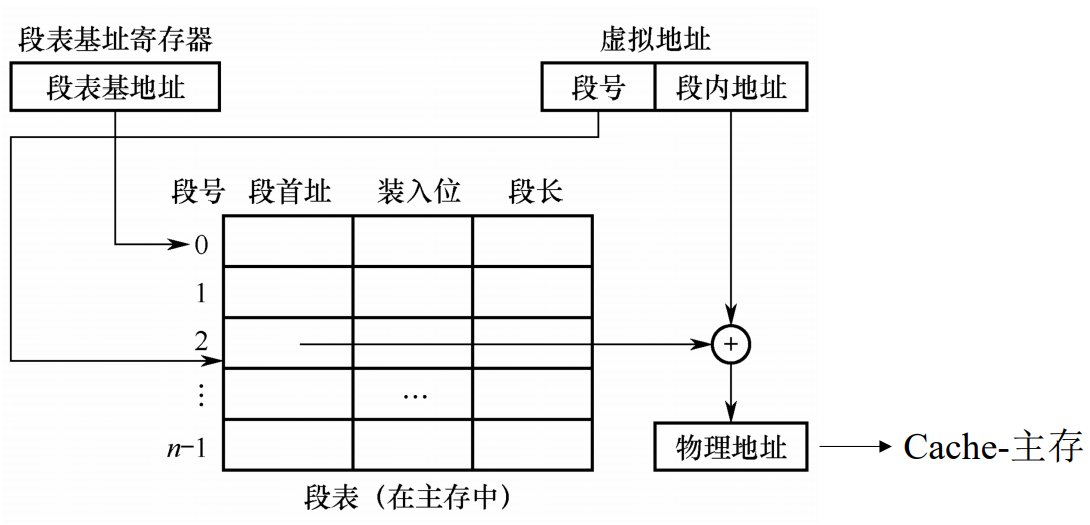

2.段式虚拟存储器

按照功能模块进行拆分。

例如:#0段是自己的代码,#1段是库函数的代码,#2段是变量。

和页式存储类似,操作系统以段为单位来决定哪一些段应该被调入内存中。

3.段页式虚拟存储器

把程序先按功能模块分段,每段再划分为固定大小的页,主存空间也划分为大小相等的页。

程序对主存的调入,调出仍然以页为基本传送单位,每个程序对应一个段表,每段对应一个页表。

虚拟地址:段号 + 段内页号 + 页内地址。

具体详情请看操作系统内容。

计算机组成原理——存储系统(超详细,必看!!)相关推荐

- sob攻略超详细攻略_2020云南旅游超详细必看攻略(附带云南美食景点攻略)

原标题:2020云南旅游超详细必看攻略(附带云南美食景点攻略) 云南,很多人首选的旅行目的地,云南的旅游景点多,而且也比较分散,建议大家先做好旅游攻略再出发吧,不然真的去到会很迷茫.也许有很多小伙伴是 ...

- 【Keras+计算机视觉+Tensorflow】OCR文字识别实战(附源码和数据集 超详细必看)

需要源码和数据集请点赞关注收藏后评论区留言私信~~~ 一.OCR文字识别简介 利用计算机自动识别字符的技术,是模式识别应用的一个重要领域.人们在生产和生活中,要处理大量的文字.报表和文本.为了减轻人们 ...

- 【机器学习】Rasa NLU以及Rasa Core概念和语法简介(超详细必看)

觉得有帮助请点赞关注收藏~~~ 一.Rasa简介 Rasa是一个开源机器学习框架,可以用于构建基于文本和语音的对话驱动型自动化智能客服助手,能够克服传统客服的部分缺陷,在Windows操作系统环境下, ...

- Java Web入门之JSTL标签的解析及使用(超详细必看)

创作不易 觉得有帮助或者想要实战源码可以点赞关注收藏后评论区留言 文章目录 前言 一.表达式标签 二.URL相关标签 三.流程控制标签 四.循环标签 总结 前言 JSTL叫做标准标签库 但实际上它是由 ...

- Android Studio App开发之网络通信中使用POST方式调用HTTP接口实现应用更新功能(附源码 超详细必看)

运行有问题或需要源码请点赞关注收藏后评论区留言~~~ 一.POST方式调用HTTP接口 POST方式把接口地址与请求报文分开,允许使用自定义的报文格式,由此扩大了该方式的应用场景.POST请求与GET ...

- 【云计算与大数据技术】Hadoop MapReduce的讲解(图文解释,超详细必看)

一.Hadoop MapReduce架构 MapReduce 是一种分布式计算框架,能够处理大量数据 ,并提供容错 .可靠等功能 , 运行部署在大规模计算集群中,MapReduce计算框架采用主从架构 ...

- 【Android App】检查手机连接WiFi信息以及扫描周围WiFi的讲解及实战(附源码和演示 超详细必看)

需要全部代码请点赞关注收藏后评论区留言私信~~~ 一.检查是否连接WiFi以及输出WiFi信息 传统的定位方式不适用于室内的垂直定位,原因如下: (1)卫星定位要求没有障碍物遮挡,它在户外比较精准,在 ...

- 【Android App】实战项目之仿微信的视频通话(附源码和演示 超详细必看)

需要源码请点赞关注收藏后评论区留言私信~~~ 虽然手机出现许多年了,它具备的功能也越来越丰富,但是最基本的通话功能几乎没有变化.从前使用固定电话的时候,通话就是听声音:如今使用最新的智能手机,通话仍旧 ...

- 计算机组成原理期末超详细复习

第一.二章 概论.计算机发展及应用 硬件:计算机中电子线路和物理装置,如主机.外设等 软件:计算机中全部程序和文件 软件分为系统软件和应用软件:系统软件是管理整个计算机系统的软件:应用软件时根据任务需 ...

- 【Python自然语言处理】隐马尔可夫模型中维特比(Viterbi)算法解决商务选择问题实战(附源码 超详细必看)

需要源码请点赞关注收藏后评论区留言私信~~~ 一.统计分词 统计分词基本逻辑是把每个词语看做由单字组成,利用统计学原理计算连接字在不同文本中出现的次数,以此判断相连字属于特定词语的概率. 二.隐马尔可 ...

最新文章

- Delphi中Chrome Chromium、Cef3学习笔记(二)

- 树(1)------实现和遍历

- 【Hadoop Summit Tokyo 2016】企业数据分类和治理

- 如何将html转为report,如何使用XtraReport将报表导出为HTML

- java list对象按照某个属性去重

- ORA-01403: no data found

- css3中的@font-face的用法(定义多个规则)

- 微型计算机原理与接口技术知识点

- LCL三相PWM整流器数学模型

- Python和R语言的区别

- IdPop3 出现 Max line length exceeded.的解决方法

- spark.reducer.maxReqsInFlight和spark.reducer.maxBlocksInFlightPerAddress

- [UVALive - 4329] Ping pong 树状数组入门

- 【PyTorch】关于函数 datasets.IMDB.splits()

- 使用Mongoose populate实现多表关联存储与查询,内附完整代码

- 治疗抑郁症,这款聊天机器人是认真的

- php上传二进制数据流

- unity实现太空场景

- 爱思助手安卓能用吗_专业的苹果越狱工具:爱思助手!

- Python集合和字符串及练习

热门文章

- 马自达css滑动按钮,css3实现的switch滑动开关按钮的效果

- java楼盘管理系统_基于Java的楼盘销售管理系统的设计与实现

- Java | 将文字生成在空白图片居中位置(根据图片大小,自动调节文字大小)

- CTFSHOW-phpCVE Writeup

- 北京地税数据复制容灾方案_SharePlex应用

- ChatGPT 被居心不良的人拿去搞黄色了...

- 【列空间(column spaces)】

- 概率论与数理统计初学印象(浙大四版+猴博士网课)

- erp5开源制造业erp价格引擎介绍

- agx 安装ros opencv_玩转软路由 篇二:虚拟机ESXI中Mikrotik RouterOS(ROS)的安装设置_路由器...