cordic ip核 vivado_Xilinx Vivado CORDIC IP核求解atan 反正切

赛灵思官方提供了cordic(coordinate rotational digital computer) ip核实现直角坐标极坐标变化,三角函数的操作。我介绍下它进行反正切求解的使用:

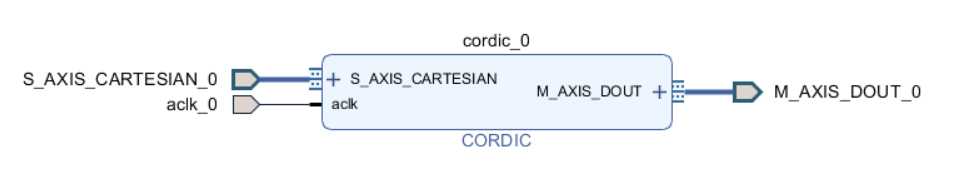

新建个简单工程:bd如下

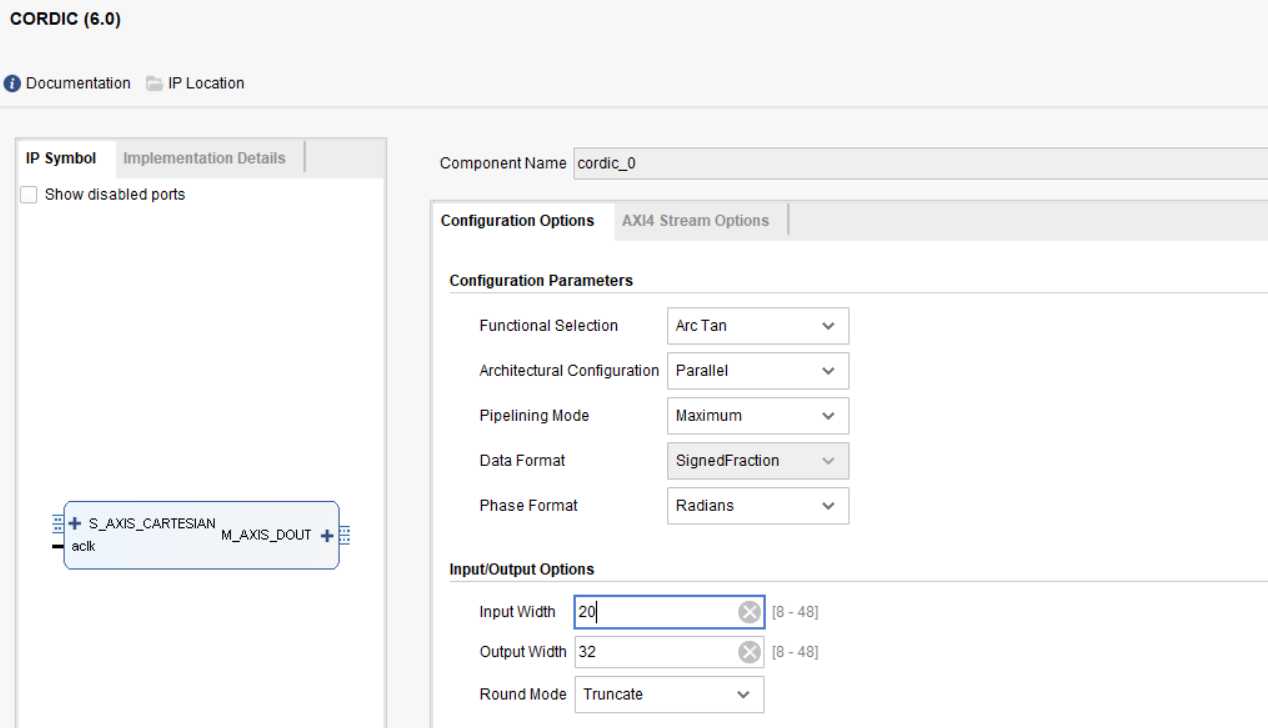

进行ip设置,选择运算位反正切后,ip端口回自动变为上图,再引出2个总线和时钟,xilinx的ip核不少是基于AXI4-Stream总线,这里使用并不复杂,默认只有2个信号,一个数据线tdata,一个握手信号tvalid,tvalid拉高时数据信号有效。

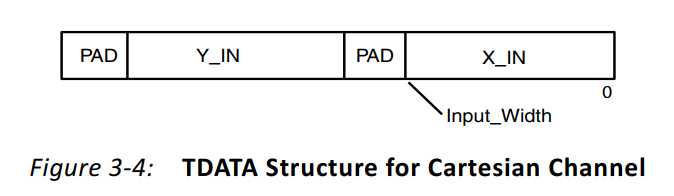

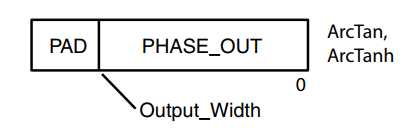

确定了输入输出位宽后,系统会自动求解出需要的延时latency。这里说一句,AXI-Stream总线收发基于byte的,无论输入什么位宽最后都是8的整数倍。所以需要参照UG,放置好有效输入位和分解输出位。

如果输入输出位宽恰好不是8的倍数,那么tdata位宽是大于设定的值的。所以需要上图提到进行填充(PAD),比如我输入20位,x和y加起来40位,那么输入S_AXIS的位宽是48,我要在0-19放x,20-23放填充数据(随意,我用0),24-43放y,44-47放填充数据。必须保证0-19和24-25分别是我的x和y。

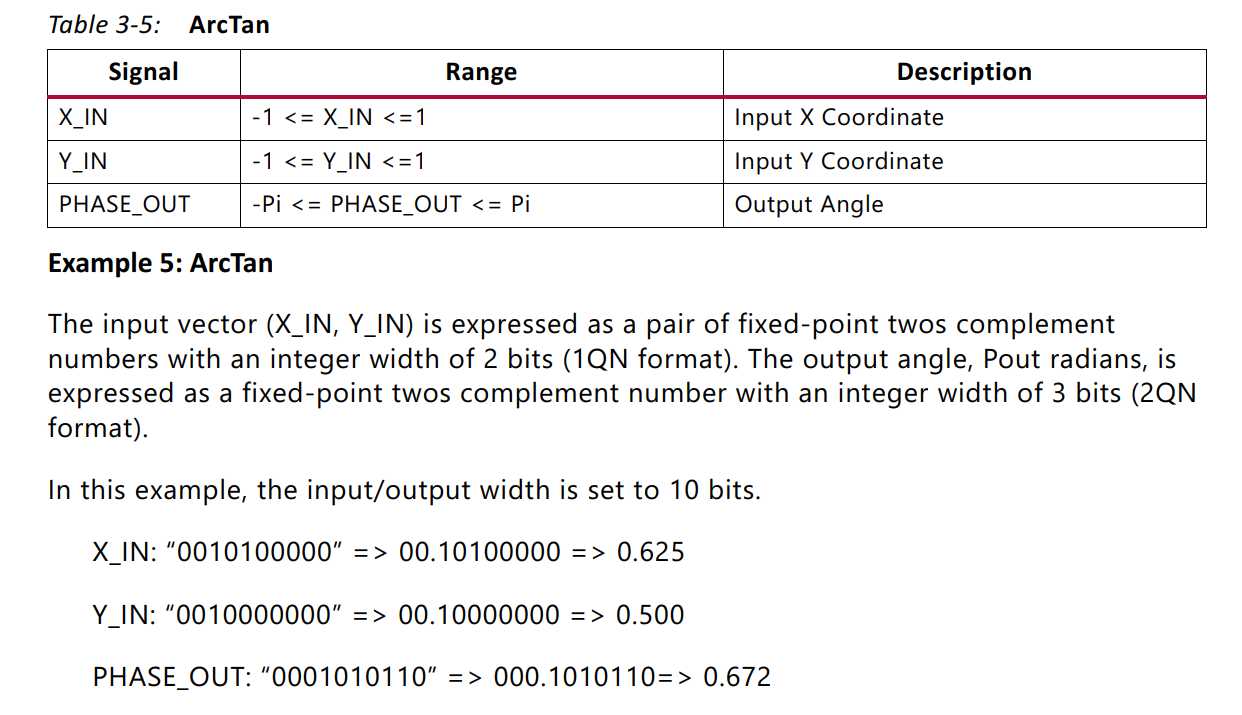

atan=y/x,要求输入必须是[-1,1],所以如果数据不是这个区间还需要进行归一化处理(可以用除法器div_gen ip核,这里不做介绍了)。上图是一个简单的示例,介绍输入输出的定点小数格式。整数部分的第一位是符号位,小数部分没有符号位是正的。

这里关于二进制小数表示,可以看下这个https://blog.csdn.net/AaricYang/article/details/87882868。整数的每一位权重是2^(n-1) 111就是2^2+2^1+2^0=7,小数部分的权重是2^(-n) 0.111就是2^(-1)+2^(-2)+2^(-3)=0.875

`timescale 1 ns / 1psmodulecordic_tb_top;regaclk;wire [31:0]M_AXIS_DOUT_0_tdata;wireM_AXIS_DOUT_0_tvalid;reg [47:0]S_AXIS_CARTESIAN_0_tdata;regS_AXIS_CARTESIAN_0_tvalid;integer handle;

initial beginaclk=0;

S_AXIS_CARTESIAN_0_tvalid=1‘b0;

S_AXIS_CARTESIAN_0_tdata=‘b0;

end

initial handle = $fopen("D:/FPGAcode/_file/cordic.txt");//打开文件

always #10 aclk=~aclk;localparam PAD=(48-20*2)/2;always@(posedge aclk) beginS_AXIS_CARTESIAN_0_tvalid<=1‘b1;

S_AXIS_CARTESIAN_0_tdata<={{PAD{1‘b0}},{3‘b000,17‘b0},{PAD{1‘b0}},{3‘b111,17‘b0}};end

always@(posedge aclk) begin

if(M_AXIS_DOUT_0_tvalid)

$fdisplay(handle,"%b",M_AXIS_DOUT_0_tdata);//写数据

enddesign_1_wrapper design_1_i

(.M_AXIS_DOUT_0_tdata(M_AXIS_DOUT_0_tdata),

.M_AXIS_DOUT_0_tvalid(M_AXIS_DOUT_0_tvalid),

.S_AXIS_CARTESIAN_0_tdata(S_AXIS_CARTESIAN_0_tdata),

.S_AXIS_CARTESIAN_0_tvalid(S_AXIS_CARTESIAN_0_tvalid),

.aclk_0(aclk));endmodule

给个简单的testbench

如果自己参考文献,用HDL实现一个CORDIC算法的模块,应该是很不错了。但是我偷懒直接用现成IP了

cordic ip核 vivado_Xilinx Vivado CORDIC IP核求解atan 反正切相关推荐

- cordic ip核 vivado_Xilinx Vivado CORDIC IP求解atan 反正切

赛灵思官方提供了cordic(coordinate rotational digital computer) ip核实现直角坐标极坐标变化,三角函数的操作.我介绍下它进行反正切求解的使用: 新建个简单 ...

- Xilinx vivado 常用IP核使用

目录 1. Accumulator 12.0 2. Aurora 8B10B 11.1 3. Clocking Wizard 3.1. 时钟资源 4. Divider Generator 5.1 5. ...

- 使用vivado封装IP

文章目录 Basics 定制IP的参数 Enablement Expression 封装IP时使用了绝对路径 封装IP时设置Address Map Addr 相关tcl 修正警告 Bus Interf ...

- vivado CORDIC ip核计算arctan记录

文章目录 前言 一.CORDIC ip核配置 二.CORDIC ip核接口 三.仿真波形 四.工程文件 前言 本文主要记录自己使用vivado CORDIC ip 核计算arctan的过程. 一.CO ...

- cordic ip核 vivado_vivado中Cordic IP核使用——计算正余弦(sin/cos)

目录 1.Cordic算法介绍 2.Cordic IP核介绍 3.仿真 4.存在的问题 5.参考 1.Cordic算法介绍 cordic算法将正余弦计算转换为简单的迭代过程(一系列的加减和移位操作), ...

- vivado cordic IP学习记录

一.QN格式(Q数据格式) XQN格式数据,是一个1bit符号位+X bits整数位+N bits小数位的补码数据.可表达的数据的范围是, 比如Q15,指的是X=0,N=15的Q格式数据,加上符号位合 ...

- Vivado FIFO IP核接口信号介绍

1.1 Vivado FIFO IP核接口信号介绍 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)Vivado FIFO IP核接口信号介绍: 5)结束语. 1.1.2 ...

- Vivado MMCM IP核接口信号介绍

1.1 Vivado MMCM IP核接口信号介绍 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)Vivado MMCM IP核接口信号介绍: 5)结束语. 1.1.2 ...

- vivado dds IP核笔记

vivado dds IP核笔记 DDS IP核在vivado提供的GUI界面中,可以选择三种配置: Phase Generator and SIN/COS LUT (DDS) SIN/COS LUT ...

- vivado ROM IP核简单使用

vivado ROM IP核简单使用 vivado配置 下面选择数据的存储深度和数据的位宽 ROM内存储的数据由coe文件初始化 下面是初始化coe文件的内容 memory_initializatio ...

最新文章

- 数据分析之CE找数据大法

- ubuntu+2080ti系统用anaconda 安装tensorflow

- 在Windows平台如何选择C语言编译器?

- 取得Access自增标识字段在插入数据后的id值

- vba quit此文件正由另一个应用程序或用户使用_VBA|如何添加外部对象库(或控件)引用来扩展VBA功能...

- centos / Linux 服务环境下安装 Redis 5.0.3

- map容器find用法

- php+mysql执行sql文件路径_PHP———MySQL笔记(5)之MySQL数据库导出导入sql文件(详细)...

- 台达DVP PLC与西门子V20变频器通讯案例台达PLC西门子变频器通讯

- 小型即时通讯软件-C#

- Thinkpad笔记本电池保养

- 转载:解决微信OAuth2.0网页授权回调域名只能设置一个的问题

- 阐明iOS证书和provision文件

- 【临侦探侦工作原理】

- 【OpenCV】- 图像修复

- 大型项目前端架构浅谈(8000字原创首发)

- Win10日历便签怎么设置定时提醒

- unity 实现3d模型渐隐(修改材质透明度)

- java signal信号_signal 信号具体含义解释~

- 他是世界上最伟大的程序员,65岁求职被歧视,一生热爱技术!

热门文章

- 业界 | 摩根大通报告12个亮点总结:金融领域的机器学习工具有哪些?

- 帝国CMS7.5忘记后台密码怎么找回

- 数学函数最小值为什么可以通过导数=0来求出呢?

- 具有聚集诱导发射(AIE)特性的新型TADF分子SBF-BP-DMAC的定制合成

- 局域网内ping不通另外一台电脑_疫情期间宅家一台电脑如何做计算机网络实验...

- 阿里云华北1235、华东1、华东2和华南1分别对应哪些城市?地域节点物理数据中心在哪?...

- 重装系统后office去哪里安装?

- Xilinx火龙果学习笔记(1)---初识火龙果

- 施努卡:机器视觉公司排名(机器人视觉系统)

- C语言任意输入三个数构成三角形,随便输入三个数,看能否组成一个三角形