SPI总线接口与简单配置

SPI 总线接口

SPI总线主要由4条线组成:

n SCLK —Serial Clock (output from master)

n MOSI/SIMO —Master Output, Slave Input (output from master)

n MISO/SOMI —Master Input, Slave Output (output from slave)

n SS — Slave Select (active low; output from master)

有另一种命名方式也经常可见:

n SCK — Serial Clock (output from master)

n SDI, DI, SI — Serial Data In

n SDO, DO, SO — Serial Data Out

n nCS, CS, nSS, STE — Chip Select, Slave Transmit Enable (active low; output from master)

SPI通讯时Master首先需要配置一个时钟(clock),这个值一般选择小于或者大于Slave设备支持的频率。 通用的频率范围为1-70MHz。

SPI工作在全双工模式,这意味着数据可以在同一时间发送和接收。

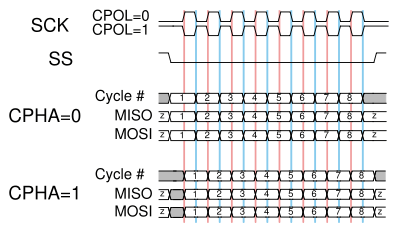

时钟极性polarity与时钟相位phase

时钟极性(CPOL)和时钟相位(CPHA)用于设定从设备何时采样数据。CPOL决定SCLK为高时总线为空闲(CPOL=1)还是SCLK为低时总线为空闲(CPOL=0)。CPHA决定在SCLK的哪一个边沿将数据写入。

按照下面的时序图,

CPOL=0, SCLK为低时总线空闲:

CPHA=0 数据在SCLK的上升沿(rising edge)被读取;数据在下降沿(falling edge)写入;

CPHA=1 数据在SCLK的下降沿(falling edge)被读取;数据在上升沿(rising edge)写入;

CPOL=1, SCLK为高时总线空闲:

CPHA=0 数据在SCLK的下降沿(falling edge)被读取;数据在上升沿(falling edge)写入;

CPHA=1 数据在SCLK的上升沿(falling edge)被读取;数据在下降沿(rising edge)写入;

以下是时序图:

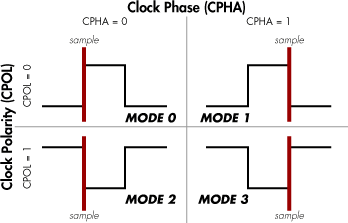

CPOL和CPHA的两个状态允许四种时钟极性和相位的不同组合。每一种都与其他三种不兼容。为了实现主、从设备间的通讯,主、从设备的CPOL和CPHA必须有相同的设置。以下是CPOL,CPHA与4种模式的关系图。

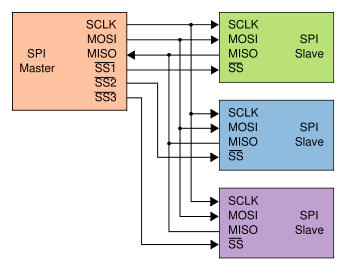

SPI的菊花链配置

一个Master 与3个独立的Slave组合, 每个Slave都有一个独立的SS(Slave Select)。

一个Master与一组使用公用SS(Slave Select)的Slave组合。

以AD7873为例做一些SPI的典型的设置

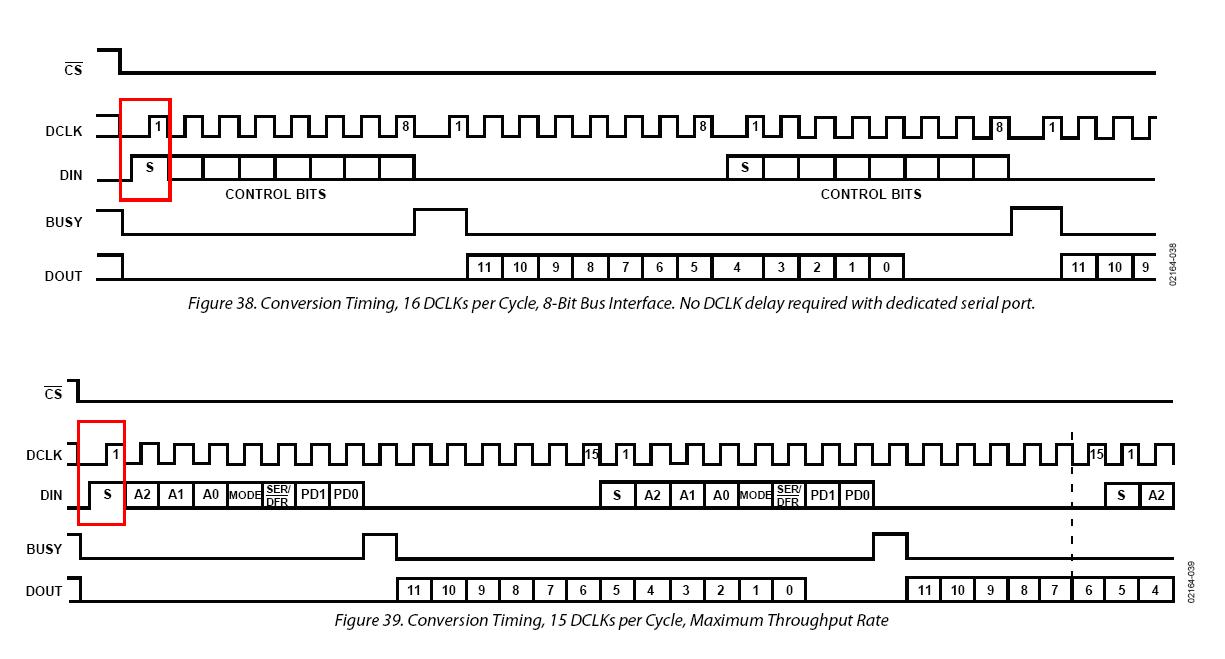

根据时序图,当CS变成低电平时,DCLK为低电平空闲,DIN在DCLK的上升沿数据锁存.所以SPI的polarity与phase设置为Mode 0。

Figure 38 -SPI设置为8bits通信模式,通信周期分为3个阶段:

1> DCLK前8个DCLK对应指令周期。在这8个DCLK中,通过DIN向AD7873发送8bits命令字控制随后进行的串行数据传输。

2> 数据传输周期从第9个上升沿开始,输入数据在时钟上升沿写入,输出的数据则在时钟的下降沿读出。这里的输入数据为8bits的0数据。DOUT同时也从DCLK的第10个上升沿开始数据输出,到第二个DCLK周期结束时,DOUT输出位数为7bits。

3> 重新开始8个DCLK的指令周期,继续通过DIN传送8bits命令控制字,同时DOUT在第17个DCLK输出最后的5bits数据。

可见在Figure 38中8bits数据通信模式下,AD7873要完成一个完整的SPI数据读写,需要3个周期,即发送24bits数据才能达到目标。

Figure 39 -SPI设置为15bits通信模式,通信周期分为2个阶段:

1> DCLK前15个DCLK对应指令周期。在这15个DCLK中,通过DIN向AD7873发送15bits命令字控制随后进行的串行数据传输(MSB 8bits为命令字, LSB 7bits为数据0)。DOUT同时也从DCLK的第9个上升沿开始数据输出,第一次15 DLCK周期结束时,DOUT输出位数为MSB 6bits。

2> 重新开始15个DCLK的指令周期,继续通过DIN传送15bits命令控制字。同时DOUT在第16个DCLK输出最后的LSB 6bits数据。

可见在Figure 39中8bits数据通信模式下,AD7873要完成一个完整的SPI数据读写,需要2个周期,即发送30bits 数据才能达到目标。

可见Figure 38使用的DCLK最少,效率最高。不过再8bits传送模式下需要采用连续发送3次8bits数据方式。

如果SPI想在一个周期内一次性将数据读取上来,可以把SPI通信设置为 传送bits>= DIN+DOUT所需的时钟数目,这里根据时序图为22个DCLK。 就可以在22个DCLK中一次性完成写8bits的命令字与读12bits的数据了。不过这里的8bits命令字是22bits中的 MSB 8bits。

不过此方法就没有上面两种通信模式的效率高了。:-)

以Freescale i.mx系列CSPI作为例:

采用CSPI1,POL=0,PHA=0,BIT_COUNT=22

CSPI1_CONTROL.bits.EN=1

CSPI1_CONTROL.bits.MODE=1

CSPI1_CONTROL.bits.POL = 0

CSPI1_CONTROL.bits.PHA = 0

CSPI1_CONTROL.bits.BIT_COUNT= 22

参考资料

1.Serial Peripheral Interface Bus

2.SPI Background

2008-05-21 修改

SPI总线接口与简单配置相关推荐

- Ip网络技术组建--hybrid混合接口的简单配置例子

hybrid混合接口的简单配置例子 新手上路请多关照,仅以该篇作为自己的学习记录,如有问题,还请不吝赐教,谢谢! 注:本实验配置基于华为设备,以百兆网口设备为例. 上图为混合配置的图例,其中pc1.p ...

- SPI协议、MCP2515裸机驱动详解----主流SPI总线接口原理

最近看到一个介绍SPI接口原理的帖子,看完觉得甚好.特来分析给大家一起学习. SPI概述 Serial Peripheral interface 通用串行外围设备接口 是Motorola首先在其MC6 ...

- 了解SPI总线CAN控制器 MCP2515配置 一文即可

1.引言 最近工作中遇到需要6路CAN通信的情况,单片机自带的4路已不满足实际需求,故采用了SPI总线的CAN控制器芯片MCP2515,通过SPI通信的CAN扩展芯片最高可实现1Mbps的遵循CAN ...

- 单片机软件模拟SPI接口—加深理解SPI总线协议

单片机软件模拟SPI接口-加深理解SPI总线协议 SPI(Serial Peripheral Interfacer 串行外设接口)是摩托罗拉公司推出的一种同步串行通讯接口,用于微处理器臌控制器和外 ...

- SPI总线之CPOL CPHA(转)

[背景] 最近在看关于Silicon Labs的C8051F347的某个驱动中,关于SPI部分初始化的代码,看到其对于SPI的设置为CPOL=1,CPHA=0,对于CPOL及CPHA的含义不了解,想要 ...

- SPI总线时钟的极性(CPOL)与相位(CPHA)

文章来源:转来转去的不知道是谁的了.. SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间.即一 ...

- SPI总线的特点、工作方式及常见错误解答重点是SCK时钟频率时间

4.1 SPR设定错误 在从器件时钟频率小于主器件时钟频率时,如果SCK的速率设得太快,将导致接收到的数据不正确(SPI接口本身难以判断收到的数据是否正确,要在软件中处理). 整个系统的速度受三个因素 ...

- 【SPI总线常见错误】

SPI总线常见错误 1 SPR设定错误 在从器件时钟频率小于主器件时钟频率时,如果SCK的速率设得太快,将导致接收到的数据不正确(SPI接口本身难以判断收到的数据是否正确,要在软件中处理). 整个系统 ...

- SPI总线传输的4种模式

概述 在芯片的资料上,有两个非常特殊的寄存器配置位,分别是 CPOL (Clock POlarity)和 CPHA (Clock PHAse). CPOL配置SPI总线的极性 CPHA配置SPI总线的 ...

- SPI协议概括、SPI总线工作的四种方式和SPI接口时序

SPI协议概括: SPI总线是一种4线总线,因其硬件功能很强,所以与SPI有关的软件就相当简单,使中央处理器(Central Processing Unit,CPU)有更多的时间处理其他事务.正是因为 ...

最新文章

- java socket同步通信,javasocket客户端与服务端同步通信实例

- 杯具,丢失了一部分邮件

- 1032 Sharing (25 分) 【难度: 一般 / 知识点: 链表】

- 现代谱估计:多窗口谱

- linux主从服务器不能同步,Linux下redis的持久化、主从同步与哨兵详解

- 使用GoldenGate进行平台迁移和数据库升级(9i-11g)步骤描述

- 【剑指offer】——【python中return函数中的and和or表达式的返回值】

- Oracle DG常用视图与运维护常用操作

- STM32 USB数据接收与数据发送程序流程分析

- cacti-0.8.8a那点儿事

- ActiveMQ_Linux安装

- 解决Ubuntu18.04下VLC打不开的问题

- php下载apk文件源码下载,php文件下载功能简单源码示例

- java layer调用native层的android_media_AudioTrack_get_min_buff_size()确定audio track buffer的min size...

- 动易2007后台模板上传任意文件漏洞

- 基于SSH开发教务排课系统

- get与post的区别

- Vue 简单人脸识别

- 谈一谈post和get的区别

- COMSOL和Matlab联合仿真之复合材料填充建模

热门文章

- BZOJ3517 翻硬币

- php 和 java_Java和php怎么选择??

- linux下槽函数的响应时间,Qt信号与槽之connectSlotsByName函数

- python udp 直播_Python使用UDP协议实现局域网内屏幕广播

- MybatisPlus常用条件查询器Wrapper的使用

- 大学本科计算机考试小抄,大学考试竟允许光明正大打小抄你也考不过

- 商务英语还是计算机专业好,是读广东外语外贸大学计算机专业好还是广东工业大学计算机专业好...

- php api json查错,PHP使Laravel为JSON REST API返回自定义错误的问题

- centos7.0配置php环境,如何在centos7中配置一个php开发环境

- 操作系统实验·动态分区分配算法