深入 AXI4 总线(一)握手机制

VALID/READY 握手机制

AXI 总线共有 5 个独立的通道,分别为写地址,写数据,写回应,读地址,读数据通道。5 条通道相互独立,有一些细小的差别,但共同使用一套握手机制:VALID/READY 机制。

VALID/READY 机制这个赛高啊,这个好啊,ARM 的手册上这么夸:

作为一种双向流控机制,VALID/READY 机制可以使发送接收双方都有能力控制传输速率。

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息放到的写总线上,并保持。

接收方置高 READY 信号表示接收方已经做好接收的准备。

所谓的双向流控机制,指的是发送方通过 VALID 信号置起控制发送速度的同时,接收方也可以通过 READY 信号的置起与否控制接收速度,反压发送方的发送速度。

当双方的信息同时为高,时钟上升沿到达后,一次数据传输完成,在 1 到 n 次时钟上升沿后,双方传完了要传的信息后,两信号同时拉低。

VALID/READY 的三种情况

VALID/READY 信号按照到达的先后顺序可以分为 3 种情况:

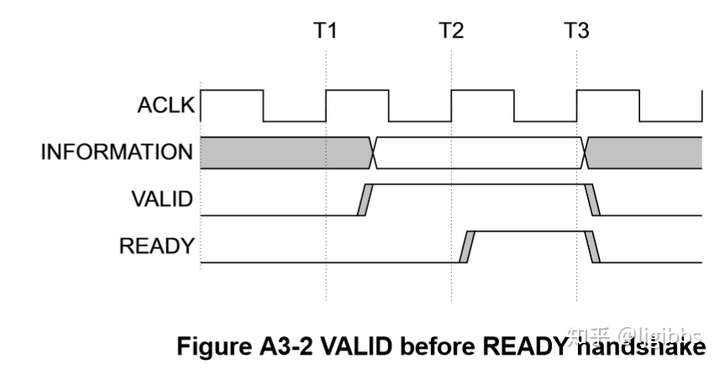

1.VALID 信号先到达

发送方 VALID 信号早早就到了,这时还不到 T2 时刻,并带来了新鲜的数据(数据通道),地址或者控制信息(地址通道)。

但过了 T2 也没见到接收方的 READY 信号。原来是接收方还忙着,可能上一次的数据还没存完,还堵在数据通路上,忙过了 T2 才来。

好吧,那也行,T3 时刻传输完成。

在这种情况下,接收方通过 READY 信号控制了传输速度,反压了发送速度。

协议规定:VALID 信号一旦置起就不能拉低,直到此次传输完成。对于接收方编程来说,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

协议另外规定:发送方不能在置起 VALID 信号之前就光等待 READY 信号。

这句阅读理解有点难,原文为:

作者个人从总线接口编程的角度理解,READY 信号可能先到达,如下图的情况。但是发送方编程时,不能依赖 READY 信号先到达的情况。不能将 READY 信号置高作为置高 VALID 的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号。

换句话说,发送方准备发送,置起 VALID 信号是完全主动的过程。接收方按照协议可以依赖发送方,但如果此时发送方也依赖接收方,就会造成死锁的情况,所以协议在这里规定了 VALID 信号的主动性。

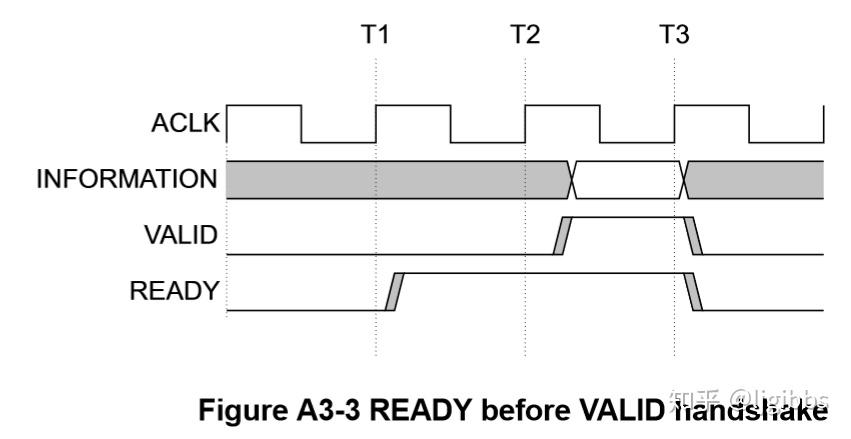

2.READY 信号先到达

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后拉低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

3.同时到达

同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地完成了,一个时钟周期里就完成了。

深入 AXI4 总线(一)握手机制相关推荐

- 深入AXI4总线- [一] 握手机制

知乎用户ljgibbs授权转发 本系列我想深入探寻 AXI4 总线.不过事情总是这样,不能我说想深入就深入.当前我对 AXI总线的理解尚谈不上深入.但我希望通过一系列文章,让读者能和我一起深入探寻 A ...

- AXI4协议学习:架构、信号定义、工作时序和握手机制

目录 1 AXI是什么? 2 AXI怎么工作? 3 AXI协议 3.1 架构 3.1.1 通道定义 3.1.2 接口与互连(interconnect) 3.1.3 Register slices 3. ...

- 数字IC验证:总线握手协议(VALID/READY握手机制)

写在前面: 最近学习总线协议,涉及握手,因此整理本文.若内容有疑惑或错误之处,请在评论区指出,感谢! 文章目录 1 什么是"握手"? 2 VALID/READY握手机制 3 Cas ...

- AXI_02 AXI4总线简介(协议、时序)

本篇文章内容在各大资料上都可找到,内容摘自专业书籍,这里作为该系列文章的原理篇. 由于该系列文章阅读有顺序性,所以请跳转至该系列文章第一篇从头开始阅读,并按照文章末尾指示按顺序阅读,否则会云里雾里,传 ...

- axi时序图_深入 AXI4总线(E3)实战:制作一个 AXI 接口 IP

本系列我想深入探寻 AXI4 总线.不过事情总是这样,不能我说想深入就深入.当前我对 AXI总线的理解尚谈不上深入.但我希望通过一系列文章,让读者能和我一起深入探寻 AXI4. 在本系列先前的文章中, ...

- axi4协议的乱序_一篇文章读懂读透FPGA AXI4 总线协议

新一代FPGA中采用的基本都是AXI4总线协议,例如与slaver侧的DMA或DDR等通信.这篇讲AXI4的文章感觉讲的很清楚. 0.绪论AXI是高级扩展接口,在AMBA3.0中提出,AMBA4.0将 ...

- 带你快速入门AXI4总线--AXI4-Stream篇(1)----AXI4-Stream总线

写在前面 随着对XILINX器件使用的深入,发现越来越多的IP都选配了AXI4的接口.这使得只要学会了AXI4总线的使用,基本上就能对XILINX IP的使用做到简单的上手.所以学会AXI4总线,对X ...

- FPGA控制DDR读写(AXI4总线接口)

FPGA控制DDR读写(AXI4总线接口) 范围 本文适用于FPGA控制DDR读写 MIG核 MIG信号注释 DDR型号为 MT41K256M16TW-107 下面是MIG IP核的相关信号 图2.1 ...

- 深入 AXI4总线 (四):RAM 读取实战

光说不练,云玩家.这篇文章中我们就通过访问一个 AXI4 接口的 RAM 的实际操作,加深我们对 AXI4 总线的理解. 我们的实验平台是 ISE 14.7 以及 modelsim 10.2, RAM ...

最新文章

- php 刀客友朋,数组与数组函数学习心得

- python pdf处理 图片_python PDF文件合并、图片处理

- C# VS预生成事件命令行 和 生成后事件命令行

- Python(10)- 格式化输出%

- Arp Scan和局域网隐身

- ML算法整理(一)线性回归与梯度下降 python实现

- pd虚拟机 17.1.2 Intel核心Mac专用版

- 在屏幕中间分别显示绿色、绿低红色、白底蓝色的字符串'welcome to masm!'

- #西柚姨妈体#蹿红微博 流行体之风重袭网络

- CPC客户端的安装方法

- android qq音乐无法连接网络连接,qq音乐不能播放_qq音乐为什么老是提示说歌曲无效或网络连接失败呢?...

- 【开发】后端框架——Mybatis

- 一个通用中间组件,简单通用的适配 ViewPager,以及 pager 中的 RecycleView 简化复杂的操作,简单直接。

- 第七周项目(5):排队看病时模拟

- 如何从光盘启动计算机!

- Spring注解大全(史上最全,字母编号,有实例)

- 一文解读广告投放全攻略,提升拓客效率

- 月薪2w+的测试,到底强在哪里?

- Windows引导过程

- 利用OBS输出计时器定时录制功能录制视频

热门文章

- 构建高性能微服务架构(网易)

- layui radio标签禁用和取消禁用

- ERROR 1819 (HY000): Your password does not satisfy the current policy requirements问题解决

- 【Web】多读书多看报

- Error creating bean with name ‘BAdminMapper‘ defined in file [C:\Users\ASUS\Desktop\FleakMarket-mast

- Android前台服务讲解二之自定义通知视图(RemoteViews)及数据UI更新

- PAT乙级【1001~1050】

- element-table 数据过多时浏览器卡死

- 开源作品——CMSIS-DAP调试器

- 以太网PHY接口直连设计