【 FPGA 】时钟简介

时钟,时序逻辑的心跳

在时序逻辑中,正是时钟信号将各个存储单元中的数据一级一级地推动下去,如果时钟信号突然停止,那么整个时序逻辑也将陷入瘫痪,因此,时钟就好像时序逻辑的心跳一样,那么重要却又平常的存在着。

几乎所有的FPGA设计都是时序逻辑,就意味着几乎所有的FPGA设计都离不开时钟,时钟之于时序逻辑,好比空气之于众生。因此,要确保FPGA设计成功,就先要确保时钟信号成功。

如果要评判FPGA实现某一功能的可行性,那么第一步, 看时钟,判断该功能对时钟信号的要求是否超越了FPGA的能力范围;如果让你着手开始一个FPGA设计,第一步,还是先看时钟,选择合适的时钟作为整个项目的支撑。

时钟信号的基本特征

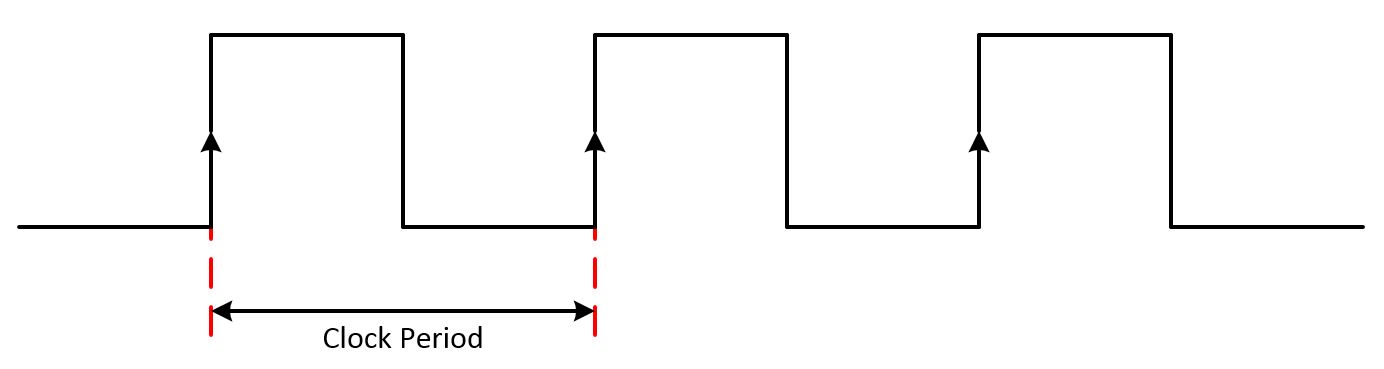

时钟信号是具有固定周期的方波。 周期是指一个时钟边沿到下一个同类时钟边沿之间的时间间隔,最常用的方式是一个上升沿到下一个上升沿之间的时间间隔。 时钟的频率等于时钟周期的倒数。

图1. 数字波形作为时钟信号的参考,时钟信号具有固定周期,在数据传输过程中用固定的时间间隔来同步数字信号发射器和接收器。

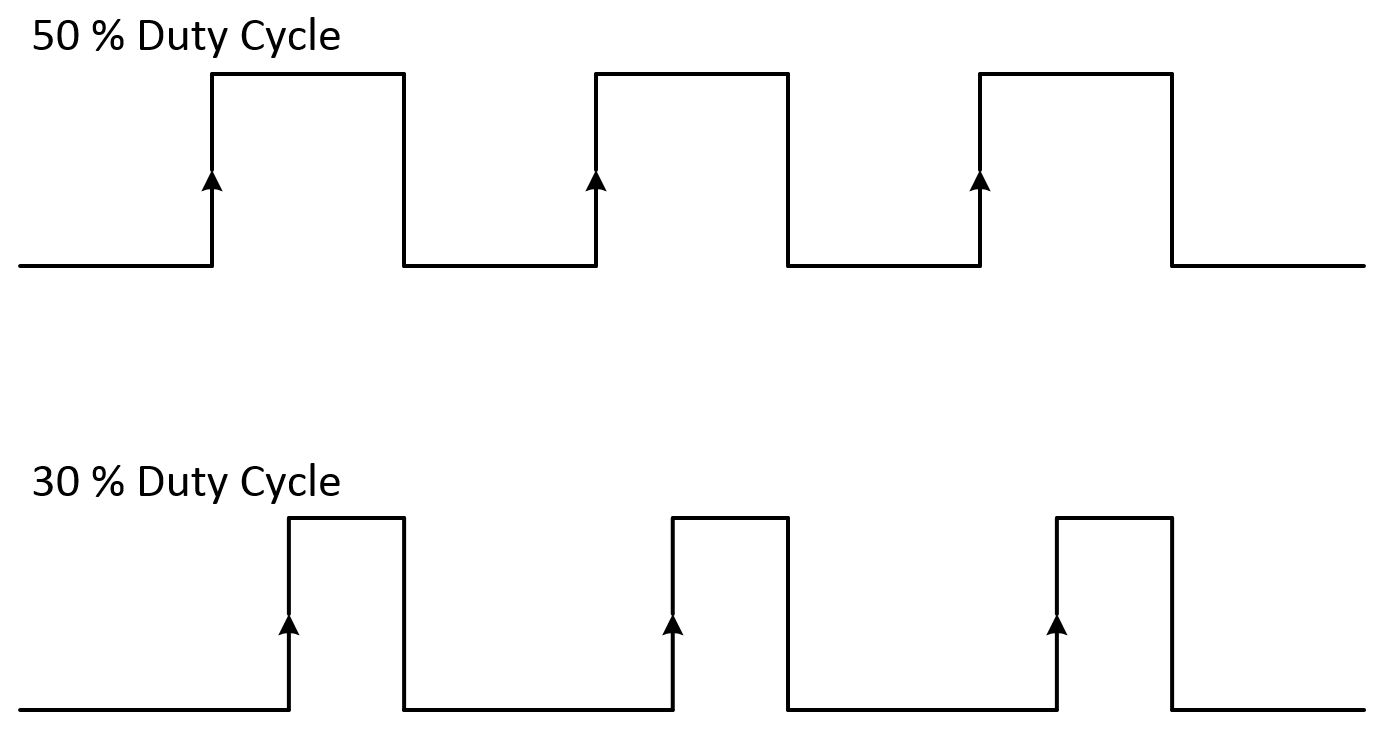

时钟信号的占空比是波形处于高电平占周期的时间比。 图2展示了两个具有不同占空比的波形的区别 您可以发现占空比为30%的波形处于的时间少于占空比为50%的波形。

图2.信号的占空比是指波形处于的时间百分比。

时钟信号用于在数据传输过程中同步数字信号发射器和接收器。 比如,发射器可以在时钟信号的每个上升沿发送一个数据位,接收器可使用相同的时钟读取数据。 在这种情况下,设备的确定边沿是上升沿(从低电平到高电平)。 对于其他设备则可能是下降沿(从高电平到低电平)。 时钟的确定边沿又称为有效时钟边沿。 数字信号发射器在每个有效时钟边沿触发新的数据发送,而接收器则在每个有效时钟边沿上进行采样。 后来的设备开始同时使用时钟的上升验和下降沿;这种设备被称为双倍数据速率传输(DDR)设备。 事实上,数据传输对于有效边沿有短暂的时延;这种延时称为时钟到输出时间。

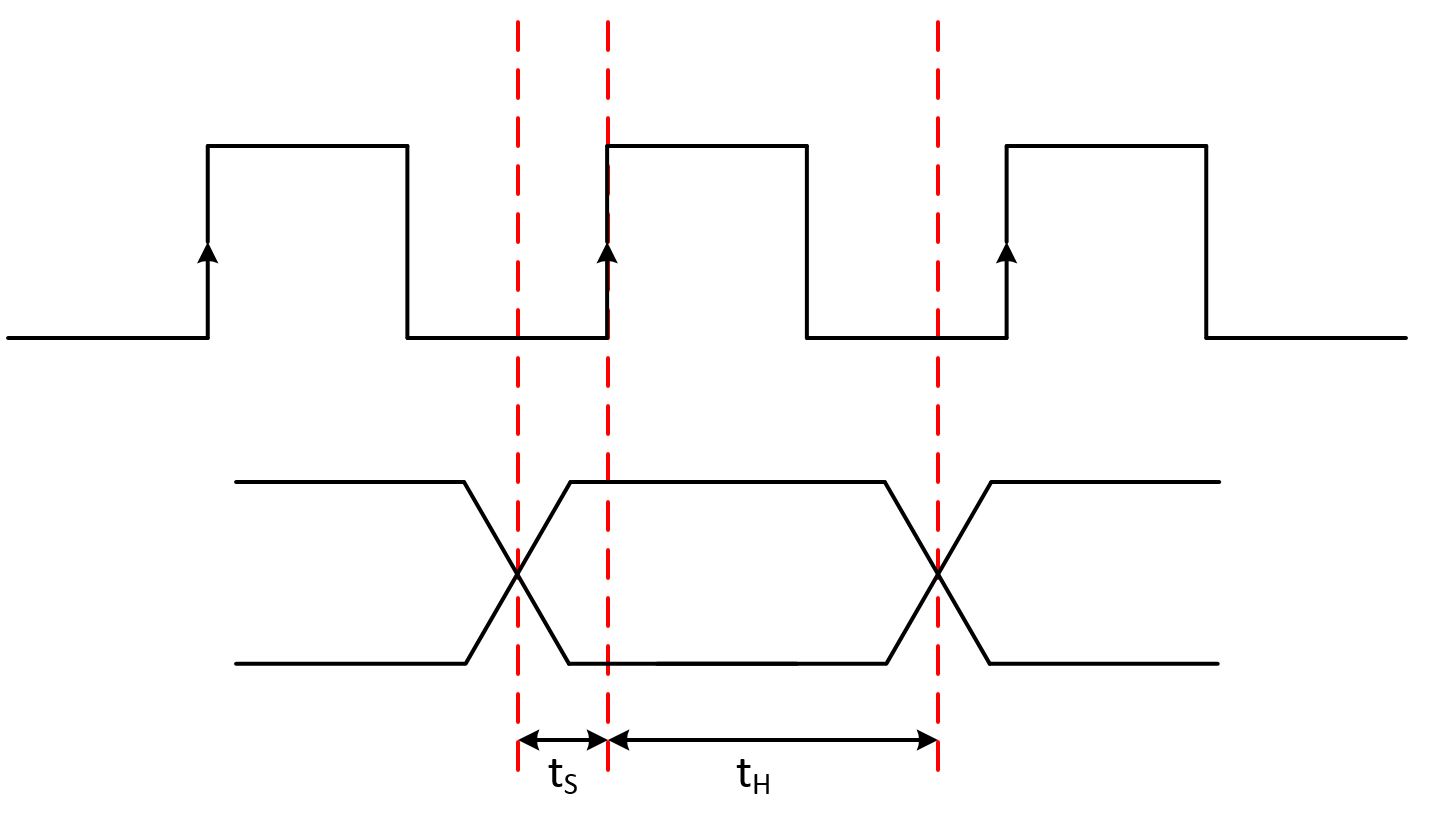

当接收器依据采集时钟接收数据时,我们需要注意两个定时参数,以确保接收数据的可靠性。 建立时间(ts)是指数据连续处于有效逻辑电平且接收器准备好接收输入信号所需的时间。 保持时间(tH)是指接收器采样后,数据发生变化前需要保持在原有状态的时间。 建立时间和保持时间在接收器的时钟有效边沿附近形成了一个稳定的窗口,以便接收器能够可靠地采集数据。 图3给出了一个上升沿时钟信号的建立时间和保持时间。 通常,数字信号会在上升轨迹的中间切换电压;因此时间基准标志通常放置在信号边沿的正中央。

图3.建立时间和保持时间在接收器的时钟有效边沿附近形成了一个稳定的窗口,以便接收器能够可靠地采集数据。

如何区分时钟和数据?

时钟信号的本质,是在于其是否为时序逻辑提供“心跳”机制,而不在于其具体的表现形式。

也就是说,如果仅仅观察信号的数字波形,是无法分辨一个信号到底是时钟信号还是数据信号的。要想做出准确分辨,必须去查看该信号在数字电路中的连接关系,举个例子,如果一个信号连接到一个寄存器的时钟端,那么它就是一个时钟信号;如果该信号连接到一个寄存器的数据输入端,那么它就是一个数据信号;如果一个信号连接到一个寄存器的时钟端的同时又连接到另一个就餐器的数据输入端,那么它就具有了时钟信号和数据信号的双重身份。

时钟信号的分类

1 按来源分

按来源分,时钟信号可分为内部时钟和外部时钟,而内部时钟又可以分为再生时钟、门控时钟、行波时钟:

(1)外部时钟

外部时钟是指时钟信号的来源是在FPGA芯片的外部。通常来说,外部时钟源对FPGA设计来说是必需的,因为一般FPGA芯片内部没有能够产生供内部逻辑使用的时钟信号的选频和激励电路。所以,需要在FPGA芯片的外部使用晶振以及恰当的电阻、电容、电感、三极管等器件,来搭建用于产生时钟信号的电路,并将其通过FPGA芯片的恰当物理管脚引入到FPGA内部供时序逻辑使用。

(2)内部时钟

1)再生时钟

再生时钟指的是FPGA内部产生的新时钟,这个时钟是以一个输入的时钟信号作为参考,然后在此基础上通过调整其频率和相位而产生出来的新时钟。

目前来说,FPGA芯片内部能够产生再生时钟信号的模块有DCM、PLL、MMCM等。

2)门控时钟

门控时钟,指的是由组合逻辑产生的时钟,其中,组合逻辑的输入可以全部是数据信号,也可以包含原始时钟信号。由于组合逻辑中的基本单元是与或非等门电路,而与门和非门又具有“开关性”,故该类时钟又称为门控时钟。

通常情况下,不建议使用门控时钟,因为门控时钟由组合逻辑产生,那么它本身就潜伏了组合逻辑的最大隐患——竞争和险象,所以门控时钟信号很容易产生毛刺,而寄存器等存储单元对时钟信号的边沿都非常敏感,因此具有毛刺的时钟会造成时序逻辑的不稳定。

3)行波时钟

行波时钟,是指有时序逻辑产生的时钟。

通常情况下,也不建议在FPGA的内部引入行波时钟,因为这样会在FPGA设计中引入新的时钟域,增加时序分析的难度,并且由于行波时钟的相位通常会滞后于原始时钟,因此后续触发器的保持时间不一定能够得到满足。

事实上,采用行波时钟的目的无非就是为后续时序电路的处理速度进行降频,而要实现降频的功能,除了通过降低时钟信号的频率外,仍然可以通过控制后续时序电路存储单元的使能端来实现。

这样,整个时序逻辑将只被一个时钟信号所驱动,变得清晰又易控。

2 按波形分

时钟信号按波形分,可以分为连续时钟,间歇时钟,不规则时钟。

(1)连续时钟

连续时钟是连续的,周期的,一般FPGA内部的时钟通常来说都是连续时钟。

(2)间歇时钟,时钟波形存在间断,时有时无。

间歇时钟常见于FPGA数据输入或输出接口,这是因为有些外围器件的同步接口不包括使能端,因此在没有需要传输的数据时只能通过关闭时钟来暂停通信,这样也可以在一定程度上减少功耗。

(3)不规则时钟,无规律可循,没有固定的周期和频率,也没固定的占空比,并且还时有时无。

不规则的时钟也常见于FPGA的数据输入或输出接口,与间歇时钟产生的原因类似,只不过间歇式时钟往往针对成包或成帧传输数据的接口,因此每次都会输出一连串规则的波形信号,而不规则时钟针对的接口数据量往往比较小,也没有固定的数据结构,因此有一个数据就会传输一个数据。

1、同相位时钟

同相位时钟可以频率不同,但是时钟跳变沿是对齐的。如图所示,clk0为慢时钟,clk1为快时钟,clk0的时钟沿始终与clk1的时钟沿对齐,两个时钟相位相同。

2、同源时钟

同源时钟,通常由一个PLL或者DLL产生,相位不需要相同,只要求相位固定。

3、同时钟域时钟

同时钟域的时钟既是同源时钟,还要求相位相同并且频率相同,通常是同一个PLL产生的频率相同相位相同的时钟,PLL能够保证两个时钟在不同的情况下(如温度不同)的偏差在精度范围内。从波形上看,同时钟域两个时钟频率一样,跳变沿完全对称。但是从波形上看两个时钟频率一样,跳变沿完全对称的不一定是同时钟域时钟,如两个PLL输出的看似相同的时钟不是同一个时钟域的,例如在不同的温度下,就不能保证两个时钟的偏差。

参考文献:

FPGA之道

数字定时: 时钟信号、抖动、迟滞和眼图

同相位时钟

【 FPGA 】时钟简介相关推荐

- (71)FPGA时钟双沿约束如何做?

1.1 FPGA时钟双沿约束如何做? 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA时钟双沿约束如何做? 5)结束语. 1.1.2 本节引言 "不积跬 ...

- (91)FPGA时钟分频与倍频问题,面试必问(十五)(第19天)

(91)FPGA时钟分频与倍频问题,面试必问(十五)(第19天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA时钟分频与倍频问题,面试必问(十五)(第1 ...

- (83)FPGA时钟抖动和时钟偏斜-面试必问(七)(第17天)

(83)FPGA时钟抖动和时钟偏斜-面试必问(七)(第17天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA时钟抖动和时钟偏斜-面试必问(七)(第17天 ...

- (8)FPGA时钟设计(第2天)

(8)FPGA时钟设计(第2天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA时钟设计(第2天) 5)技术交流 6)参考资料 2 FPGA初级课程介绍 ...

- (78)FPGA时钟激励(forever)

(78)FPGA时钟激励(forever) 1.1 目录 1)目录 2)FPGA简介 3)Verilog HDL简介 4)FPGA时钟激励(forever) 5)结语 1.2 FPGA简介 FPGA( ...

- (77)FPGA时钟激励(always)

(77)FPGA时钟激励(always) 1.1 目录 1)目录 2)FPGA简介 3)Verilog HDL简介 4)FPGA时钟激励(always) 5)结语 1.2 FPGA简介 FPGA(Fi ...

- (12)FPGA时钟设计原则

(12)FPGA时钟设计原则 1.1 目录 1)目录 2)FPGA简介 3)Verilog HDL简介 4)FPGA时钟设计原则 5)结语 1.2 FPGA简介 FPGA(Field Programm ...

- (08)FPGA时钟概念

(08)FPGA时钟概念 1.1 目录 1)目录 2)FPGA简介 3)Verilog HDL简介 4)FPGA时钟概念 5)结语 1.2 FPGA简介 FPGA(Field Programmable ...

- FPGA时钟激励编写(方法四)

1.1 FPGA时钟激励编写(方法四) 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA时钟激励编写(方法四) 5)结束语. 1.1.2 本节引言 "不 ...

- FPGA时钟激励编写(方法三)

1.1 FPGA时钟激励编写(方法三) 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA时钟激励编写(方法三) 5)结束语. 1.1.2 本节引言 "不 ...

最新文章

- 使用Hyper-v 创建Windows Server 2008 Cluster(二)

- MySQL from后面的子查询使用

- 2017.9.21 problem a 失败总结

- java转json数组对象_java对象转json、json数组 、xml | 学步园

- .NET 内存管理与垃圾回收:实现IDisposable接口和析构函数

- C#根据字节数截取字符串【转载】

- 第四届中国云计算大会——123

- 《Python和Pygame游戏开发指南》——导读

- 2345广告,够了!

- JHOST邀请码,2012年7月31日申请,2012年8月31日过期

- 电子原理 半波整流与桥式整流Protues仿真电路

- 怎么从安卓设备转移数据到苹果_如何将数据从安卓手机转移到苹果手机

- linux查询当前时间

- hadoop 历史版本下载

- 电脑广告弹窗怎么解决?

- google map api v3 的marker使用label的方法(markerwithlabel的使用)

- ionic2实现通讯录,联系人搜索功能

- 未来教育python全程班百度云_2019、3未来教育等级考试

- 海康萤石NTP时间不同步问题思路X5C

- 一招完美解决SSD系统盘卡顿死机的问题!

热门文章

- SAP 画皮门 从白狐到超人的华丽转身

- ASP.NET 4的Demo实践:URL路由改进支持

- 华为平板上wps另存为的文件在哪里能找到_原创干货 | WPS危害之嵌入ole对象绑定载荷...

- 2018全国计算机考试报名入口,北京2018年3月全国计算机等级考试报名入口

- 华为鸿蒙被扒出来安卓,华为鸿蒙被“实锤”,操作界面曝光,为何被吐槽是换皮安卓?...

- 启动多个pid_西门子S7-300PLC实现PID控制

- 第十六届全国大学生智能车竞赛广东赛区线上竞赛方案

- 基于黄色LED反向电流的光电检测板

- 比Tiny YOLOv3小8倍,性能提升11个点,4MB的网络也能做目标检测

- 2020人工神经网络第一次作业-参考答案第四部分