FPGA设计——CMOS摄像与HDMI显示(DVP版)

1. 概述

本设计采用FPGA技术,将CMOS摄像头(DVP接口)的视频数据经过采集、存储、处理、帧率转换,最终通过HDMI接口显示在电视屏幕上。

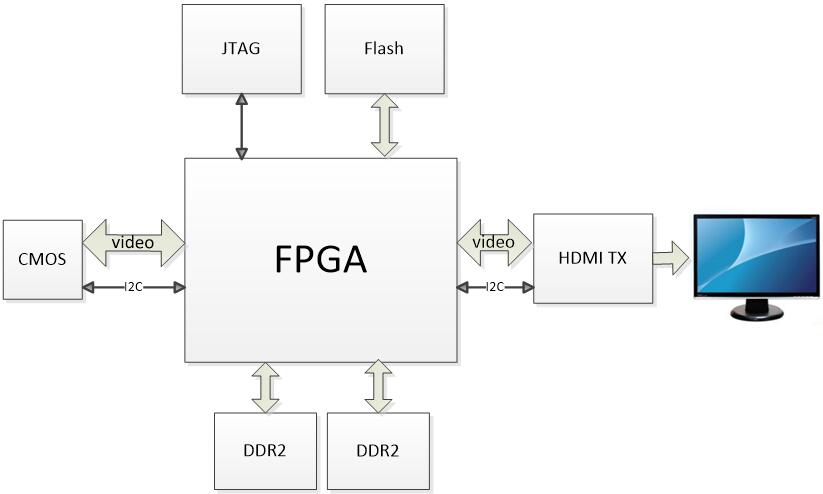

2. 硬件系统框图

CMOS采用分辨率为1080p的摄像头芯片,FPGA采用ALTERA公司的CYCLONE IV,FLASH采用EPCS64,DDR2采用Hynix公司的1Gb内存条,HDMI采用Silicon Image公司的SiI9134。

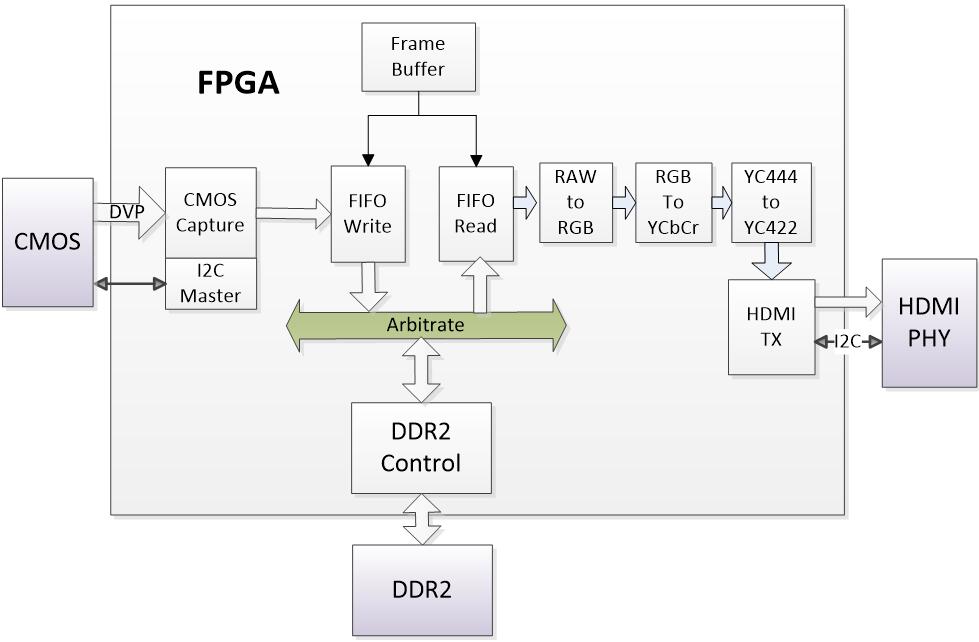

3. FPGA逻辑框图

FPGA各部分逻辑模块如下图所示:

CMOS Capture,采集CMOS摄像头视频数据;

I2C Master,配置CMOS芯片;

DDR2 Control,配置与控制DDR2芯片组,实现读写仲裁;

FIFO Write,将采集到的视频数据跨时钟域地写进DDR2中;

FIFO Read,将DDR2中的数据跨时钟域地读出给后续图像处理模块;

Frame Buffer,负责FIFO Write和FIFO Read的调度,实现帧率转换;

RAW to RGB,将原始RAW8数据转换成RGB888数据;

RGB to YCbCr,将RGB888数据转换成YCbCr444数据;

YC444 to YC422,将YC444的数据转换成YC422的数据给HDMI TX模块;

HDMI TX,将处理好的视频数据发送给HDMI PHY芯片,同时通过I2C接口配置HDMI PHY芯片。

4. CMOS配置

摄像头芯片支持最高1080p30帧的输出,参考寄存器配置如下:

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

|

module i2c_cfg_par(

input clk,

input [07:0] lut_index,

output reg [23:0] lut_data

);

always @(*)

begin

case(lut_index)

//27M input 67.5M output

'd0 : lut_data <= 'h3105_02;

'd1 : lut_data <= 'h0103_01;

'd2 : lut_data <= 'h3105_02;

'd3 : lut_data <= 'h0100_00;

'd4 : lut_data <= 'h301e_b0;

'd5 : lut_data <= 'h320c_03;

'd6 : lut_data <= 'h320d_e8;

'd7 : lut_data <= 'h3231_24;

'd8 : lut_data <= 'h320E_04;

'd9 : lut_data <= 'h320F_65;

'd10 : lut_data <= 'h3211_08; //x start

'd11 : lut_data <= 'h3213_10; //y start

'd12 : lut_data <= 'h3e03_01;

'd13 : lut_data <= 'h3e01_46;

'd14 : lut_data <= 'h3e08_00;

'd15 : lut_data <= 'h3e09_10;

'd16 : lut_data <= 'h3518_03;

'd17 : lut_data <= 'h3518_03;

'd18 : lut_data <= 'h5025_09;

'd19 : lut_data <= 'h3908_c0;

'd20 : lut_data <= 'h3416_10;

'd21 : lut_data <= 'h3e0f_90;

'd22 : lut_data <= 'h3638_85;

'd23 : lut_data <= 'h3637_bf;

'd24 : lut_data <= 'h3639_98;

'd25 : lut_data <= 'h3035_01;

'd26 : lut_data <= 'h3034_ba;

'd27 : lut_data <= 'h3300_10;

'd28 : lut_data <= 'h3301_18;

'd29 : lut_data <= 'h3308_38;

'd30 : lut_data <= 'h3306_34;

'd31 : lut_data <= 'h330a_00;

'd32 : lut_data <= 'h330b_90;

'd33 : lut_data <= 'h3303_18;

'd34 : lut_data <= 'h3309_18;

'd35 : lut_data <= 'h331e_0e;

'd36 : lut_data <= 'h331f_0e;

'd37 : lut_data <= 'h3320_14;

'd38 : lut_data <= 'h3321_14;

'd39 : lut_data <= 'h3322_14;

'd40 : lut_data <= 'h3323_14;

'd41 : lut_data <= 'h3626_03;

'd42 : lut_data <= 'h3621_28;

'd43 : lut_data <= 'h3f08_04;

'd44 : lut_data <= 'h3f09_44;

'd45 : lut_data <= 'h4500_25;

'd46 : lut_data <= 'h3c09_08;

'd47 : lut_data <= 'h335d_20;

'd48 : lut_data <= 'h3368_02;

'd49 : lut_data <= 'h3369_00;

'd50 : lut_data <= 'h336a_04;

'd51 : lut_data <= 'h336b_65;

'd52 : lut_data <= 'h330e_50;

'd53 : lut_data <= 'h3367_08;

'd54 : lut_data <= 'h3f00_06;

'd55 : lut_data <= 'h3f04_01;

'd56 : lut_data <= 'h3f05_c8;

'd57 : lut_data <= 'h3905_1c;

'd58 : lut_data <= 'h5780_7f;

'd59 : lut_data <= 'h5782_0a;

'd60 : lut_data <= 'h5783_08;

'd61 : lut_data <= 'h5786_20;

'd62 : lut_data <= 'h5787_0c;

'd63 : lut_data <= 'h5789_01;

'd64 : lut_data <= 'h578a_0f;

'd65 : lut_data <= 'h5000_06;

'd66 : lut_data <= 'h3632_48;

'd67 : lut_data <= 'h3622_0e;

'd68 : lut_data <= 'h3627_02;

'd69 : lut_data <= 'h3630_b4;

'd70 : lut_data <= 'h3633_94;

'd71 : lut_data <= 'h3620_42;

'd72 : lut_data <= 'h363a_0c;

'd73 : lut_data <= 'h3334_60;

'd74 : lut_data <= 'h303f_81;

'd75 : lut_data <= 'h501f_00;

'd76 : lut_data <= 'h3b00_f8;

'd77 : lut_data <= 'h3b01_40;

'd78 : lut_data <= 'h3c01_14;

'd79 : lut_data <= 'h4000_00;

'd80 : lut_data <= 'h3d08_00;//'h3d08_01;

'd81 : lut_data <= 'h3640_00;

'd82 : lut_data <= 'h0100_01;

'd83 : lut_data <= 'h303a_09;

'd84 : lut_data <= 'h3039_66;

'd85 : lut_data <= 'h303f_82;

'd86 : lut_data <= 'h3636_88;

'd87 : lut_data <= 'h3631_90;

'd88 : lut_data <= 'h3635_08;

'd89 : lut_data <= 'h3105_04;

'd90 : lut_data <= 'h3105_04;

`endif

default : lut_data <= 'h0000;

endcase

end

endmodule

|

5. 显示结果

电视显示1080p30的视频信号,图像中的色卡表明颜色显示正常。

本文转自 shugenyin 51CTO博客,原文链接:http://blog.51cto.com/shugenyin/1857492

FPGA设计——CMOS摄像与HDMI显示(DVP版)相关推荐

- FPGA虚拟三阶魔方(HDMI显示版)

目录 编辑 一.设计概述 二.设计模块 1.三阶魔方建模 (1)魔方基本操作: (2)魔方建模: 2.魔方转动控制: (1)控制概述: (2)按键消抖: (3)魔方控制: 3.HDMI显示模块: ( ...

- 基于FPGA的 TMDS 编码 及 HDMI 显示

目录 引言 TMDS 编码 原理简介 TMDS编码实现 HDMI差分数据串行 实现方法 源码 HDMI显示方法 思路 实现 工程结构 源代码分享 板级调试视频 引言 最近在开发板上倒腾了一下 TMDS ...

- FPGA 20个例程篇:19.OV7725摄像头实时采集送HDMI显示(三)

第七章 实战项目提升,完善简历 19.OV7725摄像头实时采集送HDMI显示(三) 在详细介绍过OV7725 CMOS Sensor的相关背景知识和如何初始化其内部寄存器达到输出预期视频流的目的后, ...

- 【正点原子FPGA连载】第四十四章MT9V034摄像头HDMI显示实验 -摘自【正点原子】新起点之FPGA开发指南_V2.1

1)实验平台:正点原子新起点V2开发板 2)平台购买地址:https://detail.tmall.com/item.htm?id=609758951113 2)全套实验源码+手册+视频下载地址:ht ...

- FPGA 20个例程篇:19.OV7725摄像头实时采集送HDMI显示(一)

第七章 实战项目提升,完善简历 19.OV7725摄像头实时采集送HDMI显示(一) 在例程"OV7725摄像头实时采集送HDMI显示"中,我们将走近FPGA图像处理的世界,图像处 ...

- activiti高亮显示图片_【正点原子FPGA连载】第二十章SD卡读BMP图片HDMI显示实验领航者 ZYNQ 之嵌入式开发指南...

1)实验平台:正点原子领航者ZYNQ开发板 2)平台购买地址:https://item.taobao.com/item.htm?&id=606160108761 3)全套实验源码+手册+视频下 ...

- 基于FPGA的HDMI显示(二)

基于FPGA的720P HDMI显示 1.4.1 HDMI 硬件电路分析 本次设计采用了 IO 模拟的方式实现 HDMI 的功能.与采用专用 HDMI 芯片相比,此方案具有成本更低.效果不输于采用 ...

- FPGA - 基于FPGA的HDMI显示

写在前面 HDMI接口很早之前就想调试了,由于没有时间,就拖到了现在,而且毕业设计也是和视频处理系统有关,就趁这个机会把这个接口调试下. 开发环境 vivado 18.3 pynq - z2 HDMI ...

- 基于FPGA的HDMI显示(一)

1.1 HDMI简介 简介略,网上很多,这里也不过多描述. 1.2 基于FPGA的HDMI接口设计 HDMI输出接口在FPGA方面应用时,主要有两种方式:一种就是如图1 22所示的方式,采用Sil ...

最新文章

- 强化学习(八) - 深度Q学习(Deep Q-learning, DQL,DQN)原理及相关实例

- eclipse中设置Linux编码环境,更改eclipse中console编码

- VTK:InfoVis之DelimitedTextReader

- VHDL其他顺序语句

- 静态连接和动态链接有什么区别?

- 找不到图片素材,看这里

- R语言编程基础(1)

- 优化C/C++代码的小技巧

- Linux安装后无法进入图形界面(GNOME,KDE等)的解决方法

- 各类电商购物网站商城系统静态网页html制作(含静态网站源码)

- C/C++ typedef用法详解

- codesys 实现冒泡排序

- bit与Byte,KB与KiB,MB与MiB,GB与GiB等

- python 视频清晰度_python识别视频黑屏或者低清晰度

- 春运抢火车票攻略汇总(持续更新中)

- FPGA--有限状态机(FSM)的设计

- Linux这些年经历了什么?

- Win10计算机窗口空白,windows10语言栏丢失怎么办?win10语言栏显示空白的解决办法...

- export ‘createStore‘ (imported as ‘createStore‘) was not found in ‘./store/index.js‘ (possible expor

- PON、EPON、GPON的区别