[转] 基本RS触发器

在触发器中,最简单的触发器是基本RS触发器,它由两个与-非门(或者两个或-非门)来组成。

图5.2.1(a)是由与-非门构成的基本RS触发器,由图看出,基本RS触发器有两个输入端( 和

和 )和两个输出端(

)和两个输出端( 和

和 ),门G1和G2的组成有对称性, G1的输出经过G2的传输后回送到G1的另一个输入端,G2的输出经过G1的传输后回送到G2的另一个输入端,正是有了这样的反馈通道才使其具有了存储特性,也有别于前面所讲到的组合逻辑电路。通常将它们的电路结构画成图5.2.1(b)的形式,与

),门G1和G2的组成有对称性, G1的输出经过G2的传输后回送到G1的另一个输入端,G2的输出经过G1的传输后回送到G2的另一个输入端,正是有了这样的反馈通道才使其具有了存储特性,也有别于前面所讲到的组合逻辑电路。通常将它们的电路结构画成图5.2.1(b)的形式,与 相连的输出端称为

相连的输出端称为 ,与

,与 相连的输出端称为

相连的输出端称为 。

。

定义输出端的状态: ,

, 时,为触发器的1状态;

时,为触发器的1状态; ,

, ,为触发器的0状态。触发器处与1状态或0状态时输出端都有互补性。下面具体分析两个输入端对输出端的影响情况。

,为触发器的0状态。触发器处与1状态或0状态时输出端都有互补性。下面具体分析两个输入端对输出端的影响情况。

(1)当 ,

, 时,

时, ,

, ,触发器为0状态;

,触发器为0状态;

(2)当 ,

, 时,

时, ,

, ,触发器为1状态;

,触发器为1状态;

(3)当 ,

, 时,触发器两个输出端的值不变,触发器保持为原来的状态;

时,触发器两个输出端的值不变,触发器保持为原来的状态;

(4)当 ,

, 时,

时, ,

, ,此时触发器的输出端既不是定义的1状态,也不是定义的0状态,破坏了

,此时触发器的输出端既不是定义的1状态,也不是定义的0状态,破坏了 和

和 的互补特性,实际使用时应该避免这种现象的产生。因为在

的互补特性,实际使用时应该避免这种现象的产生。因为在 和

和 的有效信号同时消失时,即

的有效信号同时消失时,即 和

和 同时从0变到1时,输出端的值不确定。

同时从0变到1时,输出端的值不确定。

下面分析当 和

和 同时从0转变到1时,输出端的情况。假设G1的传输时延小于G2的传输时延,在

同时从0转变到1时,输出端的情况。假设G1的传输时延小于G2的传输时延,在 由0变为1时,即G1的输出先变为0,其值反过来影响到G2的输出,使

由0变为1时,即G1的输出先变为0,其值反过来影响到G2的输出,使 的值仍然保持为1;另一种假设就是G2的传输时延小于G1的传输时延,在

的值仍然保持为1;另一种假设就是G2的传输时延小于G1的传输时延,在 由0变为1时,即G2的输出先变为0,其值反过来影响到G1的输出,使

由0变为1时,即G2的输出先变为0,其值反过来影响到G1的输出,使 的值仍然保持为1。用图5.2.2可以说明在

的值仍然保持为1。用图5.2.2可以说明在 和

和 同时从0变为1时,输出端逻辑值的不确定情况,从图中可以看出,在这种情况下,门电路传输时延小的门电路其输出端的值会发生变化,而门电路传输时延大的门电路逻辑门其输出端的值不会发生变化。

同时从0变为1时,输出端逻辑值的不确定情况,从图中可以看出,在这种情况下,门电路传输时延小的门电路其输出端的值会发生变化,而门电路传输时延大的门电路逻辑门其输出端的值不会发生变化。

由以上分析可知, 和

和 的低电平同时消失时,在门电路传输时延未知的情况下,输出端状态是不确定的。在通常使用RS触发器时,应该避免这种情况的出现,一般不要让

的低电平同时消失时,在门电路传输时延未知的情况下,输出端状态是不确定的。在通常使用RS触发器时,应该避免这种情况的出现,一般不要让 和

和 同时为0。所以,在正常工作的条件下,用式

同时为0。所以,在正常工作的条件下,用式 +

+ =1来约束两个输入端,称为约束条件。

=1来约束两个输入端,称为约束条件。

在正常工作时,输出端 和

和 具有互补的特性,

具有互补的特性, 是低电平使输出端

是低电平使输出端 为0,

为0, 也是低电平才使输出端

也是低电平才使输出端 为1。所以

为1。所以 是低电平有效置0(

是低电平有效置0( ),置0也称为触发器复位,

),置0也称为触发器复位, 端称为复位端。

端称为复位端。 是低电平有效置1(

是低电平有效置1( ),置1也称为触发器置位,

),置1也称为触发器置位, 端称为置位端。

端称为置位端。

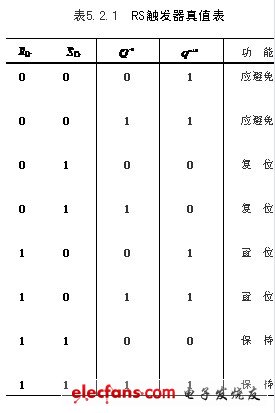

对于RS触发器输入和输出的逻辑关系,可以通过逻辑状态转移真值表来加以描述。如表5.2.1所示,真值表中考虑了触发器在 和

和 信号作用前的输出状态值,即触发器的初态

信号作用前的输出状态值,即触发器的初态 ,得到的新的状态记作

,得到的新的状态记作 。

。

表5.2.1可以写成逻辑状态转移表的形式,如表5.2.2的所示,亦称为逻辑状态转移表,还可以将其转换为卡诺图的形式,如图5.2.3所示。卡诺图中的“×”表示约束项,即约束条件 +

+ =1。

=1。

经过化简卡诺图后得到(5.2.1)式,这就是RS触发器的特性方程(也称为状态方程和或次态方程)。从特性方程中可以看出,输出端新的状态 与前一状态

与前一状态 有关,这是组合逻辑电路所不具有的特点。

有关,这是组合逻辑电路所不具有的特点。

图5.2.4为与-非门RS触发器状态转换图,图中“×”在此表示任意项,它用图形的方式描述了触发器状态间的转换情况。图5.2.5为与-非门RS触发器的逻辑符号。

例5.2.1 用与-非门组成的RS触发器中,已知输入端的波形如图5.2.6所示,试画出输出端 和

和 的电压波形图。

的电压波形图。

解: 在用与-非门组成的RS触发器中,输入端是低电平有效复位和置位,根据这一特性可以画出其输出波形。在图中必须注意 和

和 端同时出现了低电平,但是其低电平值不是同时消失的,所以输出端的值是可以确定的。

端同时出现了低电平,但是其低电平值不是同时消失的,所以输出端的值是可以确定的。

用或-非门也可以组成RS触发器,其电路结构和逻辑符号见图5.2.7(a)、(b),与前面与-非门组成的RS触发器相比,其输入端是高电平有效复位和置位。如果RS同时从高电平变到低电平时,输出的状态

是不确定的,所以其相应的约束条件为:RDSD=0。图5.2.7(c)是其卡诺图,利用约束条件化简得其特性方程为(5.2.2)式。

(5.2.2)

(5.2.2)

(原文地址:http://www.elecfans.com/book/story.php?id=621)

[转] 基本RS触发器相关推荐

- 触发器是不是不能喝外键同时存在_数字电路--RS触发器

1.基本RS触发器 (1)"与非"型基本RS触发器 工作原理: ① R= 1.S= 1 根据与非门的逻辑功能--"有0出1.全1出0",可知在这种情况下,G1. ...

- (37)VHDL实现RS触发器

(37)VHDL实现RS触发器 1.1 目录 1)目录 2)FPGA简介 3)VHDL简介 4)VHDL实现RS触发器 5)结语 1.2 FPGA简介 FPGA(Field Programmable ...

- (36)VHDL实现或非门型RS触发器

(36)VHDL实现或非门型RS触发器 1.1 目录 1)目录 2)FPGA简介 3)VHDL简介 4)VHDL实现或非门型RS触发器 5)结语 1.2 FPGA简介 FPGA(Field Progr ...

- 基本RS触发器(SR锁存器)

一.前言 SR锁存器(Set-Reset Latch)是静态存储单元当中最基本,也是电路结构最简单的一种,通常由两个或非门或者与非门组成.其中S表示Set,R表示Reset.则S_D称为置位端或置1输 ...

- 十分钟辨清锁存器与Rs触发器

rs触发器与锁存器,在新手看来非常不容易区分,会经常陷入混淆的情况.本篇文章将对于rs触发器与锁存器的区别进行讲解,帮助各位新手快速区分两者的不同. Rs触发器与锁存器在数据锁存的方式上有所区别,rs ...

- 2021.12.20基本RS触发器

RS触发器有与非和或非门两种构成,有时与非门构成的触发器还使用负逻辑. 我们注意到: 1.这两种RS触发器的RS对应的Q和Q非位置并不相同,这是为了保持R作为复位端,S作为置位端. 2.与非门构成的R ...

- 数电模电(三) 时序电路触发器 基本RS触发器 同步RS触发器 主从RS触发器 JK触发器 主从D触发器

本文原创首发CSDN,链接 https://blog.csdn.net/qq_41464123/article/details/90084796 ,作者博客https://blog.csdn.net/ ...

- 集成组合电路,编码器,全加器,译码显示器,RS触发器(或非门和与非门),主从JK触发器,D触发器

按一定的逻辑功能,把若干个门电路集成于一块芯片内,称为集成组合电路.内部可以采用不同的线路,但其外部输入输出的逻辑功能是相同的. 邮政编码,电话号码,学生学号等都是采用了编码的知识.在数字电路中,一般 ...

- RS 触发器防抖动原理

电路分析: 抖动电路的参考:https://www.dianyuan.com/article/32447.html 与非门的原理计算参考:https://blog.csdn.net/vivid117/ ...

最新文章

- 中国人民大学_《组织行为学》_18权力:怎样防止授权走样?

- linux之可视化查看磁盘大小并且删除大文件

- 哈希表的大小为何最好是素数

- 读写锁(ReadwriteLock)

- 互联网行业个人精进指南

- 因果推断笔记——DR :Doubly Robust学习笔记(二十)

- iOS核心动画详解swift版----基础动画

- win10系统 计算机配置要求高吗,win10流畅配置要求有哪些

- 【心电信号】基于matlab心电信号采集与处理【含Matlab源码 954期】

- csapp--键盘驱动程序的分析与修改

- html中文字不自动换行 white-space style

- 手写Vue个人组件库——fl-Lazyimg 图片懒加载

- noip2015day1

- spring boot 和cloud 版本升级

- 把生活过成 你想要的样子

- Android蓝牙开发 — 经典蓝牙BLE蓝牙

- ECG,脉搏波,心率,心率变异性,血压

- 惠斯登电桥传感器电路设计技巧,了解一下?

- Planet of the phones手机星球

- mysql 行号_mysql的行号问题