FPGA跨时钟域异步时钟设计的几种同步策略

1 引言

基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。本文总结出了几种同步策略来解决跨时钟域问题。

2 异步设计中的亚稳态

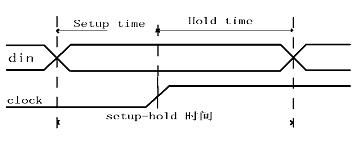

触发器是FPGA设计中最常用的基本器件。触发器工作过程中存在数据的建立(setup)和保持(hold)时间。对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定的最小时间。而保持时间是时钟上升沿到来之后,触发器数据端数据还应该继续保持稳定的最小时间。我们把这段时间成为setup-hold时间(如图1所示)。在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的。如果输入信号在这段时间内发生了变化,输出结果将是不可知的,即亚稳态 (Metastability)。

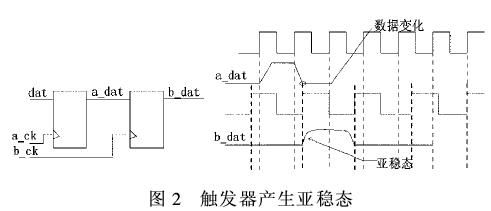

一个信号在过渡到另一个时钟域时,如果仅仅用一个触发器将其锁存,那么采样的结果将可能是亚稳态。这也就是信号在跨时钟域时应该注意的问题。如图2所示。

信号dat经过一个锁存器的输出数据为a_dat。用时钟b_clk进行采样的时候,如果a_dat正好在b_clk的setup-hold时间内发生变化,此时b_ dat就既不是逻辑“1”,也不是逻辑“0”,而是处于中间状态。经过一段时间之后,有可能回升到高电平,也有可能降低到低电平。输出信号处于中间状态到恢复为逻辑“1”或逻辑“0”的这段时间,我们称之为亚稳态时间。

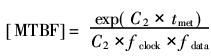

触发器进入亚稳态的时间可以用参数MTBF(Mean Time Between Failures)来描述,MTBF即触发器采样失败的时间间隔,表示为:

其中fclock表示系统时钟频率,fdata代表异步输入信号的频率,tmet代表不会引起故障的最长亚稳态时间,C1和C2分别为与器件特性相关的常数。如果MTBF很大,就认为这个设计在实际工作中是能够正常运行的,不会因为亚稳态导致整个系统的失效。当触发器处于亚稳态,且处于亚稳态的时间超过了一个时钟周期,这种不确定的状态还会影响到下一级的触发器,最终导致连锁反应,从而使整个系统功能失常。

3 同步策略

在异步设计中,完全避免亚稳态是不可能的。因此,设计的基本思路应该是:首先尽可能减少出现亚稳态的可能性,其次是尽可能减少出现亚稳态并给系统带来危害的可能性。以下是根据实际工作总结出来的几种同步策略。

3.1 双锁存器法

为了避免进入亚稳态,应当使参数MTBF尽可能大。通常采用的方法是双锁存器法,即在一个信号进入另一个时钟域之前,将该信号用两个锁存器连续锁存两次(如图3所示)。理论研究表明这种设计可以将出现亚稳态的几率降低到一个很小的程度,但这种方法同时带来了对输入信号的一级延时,需要在设计时钟的时候加以注意。

对于上面的双锁存器法,如果a_clk的频率比b_clk的频率高,将可能出现因为dat变化太快,而使b_clk无法采样的问题。即在信号从快时钟域向慢时钟域过渡的时候,如果信号变化太快,慢时钟将可能无法对该信号进行正确的采样,所以在使用双锁存器法的时候,应该使原始信号保持足够长的时间,以便另一个时钟域的锁存器可以正确地对其进行采样。

3.2 结绳法

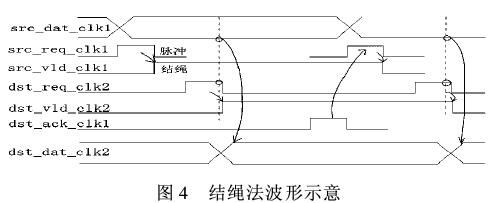

由于双锁存器法在快时钟域向慢时钟域过渡中可能存在采样失效的问题,我们引入了一种安全的跨时钟域的方法:结绳法。结绳法适合任何时钟域的过渡(clk1,clk2的频率和相位关系可以任意选定),如图4所示。

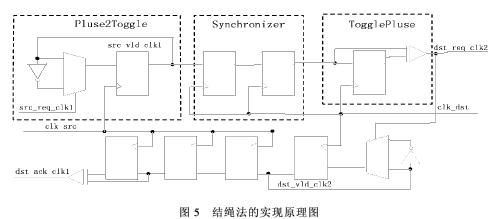

图4中的_clk1表示该信号属于clk1时钟域,_clk2的信号表示该信号属于clk2时钟域。在两次src_req_clk1之间被src_vld_clk1结绳(Pluse2Toggle)。将src_vld—clk1用双锁存器同步以后,该信号转换为dst_req_clk2(Toggle2Pluse)。同理,用dst_vld_clk2将dat_req_clk2结绳,dst_vld_clk2表明在clk2时钟域中,src_dat_clk1已经可以进行正确的采样了。最后将dst_vld_clk2转换为dst_ack_clk1(Synchronizer and Toggle2Pluse)。dst_ack_clk表明src_dat_clk1已经被clk2正确采样了,此后clk1时钟域就可以安全地传输下一个数据了。可以看出,结绳法的关键是将信号结绳以后,使其保持足够长的时间,以便另一个时钟可以正确采样。图5描述了结绳法的具体实现,主要包括3个基本单元:Pluse2Toggle、Synchronizer和Toggle2Pluse。

Pluse2Toggle模块负责将两个脉冲信号结绳,即将单脉冲信号延长;Synchronizer模块用双锁存器法将得到的信号过渡到另一个时钟域;Toggle2Pluse模块与Pluse2Toggle功能相对,即将延长的脉冲信号还原为单脉冲,这里用到了异或门。整体的设计思想就是用Pluse2Toggle将信号延长,用Synchronizer过渡,再用Toggle2Pluse还原,以保证另一个时钟域可以正确采样,而接收方用相反的流程送回响应信号。

结绳法可以解决快时钟域向慢时钟域过渡的问题,且适用的范围很广。但是结绳法实现较复杂,在设计要求较高的场合应该慎用。

4 结束语

本文主要把FPGA异步时钟设计中产生的问题,原因以及解决问题所采用的同步策略做了详细的分析。其中双锁存器法比较适用于只有少数信号跨时钟域;结绳法比较适用快时钟域向慢时钟过渡的情况。所以,在实际的应用中,应根据自身设计的特点选择适当的同步策略。

FPGA跨时钟域异步时钟设计的几种同步策略相关推荐

- 相位同步、频率同步、同相位时钟、同源时钟、同时钟域时钟和异步时钟区别。

相位同步.频率同步.同相位时钟.同源时钟.同时钟域时钟和异步时钟区别. 相位同步.频率同步 相位同步 频率同步 时间同步和频率同步区别: 参考链接 同相位时钟.同源时钟.同时钟域时钟和异步时钟 同相位 ...

- 竞争冒险 亚稳态 跨时钟域 异步fifo

1竞争冒险 竞争冒险存在组合电路中,以下图为例,对于图a中的与门,初始时刻A是高电平,B是低电平,输出Y是低电平.在某一个时刻B先开始跳变,并且达到了与门的VIL(max),此时B被视为高电平,A在某 ...

- 静态定时分析、时钟域与同步化设计

静态定时分析的基本方法是什么?时钟本身的不理想主要表现在哪些方面,在静态定时分析时是如何处理的? Ans:静态定时分析的基本方法: 1.确定延迟路径起点:模块的输入脚.寄存器或触发器的时钟脚. 2.确 ...

- FPGA(五)RTL代码之一(跨时钟域设计)

文章目录 前言 一.异步FIFO 二.异步复位同步释放 三.两级触发器同步 四.握手CDC设计 五.异步双口RAM 总结 前言 这不马上要面试了嘛,有些慌!HDLbits的题目已经刷完了,但又知道自己 ...

- FPGA跨时钟域设计的一点总结

1. 亚稳态的概念说明 是指触发器无法在某个规定时间段内达到一个可确认的状态.当一个触发器进入亚稳态引时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上.在这个稳定期间,触发 ...

- FPGA之道(48)跨时钟域问题

文章目录 前言 跨时钟域问题 什么是跨时钟域问题 解决跨时钟域问题的原理 两级采样法 为什么要对非本时钟域的信号用本时钟域的时钟进行采样呢? 为什么要采样两次呢? 握手法 对于时钟域A: 对于时钟域B ...

- FPGA异步时钟设计中的同步策略

1 引言 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统.但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免. ...

- 数字IC设计——跨时钟域篇1(时钟域)

数字IC设计--跨时钟域篇1 一.时钟域概要 1. CDC介绍 CDC(clock domain crossing)检查(跨时钟域的检查)是对电路设计中同步电路设计的检查.非同步时钟没有固定的相位关系 ...

- FPGA基础知识极简教程(7)详解亚稳态与跨时钟域传输

博文目录 写在前面 正文 FPGA或ASIC中的传播延迟 建立和保持时间是什么? 建立和保持时间与传播延迟和时钟频率有何关系? 如果违反建立和保持时间会发生什么? FPGA中的亚稳定是什么? 亚稳态何 ...

最新文章

- XML之父从愤然亚马逊离职,放弃百万年薪,谷歌华为争抢

- Synergy软件的基本配置/使用(详细教程)

- 快递公司快递单号规律总结

- CodeSmith实体类模板

- .NET Core+MySql+Nginx 容器化部署

- display none的元素重新展示如何撑开页面_寻根问底之——元素隐藏你知多少?

- 东方终焉组引导页自适应html源码 视频背景炫酷

- java 去掉 t_[Java教程]LocalDateTime去掉T

- Linux安装最新版Mono,Jexus(截至2015年12月30日)

- 深度集成 Flink: Apache Iceberg 0.11.0 最新功能解读

- 读书笔记3——《用户故事与敏捷方法》

- 马化腾:这个市场不是拼钱、拼流量,而是拼团队、拼使命感和危机感

- Python数据分析与挖掘实战第三章笔记之贡献度分析代码

- 这位日本网友和谷歌街景的故事,感动了58万人

- 二代身份证号码编码规则

- 黑客常用dos命令详解

- 大数据的概念、特点及应用场景

- centos8 解决yum重装

- 杰理AC692X---开关机实现方式介绍

- 2345看图王去掉“今日热点”弹窗的步骤

热门文章

- linux acl库编译与使用,linux的ACL-rds数据删除了可恢复吗?-WinFrom控件库|.net开源控件库|HZHControls官网...

- oracle的表空间的检查,oracle数据库检查所有表空间使用率的脚本

- python的三种数据类型列举_3.Python编程之数据类型

- 对ObjectMapper的理解及延伸

- EXCEL根据条件随机内插若干行及对应数据

- 三行代码实时追踪你的手,只要有浏览器就够了 | Demo·代码

- 微信AI正在完成:有码走遍天下,从此花钱刷脸

- 喜欢赌球的你,可能被AI盯上了

- 小米首场开发者大会:宣布IoT开发者计划,联手百度提升AI能力

- Javascript下拉刷新