ChipScope Pro内核插入器

ChipScope Pro内核插入器

ChipScope Pro内核插入器的文件后缀名为cdc。在ISE工程中可以创建一个新的cdc程序,也可以在实现流程中激活内核插入器。

注意:使用内核插入器之前,要注意一些工程项目的属性设臵。

(1) 如果采用XST综合工具,将【Keep Hierarchy】属性设置成【Yes】或【Soft】,禁止XST工具对设计的优化,保留原来设计层次,同时也保留了NET网络节点名称。设置方法如下。

选择【Edit】→【Preferences】,打开属性对话框。选择【Processes】页。设臵属性显示下拉框为【Advanced】,单击【OK】。右击【Synthesize】,选择【Properties】选项。设臵【Keep Hierarchy】属性为【Yes】或【Soft】,单击【OK】。

(2) 正确设置比特流生成选项。

在Project Navigator里,单击【Generate Programming File】右键,选择【Properties】选项。选择【Startup options】页。选择【FPGA Start-Up Clock】下拉框,JTAG Clock启动时钟。

接下来,介绍如何在ISE的环境下调用ChipScope的内核插入器(Core Inserter),以及内核插入器的各种参数的含义及其配置方法。

1. 运行ISE 11.1,打开设计的工程项目。

2. 创建CDC文件。在ISE11.1的界面下,有两个创建CDC文件的方法:

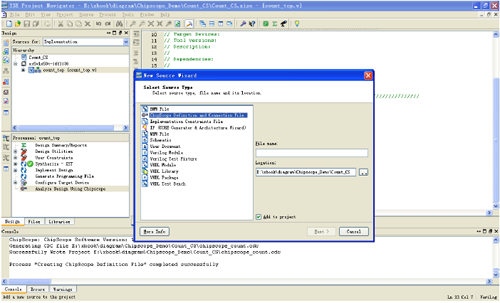

单击选择【Project】→【New Source】,弹出源程序设臵界面,选择【ChipScope Definition and Connection File】,输入文件名,如图9-28所示。单击【Next】,按照缺省设臵产生和配臵调试内核,直到【Finish】生成.cdc文件。

注意:只有安装了ChipScope Pro 11.1,才可以在ISE 11.1的【New Source】里出现【ChipScope Definition and Connection File】。

图9-28 【New Source Wizard】源程序类型选择界面 选择【Project】→【Add Source】(【Add Copy of Source】),选择已经存在的.cdc文件。

图9-28 【New Source Wizard】源程序类型选择界面 选择【Project】→【Add Source】(【Add Copy of Source】),选择已经存在的.cdc文件。

3. ChipScope内核插入器的属性和参数设置。

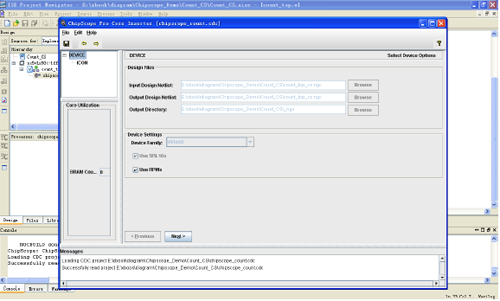

(1) 在【Sources in Project】窗口中,双击cdc文件。弹出的内核插入器界面如图9-29所示,设置Chipscope Pro的参数。

图9-29 内核插入器用户界面

图9-29 内核插入器用户界面

菜单栏中的菜单项及其功能有:

【File】菜单:包含常见的文件操作命令,如【Open Project】、【Save】、【Save As】。【Refresh Netlist】用于手动更新网表。【Edit】菜单:包含创建新的集成逻辑分析单元【New ILA Unit】,或者创建新的ATC2单元【New ATC2 Unit】,删除单元【Remove Unit】,以及参数设臵【Preferences】等命令。【Insert】菜单:包含【Insert Core.】命令,当设臵ILA Core的各项参数后,可以利用这个命令把集成逻辑分析仪的网表插入到原设计的网表中。【Design Files】设计文件选项组,有如下几个选项:

指定输入设计的网表

单击【Browse】,选择输入设计所在的目录

修改输出设计网表和输出目录(如果核插入器在ISE里激活,那么输入网表和输出网表、目录、器件型号等参数自动填入,在这钟情况下,这些参数只能在ISE工程属性中修改,不在核插入器里修改。)

工程参数

【Device Setting】器件设置选项组:

【Device Family】:选择目标FPGA器件家族,内核生成器会生成针对该器件优化的ICON和捕获内核。【Use SRL16s】:用来控制是否用SRL16和SRL16E逻辑生成内核,如果不选择该选项,将会用触发器和多路选择器来代替,影响生成核的大小和性能。缺省设臵为使能。【Use RPMs 】:用来控制是否用相关布局宏(RPMs)生成一个独立的内核,该复选框能阻止布局布线器对区域内放臵ChipScope Pro内核的逻辑进行布局优化。如果设计中占用了大部分的逻辑资源,这些布局限制有可能不被满足。【Core Utilization】选项组:内核生成器的左边是内核资源利用显示窗口,列出插入设计网表中的ChipScope核资源利用情况,包括查找表(LUT), 触发器 (FF)和块RAM (BRAM)。

注意:只有Spartan-3、Spartan-3E、Spartan-3A、Spartan-3A DSP和Virtex-4器件家族显示ChipScope核资源利用特性。

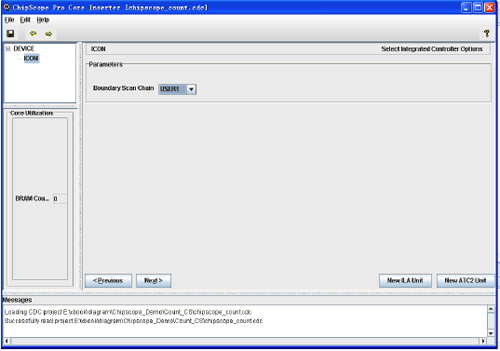

(2) ICON核配置选项设置。在图9-29中单击【Next】,弹出ICON核配置选项设置界面,如图9-30所示。

图9-30 ICON核配置选项界面 【Boundary Scan Chain】下拉选择框:边界扫描链,分析仪可以通过USER1、USER2、USER3或USER4边界扫描链与ChipScope内核通信。(Spartan-3、Spartan-3E、Spartan-3A或Spartan-3A DSP器件不支持该选项。)可以禁止BUFG插入。

图9-30 ICON核配置选项界面 【Boundary Scan Chain】下拉选择框:边界扫描链,分析仪可以通过USER1、USER2、USER3或USER4边界扫描链与ChipScope内核通信。(Spartan-3、Spartan-3E、Spartan-3A或Spartan-3A DSP器件不支持该选项。)可以禁止BUFG插入。

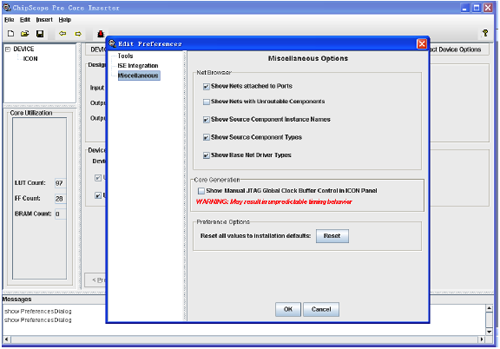

打开【Edit】菜单→【Preferences】属性,弹出【Edit Preferences】属性编辑对话窗,如图9-31所示。

使能JTAG全局时钟缓冲器控制:在【Miscellaneous】选项卡里,【Show Manual JTAG Global Clock Buffer Control in ICON Panel】复选框选中。

禁止JTAG时钟上的BUFG:【Put JTAG Clock on a Global Clock Buffer】复选框不选中。

图9-31 【Edit Preferences】界面

图9-31 【Edit Preferences】界面

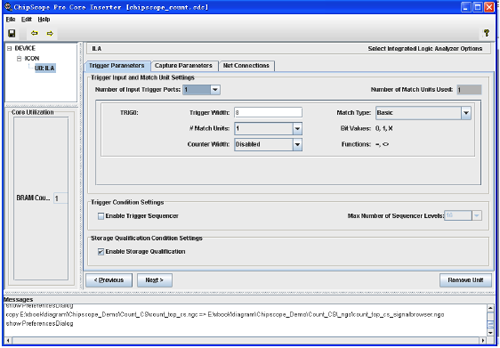

(3) 在图9-30中单击【New ILA Unit】,弹出ILA触发选项和参数设置界面,如图9-32所示。

图9-32 ILA触发选项和参数设置界面

图9-32 ILA触发选项和参数设置界面

Trigger Parameters选项卡:

Trigger Input and Match Unit Settings选项组:

【Number of Input Trigger Ports】下拉列表框:选择ILA核输入触发端口数目,ILA核最多支持16个输入触发端口。每个触发端口的参数在下方列出,包括触发宽度、触发匹配条件判断类型和数目。

TRIGn选项组:

【Trigger Width】编辑框:触发端口由一条或者多条信号线组成,信号线的总数成为触发宽度,最大为256。

【# Match Unit】下拉列表框:触发比较匹配单元是个比较器,和触发端口相连,用于检测触发端口是否满足设定的条件。每个触发端口可以有1~16个触发匹配单元。触发匹配设置单元设置的越多,触发事件就越灵活,但是要占用更多的内部资源。在满足条件的情况下,尽量减少触发匹配单元的数量。

【MatchType】下拉列表框:请参见表9-1。

【Count Width】下拉列表框:匹配单元计数器宽度,用于选择满足匹配条件的次数,最大32位。

Trigger Condition Settings选项组

【Enable trigger condition sequencer】复选框:设臵是否使能触发队列器和队列器深度。触发序列是为了增加触发的复杂性,使触发的条件更加特殊,我们可以把若干个状态组合起来形成触发条件,这样就能更好的使用有限的资源存储有用的数据。

【Max Number of Sequencer levels】下拉列表框:设臵最大的触发条件序列级数。Storage qualification condition Settings选项组

【Enable Storage Qualification】复选框:存储器限制条件。请参考9.2.2小节中的相关内容。

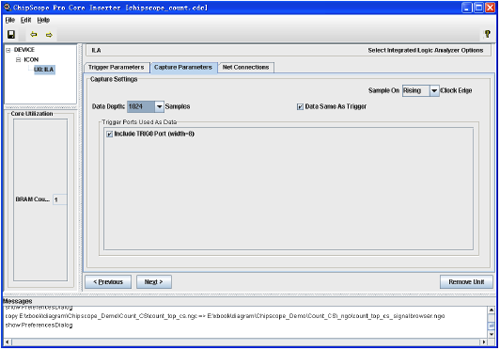

Captures Parameters选项卡:采样参数选项卡(参见图9-33)。  图9-33 【Captures Parameters】参数设置界面 【Sample On】下拉选择框:设臵在时钟的上升沿或者下降沿采集数据。【Data Depth】下拉选择框:设臵ILA核存储的最大数据采样个数。【Data Same as Trigger】复选框:设臵ILA触发端口和数据采集端口是否相同。请参考9.2.2小节中的相关内容。Trigger Port Used As Data选项组:

图9-33 【Captures Parameters】参数设置界面 【Sample On】下拉选择框:设臵在时钟的上升沿或者下降沿采集数据。【Data Depth】下拉选择框:设臵ILA核存储的最大数据采样个数。【Data Same as Trigger】复选框:设臵ILA触发端口和数据采集端口是否相同。请参考9.2.2小节中的相关内容。Trigger Port Used As Data选项组:

如果选中了【Data Same As Trigger】复选框,那么在数据选项的每个TRIGn端口前都会出现一个【Include TRIGn Port】复选框,选中该选项,表明数据和触发端口合并。

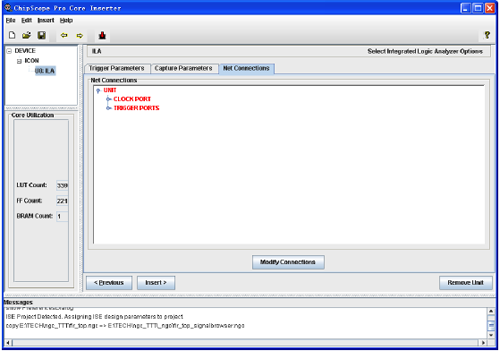

Net connections选项卡(参见图9-34)。

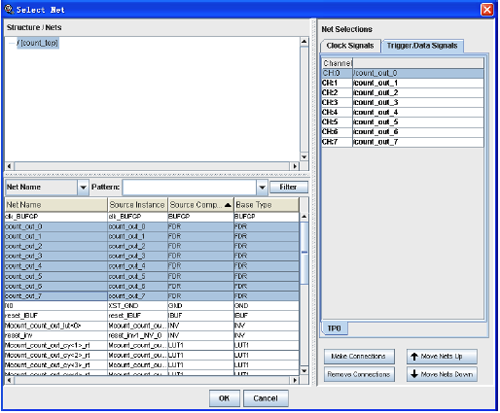

图9-34 【Net connections】网络连接界面 Net Connections选项组:用于将集成逻辑分析仪ILA核的输入信号与设计中的网线连接起来。如果触发和数据信号分离,那么必须指定数据、时钟和触发端口。双击【CLOCK PORT】或者单击【CLOCK PORT】左边的加号(+)。如果还没连接,该选项显示为红色。如图9-34所示,包括【CLOCK PORT】和【TRIGGER PORTS】两组端口的连接。【Modify Connections】按钮:单击该按钮弹出【Select Net】对话框,对话框很容易地将ILA核工作时钟、触发信号、数据信号与设计中的网线连接起来,如图9-35所示。

图9-34 【Net connections】网络连接界面 Net Connections选项组:用于将集成逻辑分析仪ILA核的输入信号与设计中的网线连接起来。如果触发和数据信号分离,那么必须指定数据、时钟和触发端口。双击【CLOCK PORT】或者单击【CLOCK PORT】左边的加号(+)。如果还没连接,该选项显示为红色。如图9-34所示,包括【CLOCK PORT】和【TRIGGER PORTS】两组端口的连接。【Modify Connections】按钮:单击该按钮弹出【Select Net】对话框,对话框很容易地将ILA核工作时钟、触发信号、数据信号与设计中的网线连接起来,如图9-35所示。

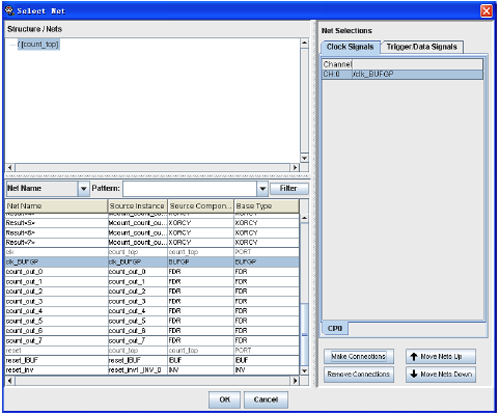

【Structure/Nets】窗格:列出设计的层次结构。

【Net Name】:EDIF网表中的网络名,由于重命名或者综合中的优化原因,可能和HDL中的源码名字不一样。

【Source Instance】:当前综合结果中较低层次的元件例化名称。

【Source Component】:【Source Instance】选项中描述的组件。

【Base Type】:最底层的组件类型,基本类型为原语(primitive)或黑盒子。

【Pattern】编辑框和【Filter】按钮:通过这两个选项,可以有选择地显示设计中可用于ChipScope的网线。

【Remove Connections】按钮:删除当前的连接。

【Move Nets Up】按钮:向上移动连接的位臵。

【Move Nets Down】按钮:向下移动连接的位臵。

【Make Connections】按钮:连接所选择的网络节点和ChipScope内核。  图9-35 【Select Net】界面

图9-35 【Select Net】界面

在【Structure/Nets】中,选择想要连接到ChipScope核的网络节点(可以配合Shift/Ctrl键,选择多个网线)。在【Net Selections】中选择【Clock Signals】、【Trigger Signals】或【Data Signals】选项卡,选择想用于连接网络节点的通道,例如CH0,单击【Make Connections】按钮建立网络节点与ChipScope内核的连接,如图9-36所示。

图9-36 【Select Net】界面

图9-36 【Select Net】界面

ChipScope Pro只能分析FPGA内部逻辑信号,不能直接连接到FPGA的输入,所以输入信号全部以灰色显示,如图9-35所示的clk、reset信号。如果要观察输入信号,可连接此输入信号的输入缓冲器的输出来实现,时钟信号选择相应的BUFGP,如图9-36所示的clk_BUFGP信号,普通信号选择相应的IBUF。

连接完成后,单击“OK”按钮返回连接显示界面,发现所有提示字符“UNIT”、【CLOCK PORT】以及【TRIGGER PORTS】没有红色,则单击【Return Project Navigator】,退出Chipscope,返回到ISE 中。

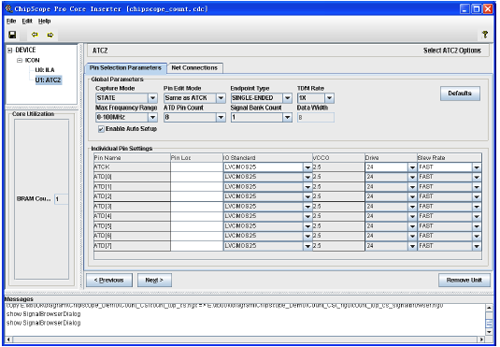

(4) 在图9-30中单击【New ATC2 Unit】,弹出ATC2的选项和参数设置界面,如图9-37所示。

图9-37 ATC2【Pin Selection Parameters】参数设置界面

图9-37 ATC2【Pin Selection Parameters】参数设置界面

Pin Selection Parameters选项卡。

【Capture Mode】下拉选择框:可以设臵成STATE模式和Timing模式,STATE模式用于和CLK输入信号同步的数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由流水线触发器和CLK组成。Timing模式用于异步数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由组合逻辑组成。【Max Frequency Range】下拉列表框:ATC2核的最大频率范围。有效的最大频率选项为0~100 MHz、101~200 MHz、201~300 MHz和301~500 MHz。当【Capture Mode】设臵成【State】,【Max Frequency Range】的选择对ATC2核实现有效。【Pin Edit Mode】下拉列表框:引脚编辑模式,用于设臵引脚是否为一组,如果设臵成【Same as ATCK】一组,那么所有ATD的IO标准、驱动、Slew斜率都和ATCK相同。设臵成【Individual】,则要设臵每个引脚的属性。【ATD Pin Count】下拉列表框:ATD输出引脚数,范围为4~128。【Endpoint Type】下拉列表框:ATCK和ATD输出驱动类型为单端或者差分。【Signal Bank Count】下拉列表框:ATC2核内部包含了一个实时可切换的多路数据信号组选通器,【Signal Bank Count】代表了多路信号选通器的输入信号组数量。有效的信号组为1、2、4、8、16、32或64。【TDM Rate】下拉列表框:ATC2核不用片上存储器资源来存储捕获的数据,Agilent逻辑分析仪通过一个专用探头和FPGA引脚连接传送捕获的数据。ATC2内核数据传送到FPGA引脚上的速率可以和ATC2输入端口DATA的速率相同或者是2倍速率。只有当目标数据捕获方式设臵成【State】时,TDM速率才可以设臵成2倍。【Data Width】:ATC2核的每个输入信号组数据宽度与捕获模式及TDM速率相关。在【State】模式,每个信号组数据端口的宽度等于【ATD Pin Count】ATD引脚数和【TDM Rate】TDM速率的乘积。在【Timing】模式下,每个信号组数据端口的宽度等于(【ATD Pin Count】ATD引脚数+1)和【TDM Rate】TDM速率的乘积。【Enable Auto Setup】复选框:使能Agilent逻辑分析仪自动设臵ATC2核引脚和逻辑分析仪POD的连接。这个属性使得Agilent逻辑分析仪能自动设定每个ATC2引脚的相位和采样电压偏移。缺省状态为使能。

Individual Pin Settings选项组。【Pin Name】引脚名。【Pin Loc】编辑框:设臵引脚的位臵。【IO Standard】下拉列表框:设臵ATCK或每个ATD引脚的I/O标准,标准根据器件和驱动器终端类型而定。【VCCO】:选择【IO Standard】后,VCCO会自动显示该标准对应的输出电压。【Drive】下拉列表框: 设臵引脚输出驱动器的最大输出驱动电流,2~24mA。【SKEW Rate】下拉列表框:设臵ATCK和ATD引脚的信号边沿斜率为FAST或SLOW。

Net connections选项卡:ATC2核网络连接,操作和ILA的网络连接部分一样。Net Connections选项组:用于将ATC2核的输入信号与设计中的网线连接起来。【Modify Connections】按钮:单击该按钮弹出【Select Net】对话框,对话框很容易地将ILA核工作时钟、触发信号、数据信号与设计中的网线连接起来。

4. 单击【Return Project Navigator】,退出内核插入器的配置,返回ISE中。

5. 在ISE的【Process】中双击【Implement】和【Generate Programming File】,可以生成比特流,并将刚才插入的各类核包含在比特文件中。如果只对ChipScope内核插入器修改,不需要重新【Sythesize】综合。

6. 打开ChipScope Analyzer,对采样数据进行分析。ChipScope Analyzer在后面小节中介绍。

ChipScope Pro内核插入器相关推荐

- ChipScope Pro内核生成器应用实例

ChipScope Pro内核生成器应用实例 下面通过一个简单8位计数器的例子,了解如何在工程中添加ChipScope Pro内核生成器的各个IP核,对FPGA内部节点和逻辑进行观测.在该实例中,我们 ...

- ChipScope Pro核生成器

ChipScope Pro核生成器 Xilinx针对不同类型的调试IP核,提供了不同的核生成器.本节重点介绍Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的C ...

- ChipScope Pro分析仪

ChipScope Pro分析仪 ChipScope Pro 分析工具(Analyzer tool)直接与ICON.ILA.IBA.VIO及IBERT核相连,用户可以实时地创建或修改触发条件. 注意: ...

- Linux 内核调试器 调试指南

Linux 内核调试器内幕 KDB 入门指南 Hariprasad Nellitheertha (nharipra@in.ibm.com), 软件工程师, IBM 简介: 调试内核问题时,能够跟踪内核 ...

- 基于windows PE文件的恶意代码分析;使用SystemInternal工具与内核调试器研究windows用户空间与内核空间...

基于windows PE文件的恶意代码分析:使用SystemInternal工具与内核调试器研究windows用户空间与内核空间 ******************** 既然本篇的主角是PE文件,那 ...

- FPGA设计开发软件ISE使用技巧之:片上逻辑分析仪(ChipScope Pro)使用技巧

URL: http://www.icbuy.com/info/news_show/info_id/182769.html 6.7 片上逻辑分析仪(ChipScope Pro)使用技巧 在FPGA的调 ...

- 【FPGA学习】ISE调试助手:逻辑分析仪(ChipScope Pro)

一.chipScope Pro介绍 与Modelsim软件仿真有所不同,chipscope pro是在线式的仿真,更准确的观察数据的变化,方便调试.是一个可以随时监测FPGA数据变化的一个便捷工具,而 ...

- 开源项目-基于Intel VT技术的Linux内核调试器

本开源项目将硬件虚拟化技术应用在内核调试器上,使内核调试器成为VMM,将操作系统置于虚拟机中运行,即操作系统成为GuestOS,以这样的一种形式进行调试,最主要的好处就是调试器对操作系统完全透明.如下 ...

- 基于IntelVt技术的Linux内核调试器 - 2

4 基于IntelVt技术的Linux内核调试器- 调试器设计与实现(2):调试核心 4.1反汇编引擎 如果说调试框架是一个调试器的灵魂,那么接口与反汇编引擎就是一个调试器的身体.我们在调试过程中是要 ...

最新文章

- java自动化开发_Java自动化开发指南

- 初学数位DP--hdu 2089

- Spring Boot 中使用 Hikari,给我整不会了

- Find命令使用详解

- 15.2. important

- java jersey client,如何在Jersey-Client Java中实现重试机制

- 定义css设备类型-Media Queries

- python脚本在centos系统一键卸载重新安装Mysql

- Windows装机必备软件大全,全部支持Vista系统

- SAP FI 系列 (022) - 货币和汇率的配置

- 我转行程序员的那一年(五)

- 开源GIS--geos实现空间连接

- 苹果手机备忘录html转pdf,苹果手机自带的扫描仪,一键便能转成PDF文件,你不会才知道吧...

- Mac计算查看文件Md5

- 一键安装ROS和rosdep(NO 墙)

- 计算机水平cet2是什么等级,英语cet2等级考试试题

- Delphi WebBrowser与网页交互

- [CF936B]Sleepy Game

- python多张图叠加为一张_python实现多张图片拼接成大图

- 工程结算款支付比例_工程进度款的支付比例及付款实例分析

热门文章

- python验证中心极限定理_我竟然混进了Python高级圈子!

- mysql-proxy 0.8.5_主从读写分离----mysql-proxy0.8.5安装与配置

- 温度转换的python程序_Python通过小实例入门学习---1.0(温度转换)

- JS通过正则限制 input 输入框只能输入整数、小数(金额或者现金) 两位小数

- 简单 描述oracle 存储结构,下面的各选项中哪一个正确描述了

- matlab messagebox函数,[MATLAB]在C#中引用MATLAB函数

- java round number,Java Number Math 类

- 字节跳动小程序接入支付功能

- 这些动物,你认识几个呢

- 每年的智能车竞赛赛道是如何产生的?