施密特(smit)触发器

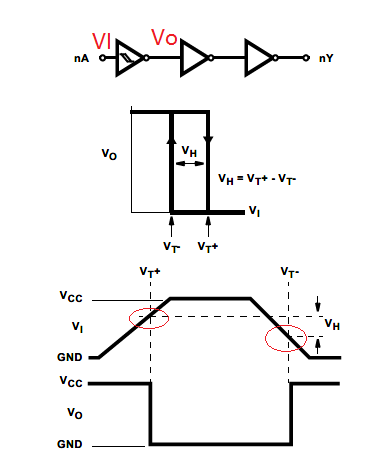

对于不停振荡的输入噪声,我们可以用施密特(smit)触发器来抑制噪声。施密特触发器的输入波形如下所示:

从图中我们可以看到:

当输入从低到高,反相器的翻转电压VT+ > 0.5*vcc;

当输入从高到低,反相器的翻转电压VT- < 0.5*vcc;

这样当输入在0.5*vcc附近波动的时候,只要你的波动范围在VT- 与VT+之间,输出波形如下所示:

跟我们预期的波形是一致的,只是翻转点略微推后一点,多了一点延迟。

下图是一种CMOS smit 触发器架构

假设Vin从0->VDD,M2处于导通上拉状态;

Vx初始电位为VDD,Vout初始电位也为0,所以M4也处于导通上拉状态;这样相对于普通反相器多了一条上拉path,所以翻转电压Vtrig+要变得更大才能使得NMOS M1下拉改变输出Vx由VDD->0 ;

同理Vin从VDD->0,M1处于导通下拉状态;

Vx初始电位为0,Vout初始电位也为vdd,所以M3也处于导通下拉状态;这样相对于普通反相器多了一条下拉path,所以翻转电压Vtrig-变得更小才能使得PMOS M2上拉改变输出Vx由0->VDD;

这里由于翻转点比较敏感,所以对于M4/M3的设计最好选择比较长的length来可以减少工艺误差带来的影响,比如特征尺寸的2倍;在实际设计中,可以在TT corner下先将标准反相器的翻转点调到0.5*vdd的位置,然后再把smit 功能加入得到vtrig+ , vtrig-,最终得到更大的noise margin。注意要用spice dc仿真2次,一次输入从0->vdd,另一次是从vdd->0。

对于内部噪声中大尺寸的mos器件设计而言,首先确认设计是不是一定要用到这么大的size,有时候我们的设计并不是越快越好,只要满足spec且有一定的余量,设计也是没问题的。

如果器件尺寸没法减小,因为大尺寸的器件瞬间在VDD和GND上抽出的电流太大,那我们可以从VDD和GND的角度来处理noise的问题,有以下几个解决方案:

1. 给这些大尺寸器件提供相对独立的VDD和GND,比如从VDD/GND的源头拉一根粗线过去;

2. 将一些对power比较敏感的电路模块远离这些大尺寸器件电路,敏感电路包括一些电压基准电路,高精度放大器等等;

3. 将noise模块与敏感模块的工作时序错开,比如原先的设计是一边放大一边输出,可以改成放大完再输出。这样控制逻辑虽然复杂了一点,但是保证了芯片的正确性

对于内部噪声中的互联线之间串扰,一般以下几种情况要考虑:

- 敏感线的周围,如电压基准信号、高精度放大器的输入信号、高阻线等。这些线就跟游戏里面的智力型脆皮英雄一样,旁边的线稍微动一下,它们就挂了;

对于这种情况,通常可以在敏感线的2侧各放1条GND线保护起来,这样可以应付绝大多数case,但是也遇到fail的情况,有时候需要2侧各放2条GND线确保万无一失。都隔着1/2条河了,你来打我啊。

2 几根routing比较长的数据传输线在layout上放在一起走,这几根数据线都是不停的在传输数据,其中B线是critical path的信号;

对于这种情况,如果线比较少可以用上面的加GND保护线的方法;如果线比较多,通常内部传输线16条、32条、64条一起传的情况还是蛮多的,这样加GND保护线的代价就太大了。假如一条线宽度0.1um,间隔0.1um,加一根GND线就要占用0.2um的空间,如果这些线都是贯穿整个chip的,加个几十条线项目老大估计要哭了。那我们可以稍微让步一点,可以把A B C之间的间距拉开一点,间距越大couple电容产生影响越小。我惹不起你离你远一点还不行。当然具体要多大的间隔,可以结合互联线的couple model进行仿真,这个跟公司用的具体工艺有关。

如果这些线都是同类型的线,我们还可以从设计的角度来削弱couple电容的影响,比如说在这些线变化之前先把它们统一reset到0或1,这样需要变化的线都是向同一个方向变化,大家节奏一致受到的伤害减小。

施密特(smit)触发器相关推荐

- 施密特触发器原理图解

施密特触发器原理图解详细分析 重要特性:施密特触发器具有如下特性:输入电压有两个阀值VL.VH,VL施密特触发器通常用作缓冲器消除输入端的干扰. 施密特波形图 施密特触发器也有两个稳定状态,但与一般触 ...

- 施密特触发器原理图解详细分析

转自:https://blog.csdn.net/chentengkui/article/details/72567762 重要特性:施密特触发器具有如下特性:输入电压有两个阀值VL.VH,VL施密特 ...

- 555定时器的原理与应用(1.1)

一.555定时器 1.1555定时器简介 555定时器是一种多用途的中等规模集成电路.它不仅能用于信号的产生和变换,也可以用于控制和检测电路中.自从Signetics公司于1972年推出这种产品以后, ...

- 单片机数码管显示自行车里程c语言,基于单片机的电动自行车速度与里程表设计...

从传感器得到的矩形脉冲经传输后往往发生波形畸变.当传输线上的电容较大时,波形的上升沿将明显变坏:当传输线较长,而且接受端的阻抗与传输线的阻抗不匹配时,在波形的上升沿和下降沿将产生振荡现象:当其他脉冲信 ...

- 74系列芯片资料下载

74系列芯片资料下载 型号 PDF资料 特性功能 74LS00 下载 4个2输入与非门 74LS01 下载 4个2输入与非门,开路输出 74LS02 下载 4个2输入或非门 74LS03 下载 4个2 ...

- 施密特触发器(Schmitt Trigger)?

施密特触发器(Schmitt Trigger),简单的说就是具有滞后特性的数字传输门. (一)施密特触发器结构举例 (二)施密特触发器具体分析 (三)施密特触发器电路用途 (四)施密特触发器相关部分总 ...

- 555定时器的应用——施密特触发器

转自慕课西安工业大学杨聪锟老师的课程<数字电子技术基础> 施密特触发器 屏蔽5脚干扰 带有干扰信号的输入模拟电压信号,二值逻辑化变数字信号,并且滤掉干扰 功能两点:波形变换,脉冲整形 下降 ...

- 电子设计教程29:滞回比较器(施密特触发器)

为系统增加滞回控制,可以让系统对于微小变化不那么敏感,增强系统的抗干扰能力.本文讨论如何滞回比较器的原理. 单限比较器 比较器一般来说只输出高低电平,如果运放用作比较器,则无需工作在线性区.由 ...

- 74HC04(反相器)和74HC14(反相器、施密特触发器)的具体区别详解

74HC04和74HC14的具体区别详解 同样具有反相器功能,你知道74HC04和74HC14的具体区别吗? 74HC04 对于74HC04很好理解,输入低电平,输出高电平:输入高电平,输出低电平. ...

最新文章

- openresty开发系列34--openresty执行流程之4访问阶段

- CSS 七层叠层顺序(stacking level)

- 那些不回微信的人,都在看什么?

- C语言字符篇(五)内存函数

- 动态规划 - Floyd算法求最短路径 - (Matlab建模)

- php中sha1,PHP中sha1()函数和md5()函数的绕过

- 什么叫显示动力学_通过流体动力学研究找到制作煎饼的最佳方法

- Tomcat中的servlet配置理解

- atitit.木马病毒webshell的原理and设计 java c# .net php.

- 卸载华为系统wifi服务器,如何安装随行WiFi驱动及如何卸载驱动

- 大数据学习开篇:了解大数据导论、清楚大数据应用领域和前景

- YOLOv7官方开源 | Alexey Bochkovskiy站台,精度速度超越所有YOLO,还得是AB

- APP添加人脸识别功能

- micro hdmi引脚定义义_臻实力芯定义:京东AMD笔记本电脑双11开门红

- matlab绘制引力场_玩引力场和漂亮的色彩

- linux如何编写crontab定时脚本,linux下编写定时任务crontab

- OpenSSL 使用拾遗(二)---- X509 证书的 SKID/AKID 字段

- 电子商务概论 # ch1 电子商务框架与模式

- 计算机编程pid计算机,什么是pid号?如何使用PID编号结束过程

- 2.3W字,这可能是把Nginx讲得最全面的一篇文章了,建议收藏备用