FPGA期末项目 | 数字时钟

戳这里下载整个项目包(已上传到CSDN资源库)

一、实验设备

FPGA开发平台、计算机、其它外接器件

二、需求分析(选题的意义、功能要求等。。。这里有点水,小伙伴们可以选择性跳过)

选题的意义:个人认为本项目(《数字时钟》)的选题意义有二,其一,时钟和闹钟早已是老生常谈的日常工具,利用课堂上所学习的知识贯通运用到现实生活中,作为操作实践,具有一定的现实意义;其二,数字时钟的功能设计囊括了数码管、LCD屏、开关运用、管教分配等知识,能够对本学期所学的实验知识做一个挽接,在知识的总结上也具备一定意义;

功能要求:

1.用数码管显示时、分、秒:分为两个界面,即时钟界面以及闹钟设置界面,显示时钟的时分秒以及闹钟的时分秒,可以通过开关切换显示,是项目的基本功能;

2.能按比例缩短时间调试:调控时钟或闹钟的频跳速度,方便演示和调试;

3.闹钟功能:用户可以通过sw8切换进入闹钟界面,再利用sw1-3设定具体的闹钟时间,到点即响,同样是项目的基本功能;

4.用LCD屏显示日期(年月日)以及祝福语:作为时钟,显示年月日的功能个人觉得也是有必要的,另外关于祝福语,我们对实验和知识的学习其实本身就是快乐的过程,生活也没有必要每天都过得毫无色彩、千篇一律,所以怀揣着这份情怀呢,我在本项目中加了一个显示祝福语的功能,意在表达自己的这份对科学和生活的热爱以及学习的热情。

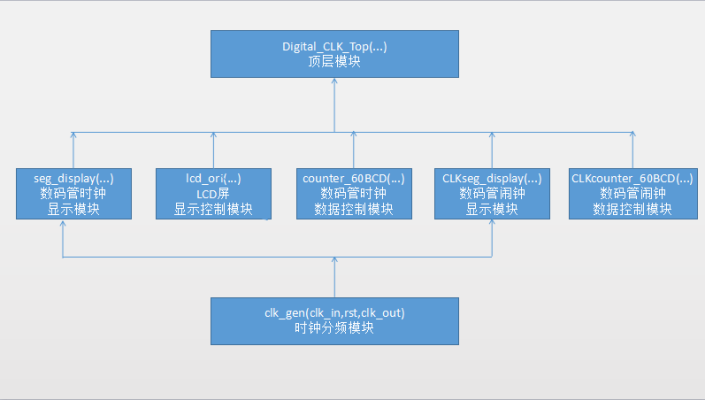

三、系统框架介绍(系统结构图,各模块的功能及端口介绍,等)

系统结构图如下所示:

各模块的功能及端口介绍:

(这里的模块功能和端口做简要的介绍,详细的用法请移步至《设计思路》部分)

1.Digital_CLK_Top(clk_50M, Reset_n, seg7,ledcom,key,beep,

LCD_ON1,LCD_BLON1,LCD_RS1,LCD_RW1,LCD_EN1,LCD_DATA1);

功能:顶层模块,调用其他子模块,统筹整个系统的功能;

端口:

clk_50M, //系统时钟输入

Reset_n, //系统复位输入

seg7, //数码管显示输出位

ledcom, //数码管位置调控输出位

key, //开关输入号位,主要使用于CLKcounter_60BCD

beep, //蜂鸣器输出信号

LCD_ON1, //LCD供电电源开关

LCD_BLON1, //LCD背景电源开关

LCD_RS1, //寄存器选择信号

LCD_RW1, //液晶读写信号

LCD_EN1, //液晶时钟信号

LCD_DATA1, //LCD的数据端口

2.lcd_ori(LCD_ON,LCD_BLON,LCD_RS,LCD_RW,LCD_EN,LCD_DATA,CLK);

功能:LCD屏显示控制模块,用于控制LCD屏显示年月日以及祝福语;

端口:

LCD_ON, //LCD供电电源开关

LCD_BLON, //LCD背景电源开关

LCD_RS, //寄存器选择信号

LCD_RW, //液晶读写信号

LCD_EN, //液晶时钟信号

LCD_DATA, //LCD的数据端口

CLK, //模块时钟输入(项目中输入的是clk_50M)

3.seg_display(clk,rst_n,mimute_cnt,second_cnt,hour_cnt,ledcom,seg7);

功能:基于视觉暂留知识,控制时钟界面数码管的显示;

端口:

clk, //模块时钟输入

rst_n, //复位信号输入

mimute_cnt, //分钟位数据输入

second_cnt, //秒位数据输入

hour_cnt, //时位数据输入

seg7, //数码管显示输出位

ledcom, //数码管位置调控输出位

4.counter_60BCD(clk, rst, couter_o,flag);

功能:在顶层模块调用,根据输入的时钟和时|分|秒位数据进行对应的加一计算和进位计算,并在溢出(分秒59加一溢出,时23加一溢出)时返回一个flag供顶层模块使用;

端口:

clk, //模块时钟输入

rst, //复位信号输入

couter_o, //数字时钟部分的时|分|秒位数据输出

flag, //输出一个溢出进位标志

5.clk_gen(clk_in,rst,clk_out); //clk_in=50MHz

功能:对输入的50MHz的系统时钟分频,调用时根据CLK_DIV变量的复用情况进行运算并返回对应的时钟分频结果;

端口:

clk_in, //模块时钟输入,在顶层模块

rst, //复位信号输入

clk_out, //时钟分频结果输出

6.CLKseg_display(clk,rst_n,mimute_cnt,second_cnt,

hour_cnt,CLKmimute_cnt,CLKsecond_cnt,CLKhour_cnt,ledcom,seg7,sw8);

功能:基于视觉暂留知识,控制闹钟设置界面数码管的显示,并基于sw8的状态控制切换数码管屏显示;

端口:

clk, //模块时钟输入

rst, //复位信号输入

mimute_cnt, //分钟位数据输入(时钟)

second_cnt, //秒位数据输入(时钟)

hour_cnt, //时位数据输入(时钟)

CLKmimute_cnt,//分钟位数据输入(闹钟设置)

CLKsecond_cnt,//秒位数据输入(闹钟设置)

CLKhour_cnt, //时位数据输入(闹钟设置)

seg7, //数码管显示输出位

ledcom, //数码管位置调控输出位

sw8 //开关8的输入信号

7.CLKcounter_60BCD(clk, rst, couter_o,flag,sw);

功能:在顶层模块调用,根据输入的时钟频率clk和时|分|秒位数据进行对应的加一计算和进位计算,并在溢出(分秒59加一溢出,时23加一溢出)时返回一个flag供顶层模块使用;

端口:

clk, //模块时钟输入

rst, //复位信号输入

couter_o, //数字闹钟设置部分的时|分|秒位数据输出

flag, //输出一个溢出进位标志

sw //开关输入位,作为key的接收变量

四、设计思路(每个模块的设计思路,文字结合示意图等进行介绍)

1.Digital_CLK_Top(clk_50M, Reset_n, seg7,ledcom,key,beep,

LCD_ON1,LCD_BLON1,LCD_RS1,LCD_RW1,LCD_EN1,LCD_DATA1);

功能:顶层模块,调用其他子模块,统筹整个系统的功能;

思路:

A.复用两次分频模块clk_gen,产生两个速度不一样的时钟频——clk_second和clk_second2,分别用来驱动数字时钟和数字闹钟设置;

B.复用三次时钟控制模块counter_60BCD:

第一次,用clk_second作为时钟频输入,传入second_cnt给couter_o作为秒位数据承载,MODULEofCNT设置为60,模块每溢出一次(即每计数到60个秒),产生一个flag,即flag_min;

第二次,用flag_min作为时钟频输入,传入minute_cnt给couter_o作为秒位数据承载,MODULEofCNT设置为60,模块每溢出一次(即每计数到60个分),产生一个flag,即flag_hour;

第三次,用flag_hour作为时钟频输入,传入hour_cnt给couter_o作为秒位数据承载,MODULEofCNT设置为24,模块每计数到24个时溢出一次;

C.复用三次闹钟控制模块CLKcounter_60BCD:

第一次,用clk_second2作为时钟频输入,传入CLKsecond_cnt给couter_o作为秒位数据承载,MODULEofCNT设置为60,sw位传入key[2]信号,即sw3的状态信号;

第二次,用clk_second2作为时钟频输入,传入CLKminute_cnt给couter_o作为秒位数据承载,MODULEofCNT设置为60,sw位传入key[1]信号,即sw2的状态信号;

第三次, 用clk_second2作为时钟频输入,传入CLKhour_cnt给couter_o作为秒位数据承载,MODULEofCNT设置为24,sw位传入key[0]信号,即sw1的状态信号;

D.复用LCD屏控制显示模块lcd_ori,根据本函数定义的变量复用对应的参数;

E.复用闹钟数码管控制显示模块CLKseg_display,根据本函数定义的变量复用对应的参数;

F.接下来,编写了一个状态机,主要设置并使用了state0、state1、state2等三个状态;

state0状态:使用if判断语句

if(second_cnt==CLKsecond_cnt&&minute_cnt==CLKminute_cnt&&hour_cnt==CLKhour_cnt)

等一个在闹钟界面模块设置的时分秒数列,等到这个数列的时候转跳到state1或state2,并设置好蜂鸣器鸣响的延时时间到变量cnt_2;

state1、state2:在计数变量cnt_2归零之前,一直给蜂鸣器管脚输出高电平,直到计数变量cnt_2归零,输出为低电平,停止蜂鸣器鸣响;

2.lcd_ori(LCD_ON,LCD_BLON,LCD_RS,LCD_RW,LCD_EN,LCD_DATA,CLK);

功能:LCD屏显示控制模块,用于控制LCD屏显示年月日以及祝福语;

思路:

A.将年月日以及祝福语分别编写成字符串,再分别付给变量lcd_buf_first、data_first和lcd_buf_second、data_second;

B.准备好状态参数常量——

clear_lcd、

set_disp_mode、

disp_on、

shift_down、

write_data_first、

write_data_second;

基于状态机思想,并用current_state变量承载状态常量;

C.初始化LCD模块;

D.clear_lcd状态, 清屏并光标复位 ;

set_disp_mode: 设置显示模式:8位2行5x8点阵;

disp_on: 显示器开、光标不显示、光标不允许闪烁 ;

shift_down: 文字不动,光标自动右移;data_first赋值给lcd_buf_first;

write_data_first、write_data_second: 用于写入数据

default: 若current_state为其他值,则将current_state置为clear_lcd;

3.seg_display(clk,rst_n,mimute_cnt,second_cnt,hour_cnt,ledcom,seg7);

功能:基于视觉暂留知识,控制时钟界面数码管的显示;

思路:

A.复用分频模块clk_gen分频出一个时钟clk_div,周期约为0.1s;

B.设置一个8位的变量cnt,基于clk_div进行递加一,并在0到满位溢出之间循环(满位溢出时将之归零,再继续加一处理);

C.基于快速递加一的变量cnt,在每个clk时钟上升沿来的是时候,取其低三位(八个数码管格位,刚好三位二进制数可以完整表示)进行case处理,

每个case的子状态中,根据cnt低三位的值,把对应的表示数码管位置的二进制数赋值给ledcom,用于选择数码管格位;再把对应的数据(如秒位数据的低四位second_cnt[3:0],高四位second_cnt[7:4]等)传给dis变量; dis的用法是在下一个always模块里面,case判断dis的值,根据dis的值把对应的二进制数传给seg7变量,用于基于ledcom选择数码管格位之后,显示格位里面的内容;

由此,基于快速跳变的clk时钟和clk_div时钟,ledcom的值也不断地快速变换,由此数码管的每个格位都在被快速地选择和显示,于是这样便是通过了视觉暂留效应,实现了数码管时钟的显示;

4.counter_60BCD(clk, rst, couter_o,flag);

功能:在顶层模块调用,根据输入的时钟和时|分|秒位数据进行对应的加一计算和进位计算,并在溢出(分秒59加一溢出,时23加一溢出)时返回一个flag供顶层模块使用;

思路:

A.将MODULEofCNT(分别通过/10和%10运算)切成5/2和9/3两个数,并分别付给变量a和b;

B.通过a和b判断是对分秒位数据(MODULEofCNT为60)还是对时位数据(MODULEofCNT为24)进行计算;

若是分秒位数据:先对couter_o[7:4]进行判断,若小于5,则对couter_o[3:0]判断,若couter_o[3:0]小于9,则couter_o[3:0]数据加一,若couter_o[3:0]不小于于9,则couter_o[3:0]归零处理,couter_o[7:4]加一;若couter_o[7:4]不小于5,则对couter_o[3:0]判断,若couter_o[3:0]小于a(9),则couter_o[3:0]数据加一,若couter_o[3:0]不小于于a(9),则couter_o八个位都归零,并返回一个溢出进位flag(flag<=1);

若是时位数据:逻辑同上,只将b替换为2,将a替换为3进行处理即可;

5.clk_gen(clk_in,rst,clk_out); //clk_in=50MHz

功能:对输入的50MHz的系统时钟分频,调用时根据CLK_DIV变量的复用情况进行运算并返回对应的时钟分频结果;

思路:简单地基于系统时钟clk_in以及可复用的参数CLK_DIV实现分频的功能;

6.CLKseg_display(clk,rst_n,mimute_cnt,second_cnt,

hour_cnt,CLKmimute_cnt,CLKsecond_cnt,CLKhour_cnt,ledcom,seg7,sw8);

功能:基于视觉暂留知识,控制闹钟设置界面数码管的显示,并基于sw8的状态控制切换数码管屏显示;

思路:

A.复用分频模块clk_gen分频出一个时钟clk_div,周期约为0.1s;

B.(基于sw8的状态控制切换数码管屏显示)If语句判断sw8时候为高电平,如果是,则将CLKsecond_cnt、CLKmimute_cnt、CLKhour_cnt系列数据付给dis变量,如果不是则将second_cnt系统数据付给dis变量;细节处如cnt、ledcom、dis、case(cnt[2:0])等用法则跟seg_display模块的设计思路相同;

7.CLKcounter_60BCD(clk, rst, couter_o,flag,sw);

功能:在顶层模块调用,根据输入的时钟频率clk和时|分|秒位数据进行对应的加一计算和进位计算,并在溢出(分秒59加一溢出,时23加一溢出)时返回一个flag供顶层模块使用;

思路:同counter_60BCD模块的设计思路;

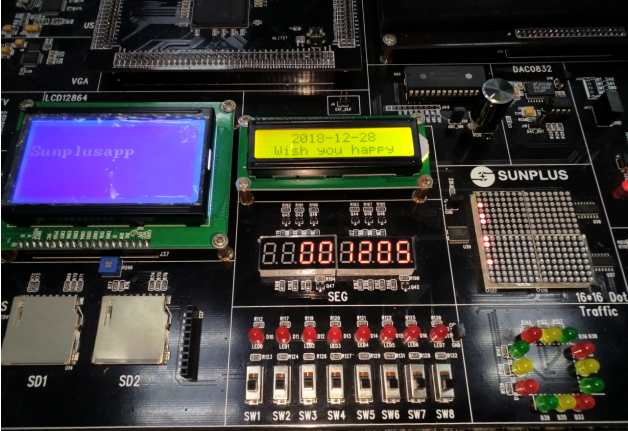

五、实验结果

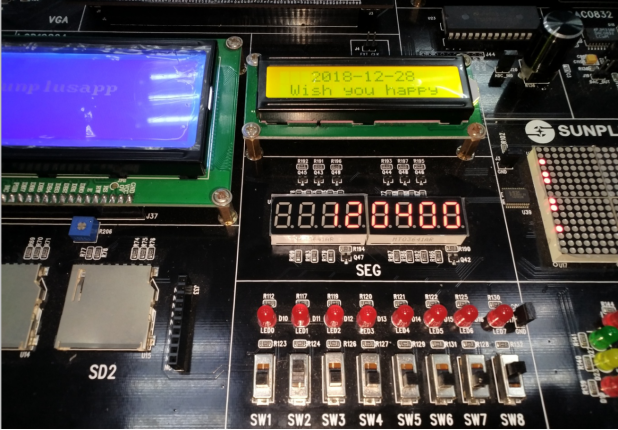

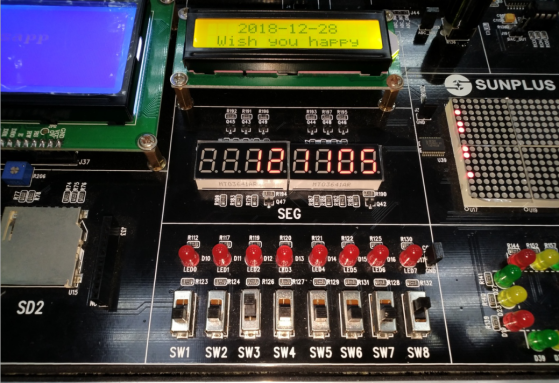

1.开机状态,初始为数字时钟界面,下图为数码管上规则地显示闪动的时钟,通过分频模块的参数调改可以改变其速度;

LCD屏上显示具体的日期(年月日)以及祝福语(Wish you happy/happiness——祝你幸福),开关状态为全数低电平:

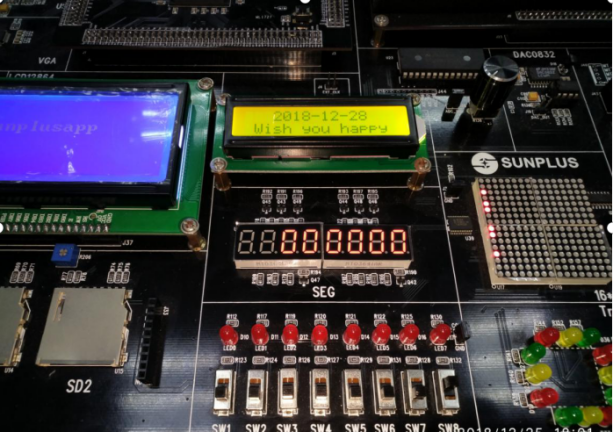

2.上推sw8,令之输出为高电平,数码管即切换到闹钟设置界面:

3.上推sw1,令之输出为高电平,数码管闹钟界面上“时”数位持续加一(图中已加到06):

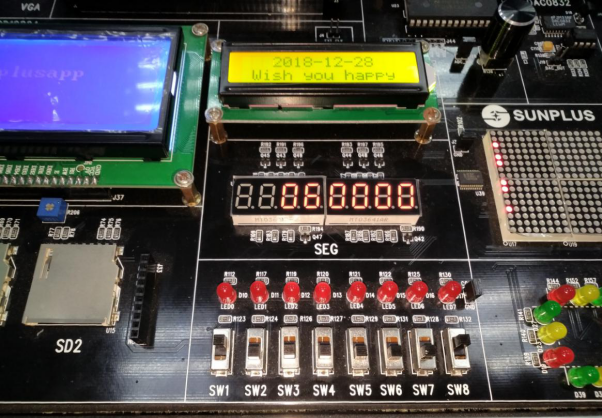

4.上推sw2,令之输出为高电平,数码管闹钟界面上“分”数位持续加一(图中已加到04):

5.上推sw3,令之输出为高电平,数码管闹钟界面上“秒”数位持续加一(图中已加到05):

6.数码管停留在设置闹钟界面的时候,数字时钟一直也在后台跑动,当我们设置完闹钟,将开关全数归为低电平时,数码管界面回切到数字时钟界面,数字时钟上的时间到达闹钟设计的点时,会启动蜂鸣器,产生一个时长为三秒(可以在程序中设置时长)的鸣响作为闹钟。

六、实验项目代码清单

1.Digital_CLK_Top.v

顶层文件,用于调用诸多要使用的模块;

2.Tcl_2c35_script1.tcl

管教分配的脚本文件,描述管教的分配;

3.lcd_ori.v

LCD屏模块,实现LCD屏显示年月日以及祝福语的功能;

4.seg_ex.v

5.seg_display.v

时钟模块的数码管显示的相关模块文件;

6.counter_60BCD.v

关于实现时钟界面显示的后台数字计算(相关变量的加一和进位操作等)的文件;

7.clk_gen.v

时钟分频模块,用于实现各种参数频率的分频;

8.CLKseg_display.v

闹钟模块的数码管管显示的相关模块文件;

9.CLKcounter_60BCD.v

关于实现闹钟界面显示的后台数字计算(相关变量的加一和进位操作等)的文件。

FPGA期末项目 | 数字时钟相关推荐

- 基于FPGA的遥控数字时钟设计

基于FPGA的遥控数字时钟设计报告 Author:张宏宇 摘要 数字时钟是一种通过数字显示时间的计时装置,本次项目采用Cyclone Ⅳ系列芯片,使用QuartusII开发环境,使用Ver ...

- FPGA初学记录——数字时钟系统搭建(上)

FPGA初学记录--数字时钟系统搭建(上) 野火征途Pro开发板教程--数码管动态展示拓展训练,数字时钟系统搭建 文章目录 FPGA初学记录--数字时钟系统搭建(上) 前言 一.问题简述 二.功能解析 ...

- 基于FPGA的简易数字时钟

基于FPGA的可显示数字时钟,设计思路为自底向上,包括三个子模块:时钟模块,进制转换模块,led显示模块.所用到的FPGA晶振频率为50Mhz,首先利用它得到1hz的时钟然后然后得到时钟模块,把时钟模 ...

- FPGA芯片结构(可编程输入输出单元IOB/可配置逻辑块CLB/数字时钟管理模块DCM/ 嵌入式块RAM(BRAM)/丰富的布线资源/ 底层内嵌功能单元/内嵌专用硬核)

目前主流的FPGA仍是基于查找表技术的,已经远远超出了先前版本的基本性能,并且整合了常用功能(如RAM.时钟管理 和DSP)的硬核(ASIC型)模块.如图1-1所示(注:图1-1只是一个示意图,实际上 ...

- 基于 FPGA 实现滑动显示、多功能数字时钟【设置年月日时分秒以及闹钟】

目录 一.数码管原理 二.基础篇 2.1 原理及代码 2.2 验证结果 三.进阶篇 3.1 原理及代码 3.2 验证结果 四.数字时钟 4.1 原理及代码 4.2 验证结果 本文内容:基于 FPGA ...

- 基于FPGA的数字时钟的设计课设(HUAT)

目录 前言 一.数字时钟课设目标 二.部分代码 1.clock.v代码的编写 2.完整代码 3.仿真代码 总结 前言 学校黄老师的FPGA的设计课设,最后的课设为数字时钟,实现分时的计数功能,带有整点 ...

- FPGA学习之 状态机实现数码管的数字时钟

FPGA学习之 状态机实现数字时钟 开发板型号:EP4CE6F17C8 六位数码管原理图: 由图可知,数码管段选和片选均为低电平有效. 由于人眼的视觉残留,我们控制一定频率对每一位数码管进行刷新,就能 ...

- 基于FPGA的数字时钟设计

基于FPGA的数字时钟设计 芯片与开发板 技术指标 1.具有正常的日时分秒技术显示功能,用七个数码管分别显示日,时,分,秒. 2.有按键校日,校时,校分,校秒. 3.利用led模拟整点报时功能. 4. ...

- 基于FPGA数字时钟的设计(附源码)

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分.大侠可以关注"FPGA技术江湖"微信公众号,在"闯荡江湖"."行侠仗义"栏里获取其 ...

最新文章

- startuml如何画流程图_因为流程图没画好SCI被拒稿!看完师姐的攻略后我被吊打了!...

- 【解决方法】Panda read_csv()把第一行的数据变成了列名,怎么处理

- ntdll 异常代码0xc0000374_不要把异常当做业务逻辑,这性能可能你无法承受

- 网站“注册流程”如何“照顾用户”?

- 哨兵机制服务器环境准备

- asp.net 4.0 新特性(翻译)

- html怎么控制进度条,HTML如何实现进度条?附源码

- 为了永不停机的计算服务 | 凌云时刻

- 微生物组-扩增子16S分析和可视化(2023.2)

- 计算机设备如何巡检,计算机联锁设备巡检作业指导书.pdf

- 台式计算机怎么放光盘,用台式电脑怎么放DVD

- 金山WPS笔试题总结

- Bugku MISC 再也没有纯白的灵魂

- webshell一句话

- 洛谷 P5594 【XR-4】模拟赛 视频讲解(二维数组、模拟)

- onclick事件在苹果手机上失效

- BERT-BiLSTM-CRF模型代码

- RabbitMQ 客户端源码系列 - Channel

- 简单网页设计(苍兰诀)html+css

- the definitive antlr 4 reference ANTLR是什么