镁光256Gb NAND Flash芯片介绍

总体概述

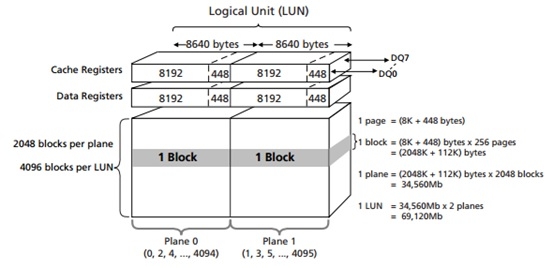

该芯片是一款典型的大容量NAND Flash存储颗粒,支持Open NAND Flash Interface (ONFI) 2.1的接口标准,采用ONFI NANDFlash的操作协议。该芯片采用Multiple-level Cell (MLC)技术,根据不同的容量,一个芯片内部封装了多个DIE(LUN),每个DIE由两个Plane构成,一个Plane可以分成2048个Block,每个Block由256页组成,一个页的大小为8KB+448B的组织结构方式。

在性能方面,一个Page页的读延迟在50us左右,页编程时间为900us,块擦除时间长达3ms。每个块的标称擦除寿命达到5000次。

芯片接口及信号

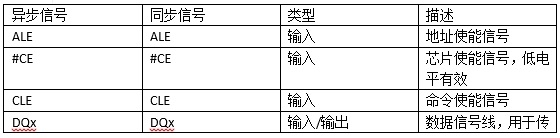

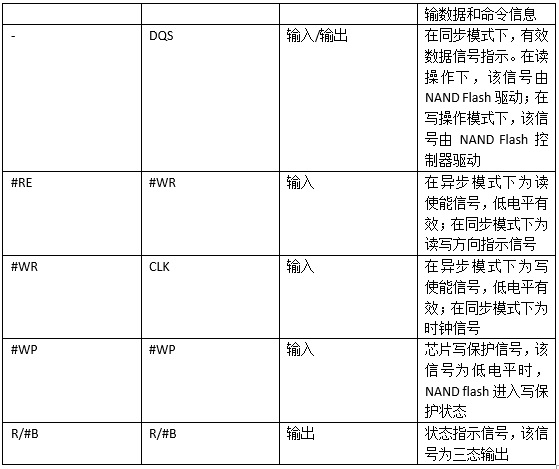

镁光的芯片支持同步和异步两种接口模式。在异步接口模式下,采用5个控制信号,分别为#CE,CLE,ALE,#WE和#RE,另外#WP用于控制芯片的写保护,R/#B用于检测芯片的当前状态。在同步操作模式下,#WR引脚为时钟输入信号,#RE信号为读写方向指示信号。

NAND Flash的接口信号具体定义如下:

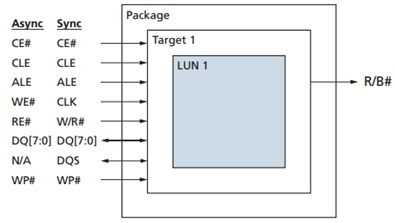

一个NAND Flash物理芯片可以由多个DIE(或者称之为LUN)的单元构成,每个DIE会有一套独立的上述提及的控制信号线。一个DIE中会存在若干个Plane,每个Plane有许多Block单元组成,一个Block单元是一个最小的擦除单位,并且有数量较多的Page页构成,每次写的最小单元就是一个Page页。对于容量较小的芯片,芯片厂商只会封装一个DIE,每个DIE的内部结构如下图所示:

对于镁光512Gb芯片,一个DIE内部集成了两个Plane,通过一套控制信号线和寄存器控制内部的两个Plane同时并发工作。值得一提的是,多个DIE(LUN)可能会共享一套控制信号线,因此,在物理上多个DIE会被封装成一个Target。需要注意的是,同一个Target内部的DIE虽然共享了物理信号线,但是寄存器都是相互独立的。因此,从结构上来看,一个NAND Flash的内部架构可以只由一个DIE(LUN)构成,如下图所示:

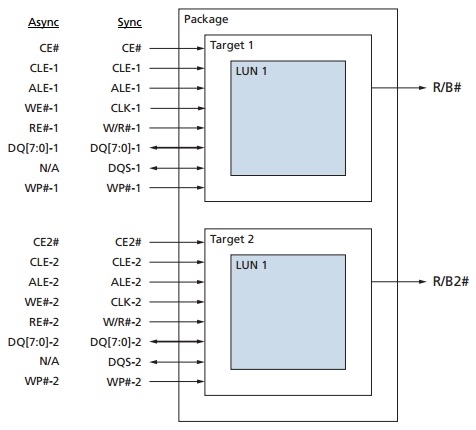

也可以在一个芯片中集成多个DIE(LUN),每个DIE拥有一套独立的物理信号线,如下图所示:

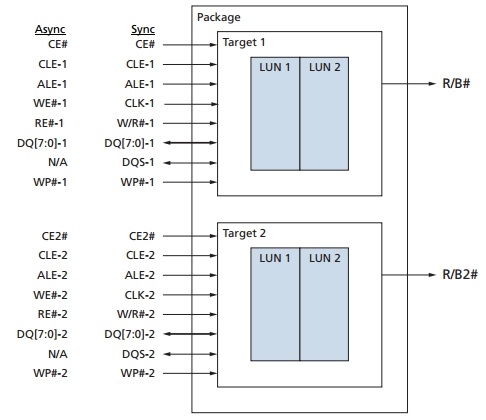

在高密的封装中,没有那么多的物理信号线,那么同一个Target中会集成多个DIE(LUN),如果下图所示:

无论如何去封装,每个DIE(LUN)中的基本结构是相同的。

NAND Flash存储单元

NAND Flash中一个DIE(LUN)中的存储单元通常由多个Plane构成,其结构如下:

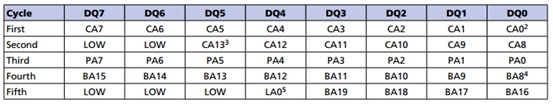

上图所示的一个Page页大小为8KB,考虑到spare area的448字节空间,因此需要14位地址访问一个page页,即地址信号的最低14位为页内地址。一个block块内部有256个page页,需要8位地址(Page address,PA)信息去访问一个block块内部的不同page页。一个Plane内部存在2048个block块,需要11位(Block address,BA)去访问一个Plane中的不同block块。一个DIE(LUN)中存在2个Plane,需要一位地址位去访问一个DIE中的不同Plane。因此,40位地址信息的定义如下表所示:

CA0~CA13为页内偏移访问地址信息,PA0~PA7为页地址信息,BA8为DIE中的Plane选择地址位,BA9~BA19为DIE中的块地址信息,另外,LA0为一个Target中的DIE(LUN)选择地址位,在该NANDFlash芯片中,一个Target中可以集成2个DIE。

在每个Plane单元中都存在两个寄存器:一个为cache寄存器;另一个为data寄存器。Cache寄存器的作用是缓存NAND Flash控制器输入的数据,而data寄存器的作用是提升数据读取和写入的性能,数据传输和数据加载之间的操作。在数据读取和数据写入的过程中,都提供了流水并发操作模式,这类模式都充分利用了这个data寄存器。

读写操作时序

镁光的NAND Flash芯片提供了两种操作模式,一种为异步操作模式;另一种为同步操作模式。异步操作是一种比较传统的接口模式,NAND Flash和控制器处于两个时钟域,所有的信号在数据传输过程中都需要进行同步操作,因此性能比较差。同步操作由外部提供参考时钟,NAND Flash和控制器处于同一个时钟域,可以获取较高的读写性能。

异步操作

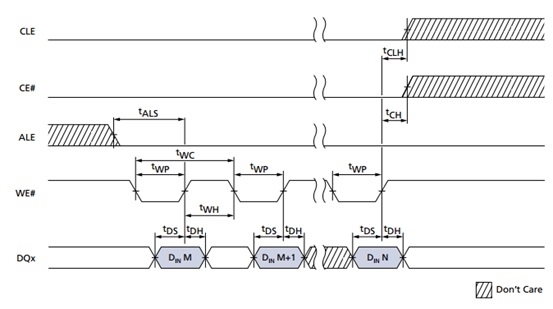

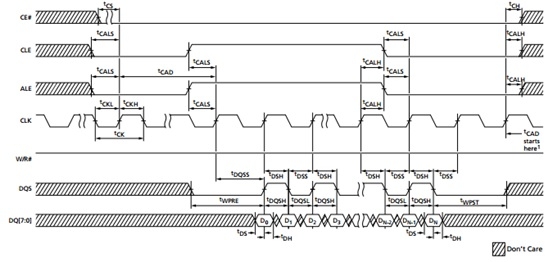

异步操作模式非常适合单片机之类的控制器对其进行操作,不需要特殊的NAND Flash控制器,普通的总线操作就可以对NAND Flash进行控制操作。异步数据写操作的时序如下图所示:

在#WE信号的驱动下,DQ总线上输入对应的数据,并且在#WE信号上升沿之后需要保持tDH时间。在#WE信号上升沿驱动下,DQ总线上的数据被锁存到NAND Flash的数据寄存器中。

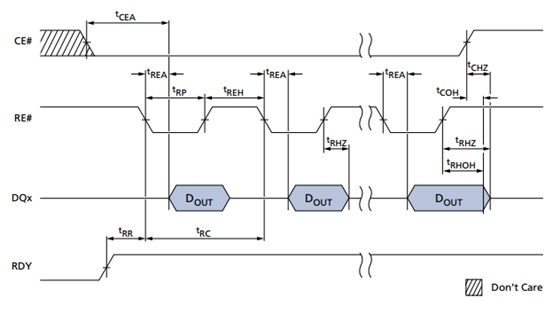

在RDY信号为高电平时,说明可以从NAND Flash指定位置中读取数据,读操作的时序如下图所示:

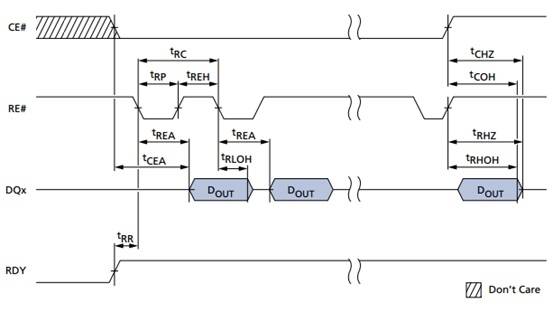

在读信号#RE的下降沿驱动下,数据从NAND Flash中输出到数据总线DQ上。NAND Flash控制器可以在#RE信号的上升沿采样数据总线DQ上的数据。当NAND Flash控制器给定的读信号频率较快时,通过#RE上升沿信号无法正确采样数据总线上的数据时,可以通过下一个#RE信号的下降沿采样总线上的输出数据。如下图所示:

因此,在异步总线操作时,需要考虑#RE读信号频率和tRC之间的时间关系。通过这个时间关系来确定具体的读数据采样方式。

同步操作

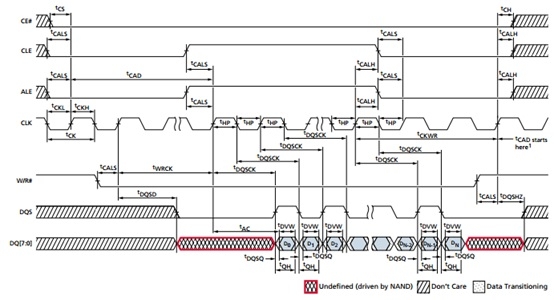

同步操作是一种高速接口,和DDR内存接口类似,可以通过上下沿同时采样的方式提升数据传输效率。在同步模式下,时钟信号需要外部持续不断的输入,NAND Flash通过控制ALE、CLE、#CE、W/#R、DQS信号来控制数据的输入和输出。在同步模式下的数据输入时序如下图所示:

DQS信号由NAND Flash控制器驱动,并且和时钟信号同频同相。在CLK时钟信号的上升沿和下降沿将总线上的数据锁存到NAND Flash内部的寄存中。为了能够让NAND Flash在DQS的上升沿和下降沿采样到总线上的数据,在沿变化之前,NAND Flash控制器需要在总线DQ上准备好写入的数据。

当RDY信号为高电平时,表明可以从NAND Flash中输出数据。在读操作的时候,数据总线DQ、总线指示信号DQS需要由NAND Flash控制,控制器需要释放对这些信号线的控制。数据读总线操作时序如下图所示:

可以发现总线数据锁存信号DQS和时钟信号CLK同频,但是会存在一定的相差,这样NAND Flash控制器可以通过CLK时钟信号的双沿变化对总线上的数据进行采样,从而可以正确的读取NAND Flash中的数据。

NAND Flash操作命令

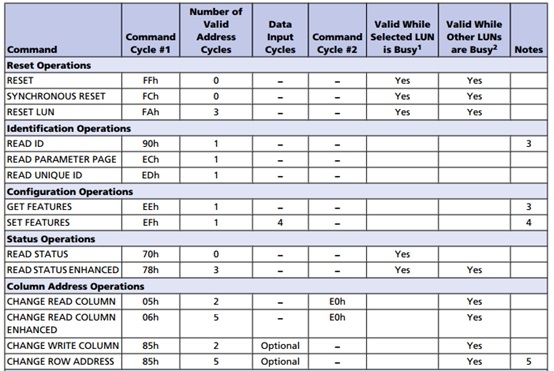

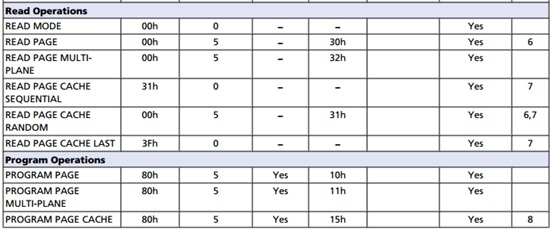

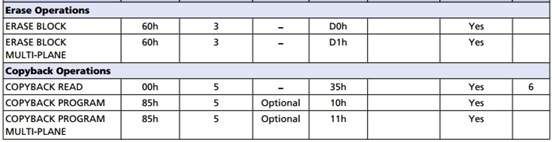

NAND Flash的操作通过一系列的命令来完成。镁光芯片的操作命令定义如下:

命令一共分成9大类,包括复位操作、识别操作、配置操作、状态操作、地址操作、读操作、写(编程)操作、擦除操作以及写回操作。在NAND Flash控制器的软件中需要将这些最底层的命令封装成NAND Flash操作库。

读命令

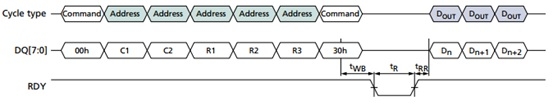

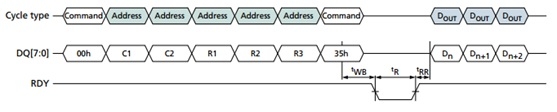

对于读操作,NAND Flash提供了多种模式。普通的页读操作效率比较低,在发起页读取的时候需要输入具体的命令和地址信息,然后再输出数据,具体的操作时序如下图所示:

输入命令和地址信息之后,RDY信号变低,NAND Flash需要等待一段时间之后才能输出数据,当数据准备完毕,可以输出时,RDY信号变高。NAND Flash在这个过程中需要不断检测RDY信号,当该信号由低变高之后,可以通过同步或者异步的方式输出数据。

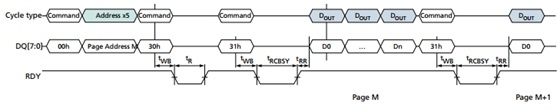

在NAND Flash的内部,有一个data cache寄存器,通过该寄存器可以将数据读取操作分成两个阶段:一个是从page cache寄存器向NAND Flash控制器传输数据;另一个是从NAND Flash中向data寄存器加载数据。这两个操作可以进行流水并发,命令0x31就是用来实现这个流水并发操作的。为了提高数据输出的效率,在普通页读取的基础上,通过0x31命令可以在数据从page cache输出的同时从NAND Flash中向data cache加载新的数据。这种并发模式分成两类:一类为顺序读,另一类为随机读,在操作时序上存在差别。下图为并发顺序读的操作时序:

在指定地址的数据从page cache中输出的同时,NAND Flash会将下一页数据加载到data寄存器中,这样当NAND Flash控制器读取完指定page中的数据之后,下一页数据也已经被加载成功了。通过这种流水机制,提升读性能。

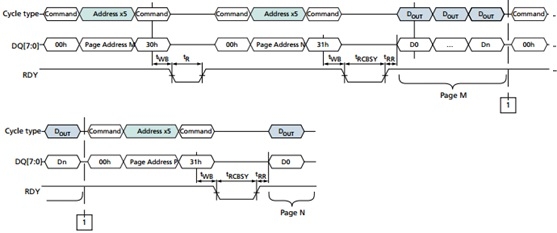

除了可以流水并发顺序page页之外,也可以将随机的page页进行并发流水读取,如下图所示:

在页读取命令发送完毕之后,当该数据被加载到page cache之后,RDY信号由低置高。紧接着输入另一个页地址,以及流水加载命令0x31。在page cache中数据往外输出的同时,NAND Flash中的数据并发输出到data寄存器中。通过这种方式可以流水并发读取两个离散page页中的数据。

对于并发读取两个plane中的数据,NAND Flash也提供了0x00-0x32控制命令,通过该命令可以实现多个plane数据的并发加载,从NAND Flash中加载到各自对应的page cache中。

写(编程)命令

普通的写命令允许NAND Flash控制器将数据写入NAND Flash中的page cache寄存器,并且将数据从page cache寄存器中写入到NAND Flash介质中。一个普通的页编程时序如下图所示:

该过程可以分成三大步骤:第一步输入控制命令、操作地址信息;第二步输入需要写入的数据至page cache;第三步启动编程,将page cache寄存器中的数据写入NAND Flash介质。

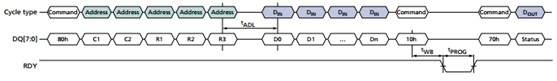

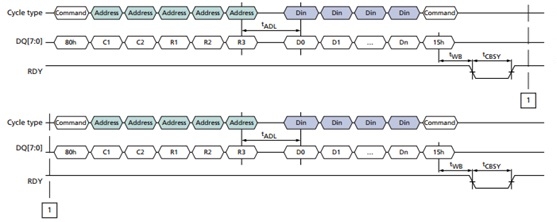

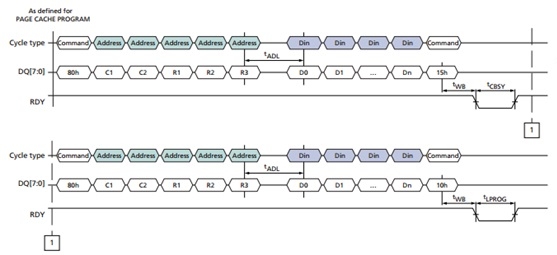

如果每次写入操作都经历上述过程,那么写延迟将会变得很长。为了提高页写入性能,NAND Flash提供了流水并发模式,该模式充分利用了data寄存器。采用的命令是0x80-0x15,时序如下图所示:

在该模式下,在地址和命令的控制下,数据被首先写入到page cache寄存器中。当0x15控制命令发送完毕之后,page cache寄存器中的数据会被拷贝到data寄存器中。拷贝进行时RDY信号置低,当拷贝完成之后,RDY信号变高电平。NAND Flash控制器在这种情况下可以输入下一个页的数据,在下一个页数据输入的过程中,NAND Flash会并发将data寄存器中的数据写入指定的介质中去。从而达到控制器输入和具体的编程操作之间的流水并发,提高了page页写操作的吞吐量。

需要结束流水编程时,在最后一页数据写入之后,写入0x10命令即可。具体的时序操作如下图所示:

对于并发编程两个Plane中的数据页,NAND Flash提供了0x80-0x11命令。通过该命令可以直接将数据写入到多个Plane中的page cache寄存器中,从而实现多个Plane中的数据页并发写入。

擦除操作命令

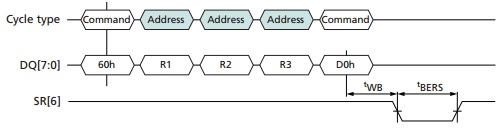

擦除操作是一个非常费时的操作,对于NAND Flash而言,一个最小的擦除单元是block块。当需要对一个块进行擦除操作时,需要输入块的地址以及对应的控制命令,具体时序如下图所示:

在擦除的过程中,RDY信号会置低,此时该DIE将无法进行正常的读写操作。所以,虽然不同的Plane之间拥有不同的寄存器组,但是由于物理信号线是共用的,所以,一旦一个Plane中的block进入了擦除状态,那么整个DIE的读写操作将会受到影响。

COPYBACK命令

在wear-leveling操作,或者garbage collecting的时候,通常需要将一个page页中的数据拷贝到另一个page页,这就用到了COPYBACK的功能。该命令可以将一个page页中的数据加载到寄存器中,然后直接写入到指定的另一个page页中。

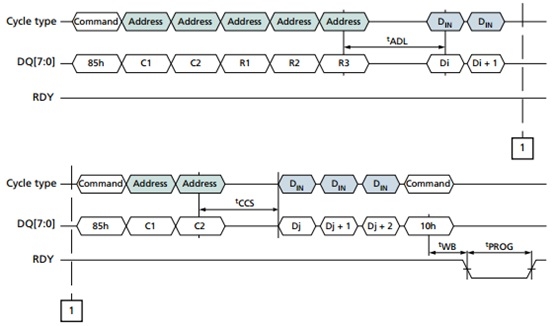

在实际操作过程中,考虑到NAND Flash中的数据可能已经遭到破坏,NAND Flash通常建议控制器在数据回拷的过程中,对迁移的数据进行校验。为此NAND Flash提供了COPYBACK READ的控制操作过程,如下图所示:

COPYBACK READ命令执行完毕之后,数据会输入到NANDFlash控制器,控制器中的ECC×××对数据进行校验,如果数据发生错误,那么在COPYBACK WRITE的过程中可以将正确的数据写入到NAND Flash中,在这个过程中可以使用CHANGE WRITE COLUME实现对page页的随机写操作。该时序如下图所示:

当更新的数据被写入到Page cache寄存器之后,启动页编程,完成COPYBACK操作。

(吴忠杰,存储之道)

转载于:https://blog.51cto.com/alanwu/1668609

镁光256Gb NAND Flash芯片介绍相关推荐

- 低功耗SD\SPI NAND Flash芯片

目前市面上很多SD/ SPI 的NAND FLASH芯片普遍面临功耗过高的情况,尤其是应用在穿戴类产品,包括手环,手表,耳机,心电贴等产品的时候,由于用户对于穿戴产品的待机时长要求很高,从而导致所有穿 ...

- STM32F103ZE单片机FSMC接口读取NAND Flash芯片K9F1G08U0E的数据时出现数据丢失的解决办法

[问题] STM32单片机使用FSMC读取K9F1G08U0E NAND Flash时,出现部分字节丢失的情况.例如:Flash存储器中存储有连续的0xff字节,则在进行连续读(Page Read)操 ...

- 《STM32从零开始学习历程》——SPI物理层及FLASH芯片介绍

<STM32从零开始学习历程>@EnzoReventon SPI物理层及FLASH芯片介绍 相关链接: SPI协议层 SPI特性及架构 SPI固件库 参考资料: [野火EmbedFire] ...

- Nand flash相关概念介绍

1. SDR/DDR SDR(Single Data Rate): 读写数据使用上升沿或下降沿. DDR(Double Data Rate):写数据时通过MCU来控制DQS信号跳变沿来触发(即上升沿和 ...

- Nor flash、Nand flash 简要介绍

一.NOR flash NOR flash 分为CFI nor flash 和 SPI nor flash. CFI nor flash使用的外部接口是CFI(common flash interfa ...

- 【FLASH存储器系列十二】Nand Flash芯片使用指导之二

目录 1.1 芯片指令集 1.2 READ PAGE(00h–30h) 1.3 READ PAGE CACHE SEQUENTIAL (31h) 1.4 READ PAGE CACHE RANDOM ...

- NAND FLASH芯片R/B引脚上拉电阻的作用和阻值选择

NAND用R/B输出作为一种硬件方法标示页操作.擦除和随机读等操作的完成,平时R/B为高电平状态,但当NAND进行编程.随机读或擦除操作时变为低电平状态,操作完成后又变为高电平状态.R/B引脚 ...

- 【FLASH存储器系列十一】Nand Flash芯片使用指导之一

- 全面理解SSD和NAND Flash

Flash Memory又叫做闪存,是一种非易失性存储器.非易失性是指断电之后数据不会丢失,这里就涉及到断电保护(后面详细讲解). 总体思路 1.NAND Flash的用途. 2.NAND Flash ...

最新文章

- 2021年大数据Spark(三十五):SparkStreaming数据抽象 DStream

- SAP RETAIL Plant Group里的特性

- python打印出指定目录下的所有文件夹和文件名(递归实现)

- where is page layout xml template being initialized - hard code in ctr

- 数字图像处理——2D降噪

- Myesclipe+SSH+jsp+mysql+tomcate实现一个简单的CRM客户关系管理系统

- Spring Boot中使用Actuator的/info端点输出Git版本信息

- cdh中hdfs非ha环境迁移Namenode与secondaryNamenode,从uc机器到阿里;

- Linux笔记-为操作系统配ntp服务地址(适用达梦操作系统)

- mysql分片库分页查询_Mysql分库分表

- hutool 取前12个月_Excel – 创建 12 个月的工资表模板,我只要 20 秒

- Linux中的mate程序的进程,终端下以后台模式运行Linux程序的过程详解

- mysql之主从复制

- linux7.3系统如何修改系统时间,两招修改Centos7 系统时区!

- ESP32 学习笔记(二十九) ESP32 低功耗模式

- 【老九学堂】【Java】初级编码规范

- 运行java程序需要的工具软件的目录,运行Java程序需要的工具软件所在的目录是A.JDK的bin目录B.JDK的demo目录C.JDK的lib目录D.JDKR的j...

- 《后来》可爱MM演唱 视频

- 不一样的解决Non-static method 'xxx' cannot be referenced from a static context

- 什么邮箱发送邮件不进垃圾箱,邮件进垃圾箱了是什么原因怎么办?