《Windows CE嵌入式开发入门——基于Xscale架构》第4章 外设控制器

PXA255具有丰富的外设接口,如LCD控制器、I2S控制器和UART控制器等,可以实现丰富的人机接口以及数据输入输出。

4.1 LCD控制器

4.1.1 概述

1.色彩描述板

2.刷新模式

TFT显示屏采用的是主动(Active)刷新模式,不采用瞬时抖动的方法。

不同的显示模式最终使用的LCD数据输出引脚数也是不同的,而且双向刷新模式所使用的数据引脚数一定是对应单向刷新模式的一倍,这是因为双向刷新模式是同时刷新屏幕的上半部分和下半部分。

3.控制时钟

4.特性

Ø 在被动单色模式中最多可以显示256级灰度(8位压缩编码);

Ø 在主动彩色模式中最多可以显示65536种色彩(16位瞬时抖动);

Ø 在主动彩色模式中最多可以显示65536种色彩(16位不采用瞬时抖动);

n 最大分辨率可达1024×1024像素,建议最大分辨率640×480像素;

n 支持外部RAM彩色色彩描述板,256入口16位宽数据(能够在每帧开始时自动加载);

n 可编程的像素时钟,频率范围195kHz~83MHz(100MHz/512至166MHz/2);

n 具有双DMA通道(一个通道用来传输色彩描述板和单向刷新的数据,另一个通道用来在双向刷新模式中传输下半屏幕刷新的数据)。

4.1.2 LCD控制器寄存器

1.控制寄存器

n 设置帧时钟、行时钟、像素时钟和AC Bias引脚信号的频率;

n 设置在屏幕显示数据(行数据、帧数据)前后插入的空数据量(协调屏幕尺寸最小数据传输量);

LCCR0的使能位(ENB)被置1时,LCD控制器启动。在控制器启动后其他的控制位就不能做任何的更改了,这点在编程时要特别注意,并且LCD控制器的停止也是依靠控制寄存器来控制的。

OUM=0时,下溢中断被启用,这时当LCSR中的OU状态位被置1时,一个下溢中断请求产生,中断控制器响应,完成相应的出错处理。OUM=1时,下溢中断被屏蔽。

QDM=0时快速停止中断被启用,这时当LCSR中的QD状态位被置1时,一个LCD快速关闭中断请求产生,中断控制器响应请求。QDM=1时被屏蔽。快速关闭一般用于休眠模式。

DIS=1时,LCD控制器在读取完当前帧的数据后会停止从缓存中读取新的帧数据,在当前帧显示完成后,关闭LCD控制器。

这一位是用来控制显示模式,主动还是被动显示模式。PAS=0时,被动模式被选中。PAS=1时,主动模式被选中。

SDS=0时表示单向刷新,SDS=1时表示双向刷新。在主动模式下SDS一定为0。

CMS=0时,选中了彩色模式,相应的色彩描述板的的色彩数据是16位宽。CMS=1时,选中了单色模式,相应的色彩描述板的色彩数据是8位宽(最多256级灰度)。

ENB=0时,所有的LCD引脚都被作为通用IO口使用;ENB=1时,LCD控制器启用。

这个寄存器中的4个域的值是用来控制LCD行显示相关时钟信号的时序,它们分别是对应计数器的默认计数值。

表示在开始显示一行像素前所需要等待的空像素时钟节拍数。BLW可以产生的1~256个像素时钟的等待周期,对应BLW值0~255。

和BLW类似,是在一行像素显示结束后需要等待的空像素时钟节拍数。

和LCCR1类似,这个寄存器中的4个域的值是用来控制LCD上帧显示相关时钟信号的时序的。

只在主动显示模式下使用,表示在开始显示新的一帧前所需要等待的空行时钟节拍数。BLW可以产生的0~255个行时钟的等待周期,BLW=0时不等待。

只在主动显示模式下使用,和BFW类似,是在一帧像素显示结束后需要等待的空行时钟节拍数。

LPP可以描述0~1023范围的值,它指定了屏幕中行的数量(1~1024行)。

PCP=0时,在L_PCLK上升沿有效,采样LCD数据引脚的数据。PCP=1时,在L_PCLK下降沿有效,采样LCDLCD数据引脚的数据。

HSP=0时,L_LCLK高电平有效,HSP=1时,L_LCLK低电平有效。在被动模式下水平同步信号就是行时钟信号。

VSP=0时,L_FCLK高电平有效,VSP=1时,L_FCLK低电平有效。

2.状态寄存器(LCSR)

当DMA控制器从存储器中取得一帧的显示数据,并且数据中的帧描述符中包含表示帧结束的标示位,那么EOF=1,如果LCCR0中的EFM屏蔽位没有被设置,那么将产生一个EOF中断请求。

当QD=1,QDM=0时,会产生一个快速关闭的中断,这个中断会强制停止LCD控制器,并且马上停止LCD的引脚的驱动。快速关闭可用于LCD休眠模式。

如果输出FIFO为空,LCD的数据引脚还继续尝试从FIFO中获取显示数据时,OU=1。若OUM=0时,这将产生一个输出FIFO下溢中断。

如果上屏幕的输入FIFO为空,LCD控制器的像素解码器还继续尝试从FIFO中获取压缩编码的数据时,IUU=1。若IUM=0时,这将产生一个输入FIFO下溢中断。

当DMA传输控制器发生了一个系统总线的错误时,BER=1。例如,当DMA控制器试图访问保留的或不存在的存储空间。错误发生后,DMA控制器会停止工作,直到有效的地址空间被加载到FDADRx寄存器。

当DMA控制器获取到新的帧描述符,并且它包含表示帧开始的标示位,那么SOF=1,如果LCCR0中的SFM屏蔽位没有被设置,那么将产生一个SOF中断请求。

4.1.3 LCD控制器的操作

1.帧缓存与总线带宽

FrameBufferSize=(BitPerPixel´Lines´(Pixels + n))/8 (单位是byte)

在双向刷新模式中,两个DMA管道的帧缓冲大小是一样的,所以在计算这个模式下一个管道中的帧缓冲时,Lines是屏幕大小的一半。

为了满足显示数据的传输,LCD控制器的数据传输总线带宽可以用以下公式计算得到:

BusBandwidth=(FrameBufferSize+PaletteSize)´RefreshRate

BusBandwidth=(FrameBufferSize*2+PaletteSize)´RefreshRate

其中PaletteSize是色彩描述板的大小,单色色彩描述板的大小是256´8bit=256byte,彩色色彩描述板是256´16=512byte。RefreshRate是屏幕的刷新率。

在双向模式中,负责上半屏幕的DMA管道负责传输Palette和上半屏幕的显示数据,而负责下半屏幕的DMA管道只下半屏幕的显示数据,所以双向模式的公式中PaleteSize没有乘以2。

2.被动模式的时序

|

ENB – LCD使能信号 |

HSP – 水平同步极性设置 |

|

0 – LCD禁止 |

0 – 行时钟高有效,低无效 |

|

1 – LCD使能 |

1 – 行时钟低有效,高无效 |

|

VSP – 垂直同步极性设置 |

PCP – 像素时钟极性设置 |

|

0 – 帧时钟高有效,低无效 |

0 – 在时钟的上升沿采样像素数据 |

|

1 – 帧时钟低有效,高无效 |

1 – 在时钟的下降沿采样像素数据 |

|

当PCP=0时,L_PCLK的波形是反向的,但时序是相同的。 |

|

|

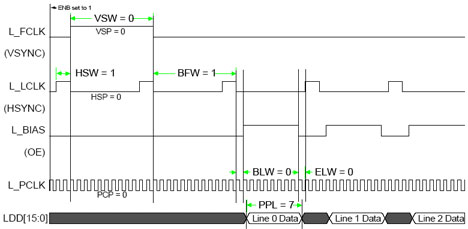

VSW = 垂直同步信号脉冲宽度 – 1 |

|

|

HSW = 水平同步信号(行时钟)脉冲宽度 – 1 |

|

|

BLW = 开始行像素时钟等待个数 – 1 |

|

|

ELW = 结束行像素时钟等待个数 – 1 |

|

图4-1 被动模式帧启动时序

|

ENB – LCD使能信号 |

HSP – 水平同步极性设置 |

|

0 – LCD禁止 |

0 – 行时钟高有效,低无效 |

|

1 – LCD使能 |

1 – 行时钟低有效,高无效 |

|

VSP – 垂直同步极性设置 |

PCP – 像素时钟极性设置 |

|

0 – 帧时钟高有效,低无效 |

0 – 在时钟的上升沿采样像素数据 |

|

1 – 帧时钟低有效,高无效 |

1 – 在时钟的下降沿采样像素数据 |

|

当PCP=0时,L_PCLK的波形是反向的,但时序是相同的。 |

|

|

VSW = 垂直同步信号脉冲宽度 – 1 |

|

|

HSW = 水平同步信号(行时钟)脉冲宽度 – 1 |

|

|

BLW = 开始行像素时钟等待个数 – 1 |

|

|

ELW = 结束行像素时钟等待个数 – 1 |

|

|

PPL = 每行像素 – 1 |

|

|

LPP = 每屏幕行数 – 1 |

|

图4-2 被动模式帧结束时序

|

PCP – 像素时钟极性设置 |

|

0 – 在时钟的上升沿采样像素数据 |

|

1 – 在时钟的下降沿采样像素数据 |

|

当PCP=0时,L_PCLK的波形是反向的,但时序是相同的。 |

图4-3 被动模式像素时钟和数据引脚时序

3.主动模式的时序

主动模式的时序如图4-4与图4-5所示。

4.LCD启动

将对应的通用I/O引脚配置给LCD控制器,设置了正确的色彩描述板、帧描述符的内存地址和LCCR0以外的一些必要寄存器的设置后,置位LCCR0的ENB控制位后LCD控制器就会启动了。

|

ENB – LCD使能信号 |

HSP – 水平同步极性设置 |

|

0 – LCD禁止 |

0 – 行时钟高有效,低无效 |

|

1 – LCD使能 |

1 – 行时钟低有效,高无效 |

|

VSP – 垂直同步极性设置 |

PCP – 像素时钟极性设置 |

|

0 – 帧时钟高有效,低无效 |

0 – 在时钟的上升沿采样像素数据 |

|

1 – 帧时钟低有效,高无效 |

1 – 在时钟的下降沿采样像素数据 |

|

当PCP=0时,L_PCLK的波形是反向的,但时序是相同的。 |

|

|

VSW = 垂直同步信号脉冲宽度 – 1 |

|

|

HSW = 水平同步信号(行时钟)脉冲宽度 – 1 |

|

|

BFW = 开始帧水平同步时钟等待个数 |

|

|

BLW = 开始行像素时钟等待个数 – 1 |

|

|

ELW = 结束行像素时钟等待个数 – 1 |

|

|

PPL = 每行像素 – 1 |

|

图4-4 主动模式的时序

|

PCP – 像素时钟极性设置 |

|

0 – 在时钟的上升沿采样像素数据 |

|

1 – 在时钟的下降沿采样像素数据 |

|

当PCP=0时,L_PCLK的波形是反向的,但时序是相同的。 |

图4-5 主动模式像数时钟和数据引脚时序

伪代码如下:

#define LCCR0_ADDRESS 0x44000000 // LCCR0的地址

#define LCCR0 ( * ( (volatile unsigned int * ) LCCR0_ADDRESS ) )

#define LCD_ENB 0x00000001 // ENB在LCCR0中的位置

LCCR0 = LCCR0 | LCD_ENB; // 置位ENB

5.LCD停止

(1)正常停止

一般建议使用这个方式停止LCD控制器。这个操作是由设置LCCR0的DIS控制位来完成的。并且在LCD控制器加载了最后要显示的帧数据后,LCSR的LDD状态位会被硬件自动置位,同时LCCR0中的ENB位也会被硬件清零。

伪代码如下:

#define LCCR0_ADDRESS 0x44000000 // LCCR0的地址

#define LCCR0 ( * ( (volatile unsigned int * ) LCCR0_ADDRESS ) )

#define LCSR_ADDRESS 0x44000038 //LCSR的地址

#define LCSR ( * ( (volatile unsigned int * ) LCSR_ADDRESS ) )

#define LCD_DIS 0x00000400 //DIS在LCCR0中的位置

#define LCD_LDD 0x00000001 //LDD在LCSR中的位置

LCCR0 = LCCR0 | LCD_DIS; //LCCR0中的LCD_DIS位置位

while(!(LCSR & LCD_LDD)); //等待硬件置位LDD

LCSR = LCSR & (~LCD_LDD); //软件清除LCD_LDD位,以便下次使用

(2)快速停止

直接清除LCCR0的ENB控制位可以实现快速停止的操作。清除了ENB位后LCSR的QD状态位会被置位,产生一个中断,中断响应后LCD控制器会马上停止加载了一切的帧数据,停止LCD控制器对LCD引脚的驱动。在电池电量不足时,CPU为了保存重要的数据,快速停止模式被采用。

伪代码如下:

#define LCCR0_ADDRESS 0x44000000 // LCCR0的地址

#define LCCR0 ( * ( (volatile unsigned int * ) LCCR0_ADDRESS ) )

#define LCD_ENB 0x00000001 // ENB在LCCR0中的位置

LCCR0 = LCCR0 & (~LCD_ENB); //清除ENB位

4.2 I2S控制器

4.2.1 概要

n 码率时钟,I2SC会将可选的系统时钟信号也发送到外部解码器中。

可以通过两种方式将数字化的音频信号通过串行通道进行传输:普通的I2S和MSB- Justified-I2S。它们都能够在不同的时钟频率下进行工作。

4.2.2 信号描述

SYSCLK是I2S单元中所有其他时钟信号的基础。通过使用可编程分频器分频PLL,SYSCLK可以产生频率从2MHz~12.2MHz的时钟频率。它的频率应当始终为音频采样率的256倍。

|

名 字 |

方 向 |

描 述 |

|

GP32/SYSCLK |

输出 |

SYSCLK = BITCLK´4,仅用于解码器 |

|

GP28/BITCLK |

输入/输出 |

BITCLK = SYNC´64 |

|

GP31/SYNC |

输出 |

左右声道标记信号 |

|

GP30/SDATA_OUT |

输出 |

到CODEC的串行音频数据 |

|

GP29/SDATA_IN |

输入 |

来自于CODEC的串行音频数据 |

BITCLK可以被配置成输入或者输出模式。编程可以按照以下步骤。

① 设置SYSUNIT的GPIO方向寄存器(GPDR)。

② 设置SYSUNIT的GPIO候选功能选择寄存器(GAFR)。

③ 设置I2SC的串行音频控制寄存器中的BCKD位。

如果BITCLK被配置成输出方向,SYSCLK也必须被配置成相同的方向。如果BITCLK是由解码器提供的,那么GPIO引脚GP32可以选用候选功能。

n 设置SYSUNIT的GPIO方向寄存器(GPDR)。

n 设置SYSUNIT的GPIO候选功能选择寄存器(GAFR)。

要将SYNC和SDATA_OUT配置成输出方向,按照以下步骤操作:

n 设置SYSUNIT的GPIO方向寄存器(GPDR)。

n 设置SYSUNIT的GPIO候选功能选择寄存器(GAFR)。

4.2.3 控制操作

处理器和DMA控制器都可以操作I2S控制器(I2SC)。处理器可以通过I/O指令来控制I2SC。并且可以得到以下类型的数据。

n I2SC寄存器数据:所有寄存器都是32位宽,并且按字对齐。

n I2SC FIFO数据:向I2SC串行音频数据寄存器(SADR)写入值,会占用发送FIFO的一个入口。而读一次(SADR)会引起FIFO的刷新,并且腾出一个空闲的接收FIFO入口。

n I2S解码器数据:解码器寄存器可以通过L3总线进行访问。L3总线操作应当由软件控制的3个GPIO引脚进行模拟。

1.初始化

② 选择运行模式、普通I2S或者MSB-Justified模式。这可以通过向SACR1寄存器的第0个位编程实现。

④ 以下的操作可以同时在I2SC串行音频控制器全局控制寄存器上执行(SACR0):

n 通过填充SACR0寄存器的TFTH和RFTH位,确定发送/接收的水位值。

2.使能和关闭声道的回放

当I2SC被使能后,音频的传送就被自动使能。可以通过设置SACR1中的DRPL位,来关闭音频的传送和回放功能。

3.使能和关闭录音功能

当I2SC被使能后,录音功能就被自动使能。可以通过设置SACR1中的DREC位,来关闭录音功能。

4.Trailing Bytes

当解码器完成有效数据的传送后,I2SC会将数据0填充到录音数据中,直到关闭录音功能。如果总的接收到的数据数量小于接收水位值,剩下的就会用0填充。当达到水位值后,会触发一个DMA请求。

4.2.4 串行数据时钟和采样频率

|

Audio Clock Divider Register(31:0) |

SYSCLK = (147.6MHz / SADIV) |

BITCLK = SYSCLK / 4 |

SYNC or Sampling frequency = BITCLK / 64 |

|

0x0000_000C |

12.288MHz |

3.072MHz |

48.000kHz(closest std = 48kHz) |

|

0x0000_000D |

11.343MHz |

2.836MHz |

44.308kHz(closest std = 44.1kHz) |

|

0x0000_001A |

5.671MHz |

1.418MHz |

22.154kHz(closest std = 22.05kHz) |

|

0x0000_0024 |

4.096MHz |

1.024MHz |

16.000kHz(closest std = 16.00kHz) |

|

0x0000_0034 |

2.836MHz |

708.92kHz |

11.077kHz(closest std = 11.025kHz) |

|

0x0000_0048 |

2.048MHz |

512.00kHz |

8.000kHz(closest std = 8.00kHz) |

4.2.5 数据格式

1.FIFO和内存数据格式

2.I2S和MSB-Justified Serial Audio数据格式

I2S和MSB-Justified是两种类似的串行音频数据传输协议。图4-7和图4-8显示了I2S和MSB-justified的数据格式。

4.2.6 寄存器列表

所有的I2S寄存器都是32位宽的,因此地址的递增是以0x0000_0004为增量的,所有的寄存器简要描述见表4-3。

|

Address |

寄存器名字 |

描 述 |

|

0x4040_0000 |

SACR0 |

全局控制寄存器 |

|

0x4040_0004 |

SACR1 |

串行音频数据控制寄存器 |

|

0x4040_0008 |

– |

保留 |

|

0x4040_000C |

SASR0 |

串行音频数据接口和FIFO状态寄存器 |

|

0x4040_0014 |

SAIMR |

串行音频中断掩码寄存器 |

|

0x4040_0018 |

SAICR |

串行音频中断清除寄存器 |

|

0x4040_001C至0x4040_005C |

– |

保留 |

|

0x4040_0060 |

SADIV |

音频时钟除数寄存器 |

|

0x4040_0064至0x4040_007C |

– |

保留 |

|

0x4040_0080 |

SADR |

串行音频数据寄存器(接收和发送FIFO访问寄存器) |

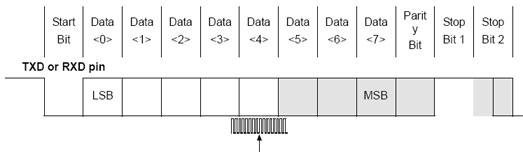

4.3 UART控制器

n 能动态指定串口通信中的标志位,如增加启始位、奇偶校验位等;

n 支持可编程的波特率产生器,将时钟分频至1到(216–1)分之一,产生内部时钟;

n 对于BTUART和HWUART波特率可以达到921kbit/s,其他接口可以达到230kbit/s;

4.3.1 接口信号描述

表4-4描述了在串口通信中需要使用到的信号。和这些信号相对应的引脚被直接连接到PXA255的GPIO上。

|

信 号 |

类 型 |

功 能 |

|

RXD |

输入 |

串口输入信号:输入的数据将被储存到接受移位寄存器。在红外模式下,这个信号直接和红外的输入器相连接 |

|

TXD |

输出 |

串口输出信号。在系统复位后,TXD被置成1 |

4.3.2 UART操作方式

每个UART有两个FIFO队列:输出队列和输入队列。输出队列有64个8位的空间;而输入队列有64字节的空间,每个单元由11位组成,多余的3位用来存放错误信息。

4.3.3 启动UART

4.3.4 内部寄存器描述

每个UART都有13个寄存器,其中12个为UART操作控制寄存器,另外一个寄存器是留给慢速红外传输模式的。所有的寄存器都为32位宽,但是只有低8位数据有效。

|

UART寄存器地址(基地址+偏移) |

DLAB位值 |

被访问的寄存器 |

|

基地址 |

0 |

接收缓冲寄存器(只读) |

|

基地址 |

0 |

发送缓冲寄存器(只写) |

|

基地址+0x04 |

0 |

中断使能寄存器(读/写) |

|

基地址+0x08 |

X |

中断识别寄存器(只读) |

|

基地址+0x08 |

X |

FIFO控制寄存器(只写) |

|

基地址+0x0C |

X |

电话线控制寄存器(读/写) |

|

基地址+0x10 |

X |

调制解调器控制寄存器(读/写) |

|

基地址+0x14 |

X |

电话线状态寄存器(只读) |

|

基地址+0x18 |

X |

调制解调器状态寄存器(只读) |

|

基地址+0x1C |

X |

暂时寄存器(读/写) |

|

基地址+0x20 |

X |

红外选择寄存器(读/写) |

|

基地址 |

1 |

分频寄存器低字节(读/写) |

|

基地址+0x04 |

1 |

分频寄存器高字节(读/写) |

1.接收数据寄存器Receive Buffer Register(RBR)(见表4-6)

表4-6描述了接收数据寄存器(RBR),在非FIFO模式下RBR寄存器保存了从接收移位寄存器(Receive Shift Register)接收到的数据,由于接收移位寄存器的宽度为8,如果RBR的宽度被设置成小于8位,那么只有右边的数据会被保留。MSB将被用0填充。对这个寄存器的读操作将使寄存器被清空,并且Line Status Register(LSR)也将被置0。

在FIFO模式下,RBR将取接收队列的头一个元素。

表4-6 接收数据寄存器(RBR)

|

位 号 |

名 字 |

描 述 |

|

31:8 |

- |

保留 |

|

7:0 |

RBR[7:0] |

接收的字节(最低位先入) |

2.发送数据寄存器Transmit Holding Register(THR)(如表4-7)

表4-7描述了发送数据寄存器(THR),在非FIFO模式下THR中的数据将被传送到发送移位寄存器(TSR)中。当TSR中的数据被发送后,THR中的数据将被传送到TSR中,并且LSR[TDRQ]被设置成1。

在FIFO模式下,向THR中写入数据将把数据存放到发送队列头部,此前的数据将被装载到TSR中。

表4-7 发送数据寄存器(THR)

|

位 号 |

名 字 |

描 述 |

|

31:8 |

- |

保留 |

|

7:0 |

THR[7:0] |

发送的字节(最低位先出) |

3.分频寄存器Divisor Latch Registers(DLL and DLH)

每个UART接口都能编程控制波特率,它以14.7456MHz输入时钟为基础进行分频。分频值可以从1到(216–1)。对于FFUART和STUART分频值为4到(216–1)。

波特率产生器产生的频率,是波特率的16倍。DLL和DLH两个8位寄存器一共存储了16位的分频值。如果这两个寄存器都为0,则分频器停止工作。它们的描述如表4-8和表4-9所示。

表4-8 分频寄存器(DLL)

|

位 号 |

名 字 |

描 述 |

|

31:8 |

- |

保留 |

|

7:0 |

DLL[7:0] |

用于产生波特率的分频寄存器低8位 |

表4-9 分频寄存器(DLH)

|

位 号 |

名 字 |

描 述 |

|

31:8 |

- |

保留 |

|

7:0 |

DLH[7:0] |

用于产生波特率的分频寄存器高8位 |

4.FIFO控制寄存器(FCR)

FCR是一个只写寄存器如表4-10所示。FCR决定了串口是否一FIFO队列的模式运行。如表4-10所示。

表4‑10 FIFO控制寄存器(FCR)

|

位 号 |

名 字 |

描 述 |

||||

|

31:8 |

- |

保留 |

||||

|

7:6 |

ITL |

中断触发级别:当接收器FIFO中的字节数目达到了ITL中的数目,并且通过IER寄存器允许触发中断,一个中断信号将被产生,同时会产生一个接收的DMA请求 |

||||

|

5:3 |

- |

保留 |

||||

续表

|

位 号 |

名 字 |

描 述 |

||||

|

2 |

RESETTF |

发送器FIFO清零:当RESETTF被设置成1,在发送器FIFO中的数据都将被清除。如果IER中的TIE位被置位,LSR中的TDRQ位将被置位,IIR显示了发送器请求数据的中断。发送器移位寄存器不会被清除,UART会完成当前的发送 |

||||

|

1 |

RESETRF |

接收器FIFO清零:当RESETRF被设置成1,在接收器FIFO中的数据都将被清除。LSR中的DR位被清零。FIFO中的所有错误位和FIFOE位都将被清除。LSR中已经设置的错误位,如OE,PE,FE或者BI都仍然保留。接收移位寄存器不会被清零。如果IIR已经被设置成接收数据可用信号,此信号就会被清除 |

||||

|

0 |

TRFIFOE |

发送器和接收器FIFO使能:TRFIFOE使能/禁止发送器和接收器的FIFO。当TRFIFOE=1,两个FIFO都会被使能(进入FIFO模式)。当TRFIFOE=0,两个FIFO都会被禁止(进入非FIFO模式)。将此位写0将会清除两个FIFO中的所有的数据。当从FIFO模式转变成非FIFO模式或者相反,FIFO中的数据会被自动清除。当此寄存器中其他位被写入时,此位必须为1,或者其他位没有被编程 |

||||

5.STUART寄存器总结

将STUART寄存器信息总结如表4-11所示。

表4-11 STUART寄存器总结

|

寄存器地址 |

DLAB位值 |

名 字 |

描 述 |

|

0x4070_0000 |

0 |

STRBR |

接收缓冲寄存器(只读) |

|

0x4070_0000 |

0 |

STTHR |

发送保持寄存器(只写) |

|

0x4070_0004 |

0 |

STIER |

IER(读/写) |

|

0x4070_0008 |

X |

STIIR |

中断ID寄存器(只读) |

|

0x4070_0008 |

X |

STFCR |

FCR(只写) |

|

0x4070_000C |

X |

STLCR |

LCR(读/写) |

|

0x4070_0010 |

X |

STMCR |

MCR(读/写) |

|

0x4070_0014 |

X |

STLSR |

LSR(只读) |

|

0x4070_0018 |

X |

STMSR |

保留(无Modem控制脚) |

|

0x4070_001C |

X |

STSPR |

暂时寄存器 |

续表

|

寄存器地址 |

DLAB位值 |

名 字 |

描 述 |

|

0x4070_0020 |

X |

STISR |

红外选择寄存器(读/写) |

|

0x4070_0000 |

1 |

STDLL |

分频器低8位寄存器(读/写) |

|

0x4070_0004 |

1 |

STDLH |

分频器高8位寄存器(读/写) |

4.4 快速红外端口(FICP)控制器

n 4相位脉冲调制Fourposition pulse modulation(4PPM);

4.4.1 信号描述

FICP使用了IRRXD和IRTXD信号。表4-12描述了这两个信号的功能。大多数IrDA传输器都有自己的使能和传输速率配置GPIO引脚。

|

信 号 |

输入/输出 |

描 述 |

|

IRRXD |

输入 |

FICP的接收数据引脚 |

|

IRTXD |

输出 |

FICP的发送数据引脚 |

4.4.2 FICP操作

收发数据寄存器中的数据将按照4PPM IrDA标准进行调制,然后转换成串行或者并行数据格式。

1.4PPM调制

4相位脉冲(Four-position pulse modulation,4PPM)用在4.0Mbps高速率数据传输场合。数据编码和传输过程如下:

图4-10 4PPM Modulation Encodings

图4-11说明了对数据0b10110001进行编码并且传送的实例。编码时一次对一个字节编

2.帧格式

3.地址域

4.控制域

控制域是一个可选的8位域,它由软件定义。FICP并没有为控制域提供硬件的解码支持,它将地址域和CRC域之间的所有位都视为数据。

5.数据域

数据域的长度可以从0~2045字节,具体有软件指定。当接收到的数据长度不是8位的倍数时,会产生abort信号。

6.校验域

需要注意的是,与地址、控制、数据域相反,CRC域是以最高位Nibble首先发送的。CRC的计算公式如下:

CRC(X)=(X32+X26+X23+X22+X16+X12+X11+X10+X8+X7+X5+X4+X2+X+1)

7.接收操作

IrDA标准规定了所有的数据帧不得超过2047字节(包括地址和控制字节),而在PXA255中并没有限制数据帧的大小。数据帧的大小必须有软件确保。

如果在数据域中发现无效chip,如0011、1010、1110等,数据帧的接收就会停止。临时FIFO中的旧数据将被转移到接收FIFO中,而没有被转移的数据将被丢弃。

8.发送操作

当发送FIFO中的空闲入口多于32个时,将产生一个DMA服务的中断请求。软件可以决定当数据的填充速度不能满足发送要求时,该帧是作为正常终止还是异常终止。

当软件将其视为正常终止的情况下,发送逻辑单元会正常计算CRC校验码,然后发送数据。然后进入下一帧的处理。

9.发送和接受FIFO

发送FIFO有128个存储入口,每个入口8位宽度;发送FIFO有128个入口,11位宽度。

接收FIFO使用每个入口的3位作为状态记录位。发送FIFO和接收FIFO使用两个独立的但是功能相同的DMA请求。

每次DMA传输的字节数在DMAC中设置,可以是8、16或者32字节。而发送FIFO没有DMA触发条件,只要空闲区域大于32字节就随时可能发生中断。

4.4.3 FICP寄存器

|

物 理 地 址 |

名 称 |

描 述 |

|

0x4080_0000 |

ICCR0 |

FICP控制寄存器0 |

|

0x4080_0004 |

ICCR1 |

FICP控制寄存器1 |

|

0x4080_0008 |

ICCR2 |

FICP控制寄存器2 |

|

0x4080_000C |

ICDR |

FICP数据寄存器 |

|

0x4080_0010 |

— |

保留 |

|

0x4080_0014 |

ICSR0 |

FICP状态寄存器0 |

|

0x4080_0018 |

ICSR1 |

FICP状态寄存器1 |

4.5 USB设备控制器(USB Device Controller,UDC)

PXA255的USB设备控制器可以实现符合USB 1.1规格的USB客户端,能支持多达16个端点,并提供了FIFO和DMA来实现与存储器的数据交换。

4.5.1 概要

UDC支持16个端点,作为从设备可以以半双工模式12Mbps的速度进行传输。UDC支持四种设备配置模式(关于配置模式的详细解释,请参考USB协议)。

4.5.2 设备配置

|

端 点 号 |

类 型 |

功 能 |

FIFO大小(bytes)×FIFO数量 |

|

0 |

控制 |

N/OUT |

16 |

|

1 |

块 |

IN |

64×2 |

|

2 |

块 |

OUT |

64×2 |

|

3 |

同步 |

IN |

256×2 |

|

4 |

同步 |

OUT |

256×2 |

|

5 |

中断 |

IN |

8 |

|

6 |

块 |

IN |

64×2 |

|

7 |

块 |

OUT |

64×2 |

|

8 |

同步 |

IN |

256×2 |

续表

|

端 点 号 |

类 型 |

功 能 |

FIFO大小(bytes)×FIFO数量 |

|

9 |

同步 |

OUT |

256×2 |

|

10 |

中断 |

IN |

8 |

|

11 |

块 |

IN |

64×2 |

|

12 |

块 |

OUT |

64×2 |

|

13 |

同步 |

IN |

256×2 |

|

14 |

同步 |

OUT |

256×2 |

|

15 |

中断 |

IN |

8 |

其中IN数据包代表从UDC发送到主控制器的数据,OUT数据包代表从主控制器到UDC的数据。

4.5.3 UDC硬件连接

1.自供电设备

在5v电源和CPU引脚之间必须插入“5V转3.3V”设备,因为CPU引脚只能接受3.3V电压。设备能用各种途径来实现,最强壮和可扩展的解决方案是诸如Power-On-Reset设备。

2.总线供电设备

4.5.4 UDC操作

1.EP0控制读操作

④ 程序检测UDCCS0[SA]和UDCCS0[OPR]位是否被设置。这代表一个EP0的缓冲区中存在一个新的OUT数据包,标记一个SETUP阶段的数据传输。

⑤ 如果UDCCS0[RNE](receiver not empty)位为1时,软件将数据读如程序的缓冲区。

⑥ 程序分析缓冲区中的数据,分析这是否是一个控制传输的读操作。

⑦ 软件开始向UDDR0寄存器中加载第一个数据包并且将程序内部的状态标志设置为EP0_IN_DATA_PHASE。

⑩ UDC发送一个IN包,其中包含了主控制器需要的数据,在主控制器发送ACK确认信号后,UDC清除UDDCS0[IPR]位,然后产生一个中断。

程序进入ISR例子,检测内部状态标记。如果处于EP0_IN_DATA_PHASE状态,这代表它需要传输更多的数据,然后加载更多的数据。内部状态标记不受影响。

然后主控制器发送一个0字节长度的STATUS OUT包,UDC设置UDDCS0[OPR]位,产生中断。

程序进入ISR例程,检查UDCCS0[OPR]是否被设置,UDCCS0[SA]是否被清空,内部状态标记是否为EP0_END_XFER。如果满足这些条件,程序将状态设置为EP0_ IDLE。

2.EP0控制读

④ 软件检测UDCCS0[SA]和UDCCS0[OPR]位是否被设置。这代表一个EP0的缓冲区中存在一个新的OUT数据包,标记一个SETUP阶段的数据传输。

⑤ 如果UDCCS0[RNE](receiver not empty)位为1时,软件将数据读如程序的缓冲区。

⑥ 程序分析缓冲区中的数据,分析这是否是一个控制传输的写操作。

⑦ 程序清除UDCCS0[OPR]和UDCCS0[SA]位并且将程序内部的状态标志设置为EP0_OUT_DATA_PHASE。

⑧ 程序设置UDCCS0[IPR]位并且向发送FIFO中加载0字节长度的数据包。

程序进入ISR例程并且检查自身是否处于EP0_OUT_DATA_PHASE状态。如果UDCCS0[OPR]位被设置并且UDCCS0[SA]位被清除,则这代表有更多的数据需要接收。

在UDCCS0[RNE]为1时,程序将数据转移到程序缓冲区,清除UDDCCS0[OPR]位。

程序设置UDCCS0[IPR]位,允许premature STATUS IN包。

在发送完控制命令后,主控制器发送STATUS IN包,标明控制端将不会发送任何数据。

UDC接收到STATUS IN包后,会返回0字节长的数据包。这会产生一个中断。

程序进入ISR服务例程,查看自身是否处于EP0_OUT_DATA_PHASE状态而且eUD CCS0[OPR]和UDCCS0[IPR]位是否被清除,这标记一个STATUS IN包的接收。

程序比较接收到的包中标记的字节数和SETUP包中标记需要发送的字节数。如果已经发送了正确的数据则程序设置内部状态为EP0_IDLE,否则丢弃所有剩余数据和指针。

注意,如果在一次发送期间,主控制器又发送了一个SETUP命令,那么UDC必须立即终止当前的传输过程。

3.EP1块数据传输(BULK-IN)

当程序接收到来自主控制器的SETUP VENDOR命令,建立端点1的传输时,UDC可以选择以下两种方式中的一种来作为传输模式:

n 关闭端点1的中断功能,使能DMA控制器,由DMA处理数据传输;

① 在接收到SETUP VENDOR命令后,软件使能DMA控制器并且屏蔽端点1的中断。DMA开始地址必须是16字节对齐的。

n 如果包大小为64字节,程序可以将所有数据通过一个DMA描述符进行传输。

n 如果包大小小于64字节,程序应当建立DMA描述符队列,其中奇数序列的描述符指向数据,偶数序列的描述符中的数据被写入UDCCS1[TSP]。

④ DMA控制器填充端点1的FIFO(UDDR1)。如果数据包长度小于标准数据包的长度,则设置UDCCS1[TSP]。

如果软件使能端点1的中断允许Megacell直接处理数据,则按照下列步骤进行数据传输:

① 在接收到SETUP VENDOR命令后,程序用数据填充端点1的FIFO(UDDR1),清除UDCCS1[TPC]。如果数据包为短数据包(大小小于标准数据包),还要清除UDCCS1[TSP]。

② 主控制器发送BULK-IN包,UDC回送一个数据包,并且产生一次中断。

③ 程序填充端点1的数据FIFO(UDDR1),清除UDCCS1[TPC]。如果数据包为短数据包(大小小于标准数据包),还要清除UDCCS1[TSP]。

4.EP2块数据接收(BULK-OUT)

在端点7和12上同样也有本操作类型。当UDC接收到SETUP VENDOR命令建立端点2块数据传输(BULK OUT),程序可以选择以下两种模式中的一种:

n 关闭端点1的中断功能,使能DMA控制器,由DMA处理数据传输;

以上两种模式的具体操作步骤和“EP1块数据传输(BULK-IN)”章节中描述的类似。

5.EP3同步数据发送(ISOCHRONOUS-IN)

本节描述的传输方式同样也适用在端点8和13上。在本节描述的传输方式中,只有当数据包大小小于256个字节时,才会被认为是短数据包。同样,同步数据发送也可以采用多种方式:

n 使能SOF(Start of Frame)中断来处理数据(有关SOF,请参考USB协议)。

① 在接收到SETUP VENDOR命令后,程序使能DMA控制器屏蔽端点3的中断。DMA开始地址必须是16字节对齐的。.

n 如果包大小为256字节,则程序可以通过一个DMA描述符来发送所有数据(256字节)。

n 如果包大小小于256字节,如果包大小小于256字节,程序应当建立DMA描述符队列,其中奇数序列的描述符指向数据,偶数序列的描述符中的数据被写入UDCCS1[TSP]。

④ DMA控制器填充端点3的数据FIFO(UDDR3),如果是短数据包,还要设置UDCCS3[TSP]。

如果程序使能端点1的中断允许Megacell直接处理数据,则按照下列步骤进行数据传输:

① 在接收到SETUP VENDOR命令后,程序用数据填充端点3的FIFO(UDDR3),清除UDCCS3[TPC]。如果数据包为短数据包,还要清除UDCCS3[TSP]。

② 主控制器发送ISOC-IN包,UDC回送一个数据包,并且产生一次中断。

③ 程序填充端点3的数据FIFO(UDDR3),清除UDCCS3[TPC]。如果数据包为短数据包(大小小于标准数据包),还要清除UDCCS3[TSP]。

如果程序使能端点3的SOF中断,则按照下列步骤进行数据传输:

① 程序通过设置UICR0[IM3]禁止UDCCS3中断,清除UFNHR[SIM]位来使能SOF中断。

② 当主控制器发送SOF后,UDC设置UFNHR[SIR]位,这将产生一次SOF中断。

6.EP4同步数据接收(ISOCHRONOUS-OUT)

本操作模式同样也可适用于端点9和14。当程序接收到SETUP VENDOR命令建立端点4同步接收连接时,可以采用多种方式传输数据:

n 使能SOF(Start of Frame)中断来处理数据。

7.复位中断处理

② 程序设置UDCCR[UDE]位来使能UDC,然后立即读取UDCCR[UDA]位来判断总线上是否有USB复位信号。

n 如果UDCCR[UDA]为0,表明总线上有USB复位信号,程序应当设置UDCCR [RSTIR]来清除中断,然后清除UDCCR[REM]位来允许将来的复位中断。

n 如果UDCCR[UDA]为1,总线上没有USB复位信号,程序通过清除UDCCR[REM]位来允许将来的复位中断。

④ 主控制器可以断言一个Assertions Reset USB中断或者Reset Negation USB中断。

⑥ 软件判断UDCCR[RSTIR]位是否被设置,然后清除中断(设置UDCCR[RSTIR])。接着程序检查UDCCR[UDA]位,来确定已经产生的复位的类型。

n 如果UDCCR[UDA]为0,代表断言的复位。程序从中断返回,等待Reset Negation中断。

n 如果UDDCR[UDA]为1,则产生的是Reset Negation。程序做必要的初始化。

8.SUSPEND中断处理

① 程序开始运行时,清除UDCCR[SRM]位来允许USB suspend中断。

② 主控制器通过截断UDC+和UDC-上的信号,断言一个USB suspend。

④ 中断程序检查UDCCR[SUSIR]位是否被设置。这代表了是否产生了一个USB suspend。如果的确产生了一个USB suspend中断,则UDC关闭外设,清除内部数据缓冲区,切换电源状态等。

9.RESUME中断处理

① 在程序开始运行时,清除UDCCR[SRM]位,允许产生USB resume中断。

② 主控制器通过恢复UDC+和UDC-上被截断的信号,断言一个USB resume。

④ 中断服务程序判断UDCCR[RESIR]位是否被设置。这代表是否已经产生了一个USB resume命令,然后后续程序可以恢复设备供电、初始化数据缓冲区等操作。

4.5.5 UDC寄存器一览

|

地 址 |

寄存器名字 |

描 述 |

|

0x4060_0000 |

UDCCR |

UDC控制寄存器 |

|

0x4060_0004 |

- |

保留 |

|

0x4060_0008 |

UDCCFR |

UDC功能寄存器 |

|

0x4060_000C |

- |

保留 |

|

0x4060_0010 |

UDCCS0 |

UDC端点0控制/状态寄存器 |

续表

|

地 址 |

寄存器名字 |

描 述 |

|

0x4060_0014 |

UDCCS1 |

UDC端点1(IN)控制/状态寄存器 |

|

0x4060_0018 |

UDCCS2 |

UDC端点2(OUT)控制/状态寄存器 |

|

0x4060_001C |

UDCCS3 |

UDC端点3(IN)控制/状态寄存器 |

|

0x4060_0020 |

UDCCS4 |

UDC端点4(OUT)控制/状态寄存器 |

|

0x4060_0024 |

UDCCS5 |

UDC端点5(中断)控制/状态寄存器 |

|

0x4060_0028 |

UDCCS6 |

UDC端点6(IN)控制/状态寄存器 |

|

0x4060_002C |

UDCCS7 |

UDC端点7(OUT)控制/状态寄存器 |

|

0x4060_0030 |

UDCCS8 |

UDC端点8(IN)控制/状态寄存器 |

|

0x4060_0034 |

UDCCS9 |

UDC端点9(OUT)控制/状态寄存器 |

|

0x4060_0038 |

UDCCS10 |

UDC端点10(中断)控制/状态寄存器 |

|

0x4060_003C |

UDCCS11 |

UDC端点11(IN)控制/状态寄存器 |

|

0x4060_0040 |

UDCCS12 |

UDC端点12(OUT)控制/状态寄存器 |

|

0x4060_0044 |

UDCCS13 |

UDC端点13(IN)控制/状态寄存器 |

|

0x4060_0048 |

UDCCS14 |

UDC端点14(OUT)控制/状态寄存器 |

|

0x4060_004C |

UDCCS15 |

UDC端点15(中断)控制/状态寄存器 |

|

0x4060_0050 |

UICR0 |

UDC中断控制寄存器0 |

|

0x4060_0054 |

UICR1 |

UDC中断控制寄存器1 |

|

0x4060_0058 |

USIR0 |

UDC状态中断寄存器0 |

|

0x4060_005C |

USIR1 |

UDC状态中断寄存器1 |

|

0x4060_0060 |

UFNHR |

UDC帧数目高位寄存器 |

|

0x4060_0064 |

UFNLR |

UDC帧数目低位寄存器 |

|

0x4060_0068 |

UBCR2 |

UDC字节计数寄存器2 |

|

0x4060_006C |

UBCR4 |

UDC字节计数寄存器4 |

|

0x4060_0070 |

UBCR7 |

UDC字节计数寄存器7 |

|

0x4060_0074 |

UBCR9 |

UDC字节计数寄存器9 |

|

0x4060_0078 |

UBCR12 |

UDC字节计数寄存器12 |

|

0x4060_007C |

UBCR14 |

UDC字节计数寄存器14 |

|

0x4060_0080 |

UDDR0 |

UDC端点0数据寄存器 |

|

0x4060_0100 |

UDDR1 |

UDC端点1数据寄存器 |

|

0x4060_0180 |

UDDR2 |

UDC端点2数据寄存器 |

|

0x4060_0200 |

UDDR3 |

UDC端点3数据寄存器 |

|

0x4060_0400 |

UDDR4 |

UDC端点4数据寄存器 |

续表

|

地 址 |

寄存器名字 |

描 述 |

|

0x4060_00A0 |

UDDR5 |

UDC端点5数据寄存器 |

|

0x4060_0600 |

UDDR6 |

UDC端点6数据寄存器 |

|

0x4060_0680 |

UDDR7 |

UDC端点7数据寄存器 |

|

0x4060_0700 |

UDDR8 |

UDC端点8数据寄存器 |

|

0x4060_0900 |

UDDR9 |

UDC端点9数据寄存器 |

|

0x4060_00C0 |

UDDR10 |

UDC端点10数据寄存器 |

|

0x4060_0B00 |

UDDR11 |

UDC端点11数据寄存器 |

|

0x4060_0B80 |

UDDR12 |

UDC端点12数据寄存器 |

|

0x4060_0C00 |

UDDR13 |

UDC端点13数据寄存器 |

|

0x4060_0E00 |

UDDR14 |

UDC端点14数据寄存器 |

|

0x4060_00E0 |

UDDR15 |

UDC端点15数据寄存器 |

4.6 AC'97控制器

PXA255在提供I2S控制器的同时,也提供了另外一种实现数字音频的接口——AC'97,大大增加了系统设计和实现的灵活性。

4.6.1 概要

4.6.2 功能列表

n 独立的通道:立体声脉冲编码调制(PCM)输入,立体声脉冲编码调制(PCM)输出,调制解调输出,调制解调输入。以上所有的通道,在硬件上只支持16位的样本,对于少于16位的样本,应当由软件进行处理;

n 多重采样频率AC'97 2.0 CODEC(48kHz或者更低)。ACUNIT通过CODEC来控制采样频率;

4.6.3 信号描述

表4-16列出了AC-Link需要使用的引脚名称(面向外部解码器):

|

引 脚 名 称 |

方 向 |

功 能 描 述 |

|

nACRESET |

输出 |

低电平有效,复位外部解码器寄存器 |

|

GP28/BITCLK |

输入 |

12.288MHz比特频率时钟. |

|

GP31/SYNC |

输出 |

48kHz帧标识和同步信号 |

|

GP30/SDATA_OUT |

输出 |

串行音频数据输出 |

|

GP29/SDATA_IN_0 |

输入 |

来自外部解码器的串行音频数据输入 |

|

GP32/SDATA_IN_1 |

输入 |

来自二级外部解码器的串行音频数据输入 |

信号引脚配置步骤

① 将SYNC和SDATA_OUT配置成输出。

② 将BITCLK,SDATA_IN_0,和SDATA_IN_1配置成输入。

③ nACRESET只能配置成输出,并且在上电后一直处于有效状态。通过全局控制寄存器(GCR)设置GCR[COLD_RST]位来使nACRESET无效。

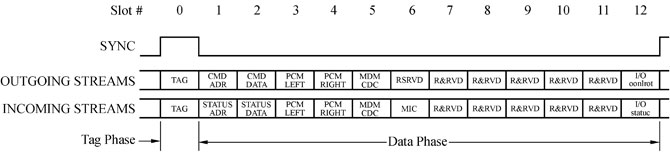

4.6.4 AC-link数字串行接口协议

ACUNIT为所有AC-link上的数据传输提供了同步机制。一次数据传输(一帧)由256位数据组成,分割成13个时间槽。

|

通 道 |

时 段 |

描 述 |

|

PCM回放 |

两个输出时段 |

两通道合成PCM输出流 |

|

PCM录音数据 |

两个输入时段 |

两通道合成PCM输入流 |

|

CODEC控制 |

两个输出时段 |

控制寄存器写端口 |

|

CODEC状态 |

两个输入时段 |

控制寄存器读端口 |

|

Modem线路CODEC输出 |

一个输出时段 |

Modem线路CODEC DAC输入流 |

|

Modem线路CODEC输入 |

一个输入时段 |

Modem线路CODEC ADC输出流 |

|

专用麦克风输入 |

一个输入时段 |

支持立体声AEC和其他语音应用的专用麦克风输入流 |

|

I/O控制 |

一个输出时段 |

专用于Modem CODEC的GPO的时段 |

|

I/O状态 |

一个输入时段 |

专用于Modem CODEC的GPI的时段 |

时间槽0被成为标记阶段(Tag Phase),16位长。其他12个时间槽为数据阶段(Data Phase)。标记阶段包含了1位的帧有效位,和12位定义数据槽有效的位。每个数据阶段的时间槽都是20位长。

当SYNC引脚被拉高时,开始一帧的传输。SYNC被拉高的时间长度由标记阶段的数据长度决定。AC'97的帧按照12.288MHz比特时钟,以48kHz的固定频率产生。

ACUNIT和解码器使用SYNC和BITCLK来决定传输或者接收数据的时间。在BITCLK的上升沿发送数据,在BITCLK的下降沿接收数据。发送器必须在数据流中指明有效时间槽(有效时间槽在时间槽0中的12位定义)。AC-link的串行数据传输顺序从MSB(最高位)到LSB。标记段的最先传输位为第15位(从第0位算起),数据段的最先传输位为第19位(从第0位算起)。

图4-14显示了ACUNIT和CODEC通信中使用的帧的结构。由一个标记段(时间槽0)和12个数据段组成。

图4-14 CODEC通信帧结构

1.AC-link音频输出帧(SDATA_OUT)

每个音频输出帧支持最多12个20位的输出时间槽。ACUNIT产生的样本数据容量都大于16位。最低4位用0填充。图4-15所示是音频输出帧的时序图。

图4-15 音频输出帧的时序图

一个新的音频输出帧的传输由SYNC和BITCLK信号的同步上升沿开始。紧接着是BITCLK的下降沿,此后SYNC在数据传输过程中一直保持高电平。BITCLK的下降沿标记了AC-link链接的两端都已经意识到开始了一个新的音频输出帧。在下一个BITCLK的上升沿,ACUNIT开始传输时间槽0的第一位(Valid Frame Bit)。每位都在BITCLK的上升沿被传输,然后由AC'97控制器在下一个BITCLK下降沿接收。

2.AC-link音频输入帧(SDATA_IN)

ACUNIT有主从两条SDATA_IN输入线。每条线可以和外部解码器连接。CODEC的类型决定了帧中的时间槽的有效性。两条线上输入数据完全是正交的,不会存在同一位置上的两个时间槽都有效的现象。多重输入数据流在每个时间槽边沿上被接收和合成,时间槽边沿有时间槽有效位标记。每个AC-link音频输入帧由12个20比特的时间槽组成。

软件在将ACUNIT设置成数据传输模式之前必须检查音频输入帧的第一位(SDATA_IN slot 0,bit 15)确保解码器处于就位状态。当解码器已经处于就位状态,才能接收后12比特的数据,它们标记12个数据槽的有效性。

图4-16所示是一个音频输入帧的时序图,其时序和发送帧相类似。

图4-16 音频输入帧的时序图

4.6.5 AC-link低功耗模式

4.6.6 AC-link的唤醒

1.由解码器触发唤醒

2.由ACUNIT触发唤醒

AC-link协议提供了AC'97冷复位和热复位的功能。当前的断电模式决定了复位方式。所有寄存器中的内容必须保持一致,直到发生冷复位。在冷复位发生以后,所有寄存器被恢复到默认值。

4.6.7 ACUNIT操作

ACUNIT可以通过处理器或者DMA控制器进行操作。处理器使用GPIO对ACUNIT进行操作,并且可以操作4种寄存器类型:

n CODEC寄存器:音频或者调制解调解码器可以支持最多64个寄存器;

n Modem CODEC GPIO寄存器:如果ACUNIT连接到一个调制解调器CODEC,就可以访问CODEC GPIO寄存器,它们使用了CODEC的地址0x0054;

n ACUNIT FIFO数据寄存器:对于音频输出和调制解调输出,ACUNIT包含两个发送FIFO;对于输入,则有3个FIFO。

n 当PCM FIFO中的数据达到容量一半时,PCM FIFO传输和接收DMA请求;

n 当调制解调FIFO中的数据达到容量一半时,调制解调FIFO传输和接收DMA请求;

1.初始化

AC'97解码器和ACUNIT在系统上电后被复位。在系统上电后,nACRESET信号一直维持在高电平,直到软件设置GCR的COLD_RST位为1。可以按照以下步骤来初始化ACUNIT。

② 设置GCR的COLD_RST位为1,使nACRESET无效。在这步之前,所有寄存器都处于被复位状态。使nACRESET无效会带来以下影响:

③ 使能主Ready中断,或者二级Ready中断(通过设置GCR PRIRDY_IEN和SECRDY_ IEN)。

⑤ ACUNIT触发DMA传输请求,DMA填充FIFO作为回应。

⑥ ACUNIT不断发送0值,直到发送FIFO中的数据达到容量的一半。然后数据通过AC-Link发送。

2.操作解码器寄存器的步骤

当获取AC-link的占用锁后,程序可以通过对应的处理器物理地址来访问解码器寄存器。ACUNIT在解码器写操作完成后会自动设置GSR寄存器的CDONE位。程序可以直接向其中写入1来清除这个位。

① 程序首先产生一个对解码器寄存器的预读操作。作为响应,ACUNIT返回有效数据。ACUNIT随后通过AC-link初始化读寄存器。

② 当解码器读操作完成后,ACUNIT自动设置GSR寄存器的SDONE位为1。程序可以通过向其中写入1来清除这个位。

③ 程序重复步骤1中的读操作,然后ACUNIT返回解码器发送的数据。

④ 如果解码器没有在4个SYNC帧内回应有效数据,则ACUNIT认为读操作超时,这样第二次读操作将返回0x0000_FFFF。

4.6.8 时钟和采样频率

4.6.9 功能描述

1.FIFO

n Modem发送FIFO,16个32位入口(高16位必须为0);

n Modem接收FIFO,16个32位入口(高16位必须为0);

n Mic-in接收FIFO,16个32位入口(高16位必须为0)。

2.中断

n Mic-in FIFO错误:Mic-in接收FIFO数据溢出或者没有接收到数据。

n Modem-in FIFO错误:Modem接收FIFO数据溢出或者没有接收到数据。

n PCM-in FIFO错误:音频接收FIFO数据溢出或者没有接收到数据。

n Modem-out FIFO错误:Modem发送FIFO’s数据溢出或者没有接收到数据。

n PCM-out FIFO错误:音频发送FIFO数据溢出或者没有接收到数据。

n Modem CODEC GPI状态迁移中断:如果时间槽12的比特0被设置为1,则产生本中断。这标记了调制解调GPIO寄存器中有一位发生了数值改变。

n 主解码器“恢复”中断(Resume Interrupt)。

n 二级解码器“恢复”中断(Resume Interrupt)。

n 解码器命令完成中断:当解码器寄存器中的命令完成时,产生本中断,软件可以向本位中写入1来清除中断标记。

n 解码器状态完成中断:当解码器寄存器的状态地址和数据接收完成时,产生本中断,软件可以向本位中写入1来清除中断标记。

n 主解码器就绪中断:当主解码器就绪时,设置状态寄存器中相应的位。解码器设置时间槽0的位0为1来标记解码器就绪。程序清除GCR寄存器的PRIRDY_IEN位来清除本中断。

n 二级解码器就绪中断:当主解码器就绪时,设置状态寄存器中相应的比特位。解码器设置时间槽0的位0为1来标记解码器就绪。程序清除GCR寄存器的SECRDY _IEN位来清除本中断。

3.寄存器描述

n 全局寄存器,ACUNIT有3种全局寄存器──状态、控制和解码器访问寄存器;

n 通道特定的音频ACUNIT寄存器,用于PCM-out、PCM-in和Mic-in通道;

n 通道特定的调制解调寄存器,用于modem-out和modem-in通道;

4.7 时钟和电源管理功能

时钟和电源是一个电子系统中非常关键的要素,PXA255在时钟和电源的管理上提供了丰富的控制功能,大大增强了PXA255在对功耗敏感的手持设备的应用能力。

4.7.1 时钟管理器介绍

4.7.2 电源管理器介绍

时钟和电源管理器可以控制处理器进入或者退出任何低功耗模式或者其他特殊时钟驱动模式,这些模式如下。

n Turbo模式:CPU核以最高频率运行。在这个模式下,尽可能少地操作外部存储器,因为CPU会将很多时间花费在等待存储器操作完成上。

n Run模式:CPU核以正常频率工作。在这个模式下,CPU被认为会频繁执行外部存储器访问操作,因此降低CPU工作频率,节省功耗正适合访问外部速度比较慢的存储器。

n 空闲模式:CPU核没有被时钟信号驱动,而系统其他设备仍然具备所有运行功能。

n 睡眠模式:CPU将被设置成最低功耗状态,然而保留I/O状态、RTC和时钟及电源管理器的运行。

4.7.3 电源模式

1.Run模式

Run模式是处理器的普通操作模式。所有电源供应被打开,所有功能时钟被提供。处理器复位后就进入本工作模式。

2.Turbo模式

Turbo模式允许CPU以高频率运行。在本模式下允许频率的同步切换而不用中断存储器、LCD控制器或者其他设备的运行。

3.进入Turbo模式

程序设置了时钟配置寄存器(Clock Config,CCLKCFG)的TURBO位后,CPU就进入本模式。然后,CPU等待当前管道线内所有的指令都执行完毕,之后再开始以高频率模式继续操作。

在CCLKCFG中,其他模式的位都比本模式有优先执行权,因此如果其他位也被设置,处理器在进入本模式后,会立即切换运行模式。

4.Turbo模式下处理器的运行方式

5.退出Turbo模式

只要程序清除CCLKCFG寄存器中的TURBO位就可以退出本模式。然后CPU仍然要等到管道线中所有指令执行完毕后才会更改频率。随后处理器进入run模式。

4.7.4 空闲模式

空闲模式允许用户停止对CPU的时钟信号供应。空闲模式并不改变时钟信号的频率,因此当有中断产生时,CPU会被立刻激活,恢复到进入空闲模式之前的模式。

1.进入空闲模式

在进入空闲模式之前,所有需要执行的应用程序都应当被完成,外设如果需要CPU进行数据处理,则必须处于中断使能状态。程序设置PWRMODE[M]就可立即使CPU在执行完管道线中的指令后进入空闲模式。

2.空闲模式下处理器的运行方式

当ICCR[DIM]被设置为0时,任何中断都可以唤醒CPU;否则无效。

4.7.5 33MHz空闲模式

33MHz空闲模式是所有空闲模式中耗电量最低的。CCCR寄存器中设置的频率直接影响到空闲模式下的功耗。33MHz空闲模式在处理器进入空闲模式之前将处理器功耗设置到低速运行模式。但是本模式有一定的限制。

和普通的空闲模式不同,在33MHz空闲模式中,所有的外设都无法正常运行包括SDRAM,LCD等。

1.进入33MHz空闲模式

在本空闲模式中,处理器核被停止提供时钟信号。在时钟停止之前,所有的应用程序都应当完成,外设应当被关闭。如果程序正在SDRAM中等待处理,则应当在进入本模式之前执行下列步骤的操作:

③ 执行频率变换操作,转换到33MHz模式,CCCR中的对应值应当是0x13F。

2.33MHz空闲模式下处理器的运行方式

3.退出33MHz空闲模式

4.7.6 睡眠模式

1.睡眠准备

① 存储控制器必须被配置成能确保SDRAM内容不改变的模式。

② 在外设进入睡眠之前,必须先关闭外设。这包括监视DMA和设备或者内存之间的传输是否完成等。其他设备不必完全关闭,因为在睡眠模式中,它们处于复位状态下。

n PM GPIO睡眠状态寄存器(PGSR0、PGSR1和PGSR2)。为了避免处理器在尝试唤醒时出现总线争用的现象,应当确保片选在睡眠中没有被设置为0。

n PM通用配置寄存器Float位[FS/FP]必须被适当地配置。在唤醒时,它必须被清除。

n PMFW配置寄存器必须被配置成标准或者快速睡眠唤醒模式。

④ 在IDEA位被设置之前,程序必须配置不严密数据失败的异常例程来响应nVDD_FAULT或者nBATT_FAULT有效时的处理。这个异常表明处理器即将失去电源供应。

2.进入睡眠模式

① 程序使用外部存储器和电源管理擦除填充(Power Manager Scratch Pad Register,PSPR)来保存必要的数据,如处理器的状态等。

② 程序设置PWRMODE[M]位,这会立即引起一个退出睡眠模式的中断。

④ 存储控制器完成和CPU的数据交换。来自LCD或者DMA的新数据传输请求将被忽略。

3.睡眠模式下处理器的运行方式

在睡眠模式下,除了RTC以外所有处理器和外设都被关闭。处理器将忽略不被记录的中断和外部引脚的状态变化。只有Reset信号和nBATT_FAULT信号。

4.退出睡眠模式

当产生硬件复位信号时,处理器退出睡眠模式。通常情况下,睡眠模式在以下情况中被退出。

① 当一个预先定义的唤醒时间从GPIO或者RTC产生。如果这时候nBATT_FAULT有效,则唤醒时间被忽略。

③ 如果在睡眠模式开始时,PCFR[OPDE]和OSCC[OON]被设置,则3.6864MHz晶振被使能。否则可以跳过这步。

⑥ 处理器内部复位信号被清除并且处理器执行正常的启动操作。当正常启动操作开始后,外设和处理器核恢复正常运做。

⑦ nRESET_OUT引脚信号无效,这表明处理器已经就绪准备从复位向量表取指令执行。

⑨ 清除PCFR[FS]和PCFR[FP]如果它们先前被设置。

4.7.7 电源模式总结

表4-18和表4-19显示了进入某种电源模式和退出时需要采取的操作。

|

步骤 |

动 作 说 明 |

加速 |

运行 |

待机 |

频率变化 |

睡眠 |

Fault Sleep |

|

1 |

软件在CP14上对某一位进行写操作 |

X |

X |

X |

X |

X |

|

|

2 |

CPU等待所有指令执行完毕 |

X |

X |

X |

X |

X |

|

|

3 |

唤醒触发源被清零并被限制为GP[1:0] |

X |

|||||

|

4 |

PM将GPIO设置成睡眠状态时的电平 |

X |

X |

||||

|

5 |

存储器控制器完成所有未完成的事务 |

X |

X |

X |

|||

|

6 |

存储器控制将SDRAM设置为自刷新模式 |

X |

X |

X |

|||

|

7 |

将PLL禁止 |

X |

X |

X |

|||

|

8 |

如果OPDE和OOK位被置位,3.6864振荡器将被禁止 |

X |

X |

||||

|

9 |

复位大多数内部模块,将nRESET_OUT置位 |

X |

X |

||||

|

10 |

PWR_EN被置位,电源关闭 |

X |

X |

||||

|

11 |

大多数I/O的引脚的电源被关闭 |

|

步骤 |

动 作 说 明 |

加速 |

运行 |

待机 |

频率变化 |

睡眠 |

Fault Sleep |

|

1 |

接收到唤醒信号或者中断 |

X |

X |

X |

|||

|

2 |

恢复I/O引脚的电源 |

||||||

|

3 |

PWR_EN被置位 |

X |

X |

||||

|

4 |

外部电源加电 |

X |

X |

||||

|

5 |

如果OPDE和OOK置位,使能3.6864兆振荡器 |

X |

X |

||||

|

6 |

如果OPDE和OOK置位,等待3.6864兆振荡器稳定 |

X |

X |

||||

|

7 |

用新频率使能PLL |

X |

X |

X |

|||

|

8 |

等待PLL稳定 |

X |

X |

X |

|||

|

9 |

等待内部电路稳定 |

X |

X |

||||

|

10 |

清除CP14位 |

X |

X |

||||

|

11 |

清除nRESET_OUT标志 |

X |

X |

||||

|

12 |

重新启动CPU时钟,使能中断信号 |

X |

X |

X |

X |

X |

X |

4.7.8 电源管理寄存器

|

地 址 |

名 字 |

描 述 |

|

0x40F0_0000 |

PMCR |

电源管理单元控制寄存器 |

|

0x40F0_0004 |

PSSR |

电源管理单元睡眠状态寄存器 |

|

0x40F0_0008 |

PSPR |

电源管理单元暂时寄存器 |

|

0x40F0_000C |

PWER |

电源管理单元唤醒使能寄存器 |

|

0x40F0_0010 |

PRER |

电源管理单元GPIO上升沿检测使能寄存器 |

|

0x40F0_0014 |

PFER |

电源管理单元GPIO下降沿检测使能寄存器 |

|

0x40F0_0018 |

PEDR |

电源管理单元GPIO边沿检测状态寄存器 |

|

0x40F0_001C |

PCFR |

电源管理单元通用配置寄存器 |

|

0x40F0_0020 |

PGSR0 |

电源管理单元GPIO(GP[31~0])睡眠状态寄存器 |

|

0x40F0_0024 |

PGSR1 |

电源管理单元GPIO(GP[63~32])睡眠状态寄存器 |

|

0x40F0_0028 |

PGSR2 |

电源管理单元GPIO(GP[84~64])睡眠状态寄存器 |

|

0x40F0_0030 |

RCSR |

复位控制器状态寄存器 |

4.7.9 时钟寄存器一览

|

地 址 |

名 字 |

描 述 |

|

0x4130_0000 |

CCCR |

核心时钟寄存器 |

|

0x4130_0004 |

CKEN |

时钟使能寄存器 |

|

0x4130_0008 |

OSCC |

振荡器配置寄存器 |

《Windows CE嵌入式开发入门——基于Xscale架构》第4章 外设控制器相关推荐

- 《Windows CE嵌入式开发入门——基于Xscale架构》 第9章 Windows CE BSP及驱动程序结构分析

9.1 Windows CE驱动程序结构概述 Windows CE的驱动程序可以从多种角度进行区分. 1.从加载以及接口方式来区分 可以分为本机设备驱动(Built-In Driver).可加载驱动 ...

- 《Windows CE嵌入式开发入门——基于Xscale架构》 第7章 Windows CE体系结构

7.1 层次式架构 1.系统分层模型 操作系统(包括应用环境.操作环境等)一般具有分层的结构特征,典型的就是UNIX系统的同心环,最里面是硬件,从里向外依次是kernel.共享函数库.应用程序3个层 ...

- 《Windows CE嵌入式开发入门——基于Xscale架构》第2章 系统时钟

电子系统中,时钟是一个关键的要素,尤其在手持设备中,时钟系统的设计与系统的性能和功耗有直接关系.PXA255提供了丰富的时钟系统的控制能力,能有效地实现性能和功耗的平衡. 2.1 实时时钟RTC 在 ...

- Windows CE嵌入式系统程序开发

<Windows CE嵌入式系统程序开发> 基本信息 作者: 胡文 冯剑 姜海涛 胡玥 丛书名: 单片机与嵌入式丛书 出版社:机械工业出版社 ISBN:978711 ...

- RISC-V嵌入式开发入门篇2:RISC-V汇编语言程序设计(中)

原文出处:https://mp.weixin.qq.com/s/3RHss3vhfK004-TtM8fpeA 随着国内第一本RISC-V中文书籍<手把手教你设计CPU--RISC-V处理器篇&g ...

- 安信可PB-03蓝牙模组入门之旅 二:SDK二次开发入门,认识架构,开始点亮一盏LED。

本系列博客学习由非官方人员 半颗心脏 潜心所力所写,仅仅做个人技术交流分享,不做任何商业用途.如有不对之处,请留言,本人及时更改. 1. 安信可PB-03蓝牙模组入门之旅一:Windows SDK二次 ...

- Swift项目开发实战-基于分层架构的多版本iPhone计算器-直播公开课

Swift项目开发实战-基于分层架构的多版本iPhone计算器-直播公开课 本课程采用Q Q群直播方式进行直播,价值99元视频课程免费直播.完整的基于Swift项目实战,手把手教你做一个Swift版i ...

- PaaS的发展将释放物联网开发效率 ——基于云架构的物联网云平台解决方案

PaaS的发展将释放物联网开发效率 --基于云架构的物联网云平台解决方案 2018年7月6日.7日,为期两天的 ArchSummit 全球架构师峰会在深圳·华侨城洲际酒店拉开帷幕.在7月6日解决方案专 ...

- 嵌入式开发入门之经典 ARM开发板

嵌入式开发入门之经典 开始进入嵌入式世界,真是一头雾水,不知道如何入手!也不知道该如何学习,学习什么,最近从网上转载这篇文章,对我启发很大,对于初始进入嵌入式的人们很有帮组,好多嵌入式大侠都说这是入门 ...

最新文章

- ESP-TOUCH编码规则及解码

- 大志非才不就,大才非学不成—博文资源汇总

- 埃拉托斯特尼筛法(埃筛)

- SAP 4.6C升级ECC6.0 WS_QUERY 的改法

- 你真的了解引用传递与值传递吗?

- leetcode79. 单词搜索(回溯算法)

- OSChina 周日乱弹 —— 快喊爸爸

- 开机时设置linux 内核参数 mem,Linux内核开机保留大块内存的方法总结

- mysql增删改查 表格_mysql 数据表 增删改查

- 计算机多系统启动光盘制作,制作启动光盘,小编教你如何制作光盘启动盘

- 酉矩阵/幺正矩阵(Unitary Matrix)

- Docker制作深度学习镜像常用操作

- 电脑端实现微信双开(登录两个微信)

- 关于AndroidStudio打包后apk包名乱码的问题

- 维夏英语暑期调研小分队——第二天

- keras训练过程中发生的一些报错及其解决办法

- 中国二氯甲烷行业研究与投资前景预测报告(2022版)

- 影视动画制作中的后期渲染是什么意思?

- 图像拼接小实验开发日志和笔记

- 犹抱琵琶半遮面--探究直播系统源码的真面目