FPGA从Xilinx的7系列学起(4)

2. 最基本的BlockRAM

2.1 BlockRAM的初探

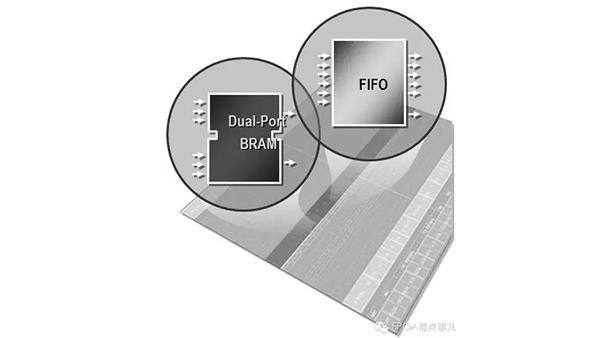

BlockRAM资源对FPGA来说也是非常重要的,我们的很多设计用到了BlockRAM以后,可以变得设计非常灵活,这样我们就可以设计出很多高效能的应用。了解BlockRAM的一些情况,对我们来说也是一个很重要的事情。

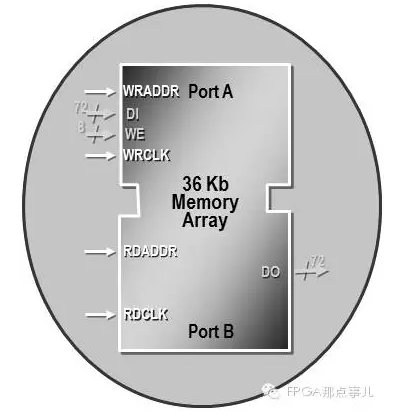

大家都知道,每个FPGA设计需要一定的内存资源。一般来说,相对于DDR来说小一点的空间,我们都是通过频繁调用的块RAM实现的。所有7系列的FPGA都具有相同架构的BlockRAM,每一块BlockRAM是36KB大小的真正的双端口存储器,经常被我们用来构建FIFO,大量的数据存储以及有限状态机,同时7系列有专用硬件,可以将BlockRAM转换成FIFO,供大家在设计的时候使用。

因为7系列器件具有相同的BlockRAM资源,这使得我们的设计能够快速的在7系列之间切换。他们和Virtex-6使用了相同的RAM资源,这样我们也可以方便的把Virtex-6中的设计升级到7系列中。

7系列的BlockRAM的时钟频率可以达到600MHz,这种结构包括输出寄存器,让更快的输出时钟速度,但是,对不起,它会增加延迟。每个RAM块具有独立的读和写端口、宽度,每个端口具有它自己的时钟和不同的读写位宽比例。 XILINX的Block RAM中包括一个可配置的端口位宽长宽比功能,这样做的好处,就是允许每个Block RAM端口有一个自定义的位宽。这有助于用户使用BlockRAM实现更多的应用,而不是需要我们在BRAM外作额外的逻辑来处理位宽差异,增强了用户的使用效率。举一个简单的例子,用户给端口A可以写数据,并且按照字节加上使用的奇偶校验位,那么用户可以从端口A读出的数据不带任何校验信息,但是从B端口,用户可以选择位宽16位,但是带2位的奇偶校验,也可用选择位宽32位,但是带4位的奇偶校验位。基本上,未来用户使用BlockRAM的时候会使用到有很多关于这方面的配置比例问题,以及如何配置用户的端口宽度的灵活性。每块XILINX的BlockRAM都可以用作真双端口存储器,简单双端口或单端口配置,这个在生成IP核的时候会遇到。

BlockRAM也可级联的,这意味着它们可以被连接在一起,形成更大的存储空间(包括BlockRAM,也包括FIFO)。和Virtex-6的BlockRAM类似,7系列的BlockRAM也有一个字节写使能信号,这对那些要使用MicroBlaze的用户来说,他们可以在比特流配置过程中初始化块存储器内容。那么,如果用户在运行复位时,仅仅只能复位就寄存器的内容,而不能复位BlockRAM的内容。当然,只要用户想要复位存储器的内容,只要重新写入新的数据即可。

和Virtex-6一样,7系列的BlockRAM有ECC功能能够修正错误的bit信息。这是专门的硬件电路来实现的,不需要用户进行相关逻辑代码来实现。另外,7系列的BlockRAM和Virtex-6的不同在于,7系列需要专门的电源来给BlockRAM提供电源。如果用户使用7系列的-1L速度等级,要注意正确的操作,-1L的核心电压有所降低,但是BlockRAM的供电需求没有降低。没有使用的BlockRAM通过配置比特流自动断电,这减小了FPGA总功率,这一点在追求低功耗的应用上,考虑使用。

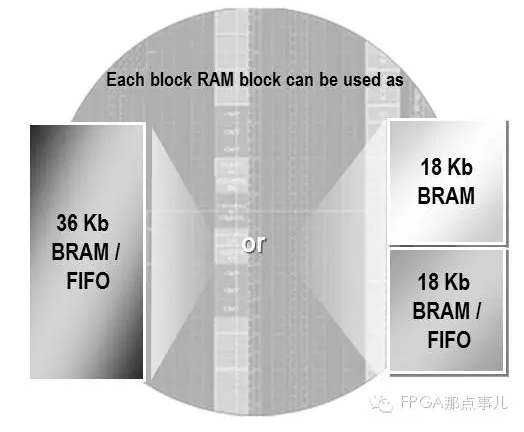

每块7系列的BlockRAM大小为36Kb的,但是允许每个BlockRAM块被分割成2个18Kb存储空间。但是18Kb的存储块不能被进一步分割。这样就保证了BlockRAM的有效使用,也增加了灵活性。这个功能非常有意思,因为它能够保证你不会浪费你的BlockRAM存储器,让你享受到仿佛更多的存储空间,用户可以用它来传递不同时钟域的数据,可以用来作为FIFO, 至于怎么用,用户可以根据需求雕琢一下即可。

用户只要想把FPGA功能发挥到极致,建议必须考好考虑XILINX给提供的这个功能。这一点与Spartan-6和Virtex-6不同,用户使用时要注意。

2.2 7系列BlockRAM资源的小结

对7系列的FPGA的BlockRAM做一个简单的总结:

7系列都具有相同的BlockRAM架构;可以实现完全同步操作,所有输出锁存;可选内部流水线寄存器,提高工作频率;两个独立的端口访问存储数据,包括独立的地址,时钟,写使能,时钟使能,独立的数据宽度;IP核配置时,有多个配置选项:真正的双端口,简单双端口,单端口;可以级联,生成更大的存储空间;按照字节使能;专用电路高效配置电路;具有ECC功能;独立Vbram供电,但是要注意-1L BlockRAM存储器供电电源的使用。

2.3 7 系列BlockRAM使用三种模式

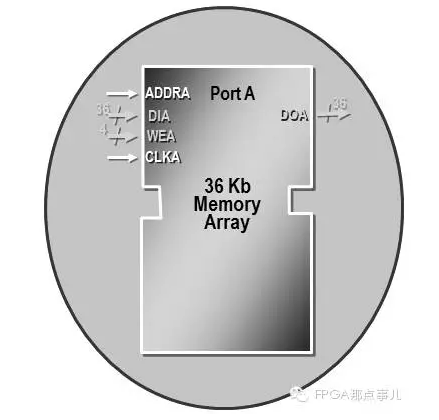

2.3.1 简单单口BlockRAM

如上图所示,简单的单口RAM的端口非常简单:

时钟: CLKA,

地址: ADDRA

写使能: WEA,

写数据: DIA,

读数据: DOA,

还有一些其他的非必须的端口图中就没有一一列出来了。

以前我们讲过,BlockRAM都是真正的双口RAM,但是有时候需要简单有效的配置方式,用户就会选择使用简单的单口RAM的模式。类似于中国人说的弱水三千只取一瓢,你纵使有各种的灵活性,我还是选择最适合我的配置方式。由于BlockRAM可以分割成36K或18K位的大小,下面列出来当用户你完全使用36Kb RAM的时候能够配置的方式和用户只使用18Kb RAM的时候能够配置的模式。对于36Kb大小的空间可以配制成:32k x 1, 16k x 2, 8k x 4, 4k x 9, 2k x 18, 1k x 36;对于18Kb的空间可以配置成: 16k x 1, 8k x 2, 4k x 4,2k x 9, 1k x 18, 512 x 36。另外也允许用户配置的写模式有三种:

WRITE_FIRST: 同时读写相同地址时,从DIA写入的数据立即在DOA上可见,也就是写优先;

READ_FIRST: 同时读写相同地址时,以前的数据还是出现在DOA上,也就是读优先;

NO_CHANGE: DOA一直保持以前的数据(可以节省功耗)。

这些配置都是你在例化BlockRAM的GUI界面上可以选择的。

另外说一下,除了上面显示的信号,简单的端口RAM端口还有其他端口:

读使能:ENA,

输出锁存器复位:RSTRAMA,

输出寄存器复位:RSTREGA

输出寄存器芯片使能:REGCEA,

为简化起见,DIA和DOA总线被示出为包括校验位,校验位和数据实际是不同的总线,他们分别是DIPA和DOPA。RST,CE,和CLK信号高低有效的使能是可编程的决定。其他RST信号是同步的Reset信号。REGCEA优先级是否超过RSTREGA是通过RSTREG_PRIORITY属性来编程。另外,即使是写使能不是有效的时候,也要确保Address线上没有时序错误。

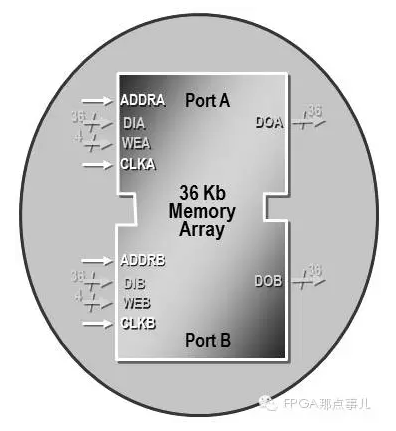

2.3.2 真正的双口Block RAM

端口信息如图所示,就不一一赘述了。真正的双端口的RAM有两个独立的读/写端口,每个端口都有独立的时钟、地址、输入数据、输出数据、写使能等等。两个端口的时钟可以设置成同步或者异步;和简单的端口RAM不同的是真正的双端口RAM可以配置成不同的宽度。同时两个端口可以具有不同的写模式。那么就要求用户在写之前执行读,或者读之前执行写。这在例化BlockRAM的GUI界面中设置。这是非常重要,用户可以进行对一个位置进行读写,但是这个操作可能导致用户需求数据发生冲突产生错误,所以必须确保您的地址和控制信号不会造成数据冲突。只有在一种情况下不会发生错误,就是读写的时钟相同,写端口的写模式是READ_FIRST,读端口是要求使用旧数据。

2.3.3 简单的双口Block RAM

端口信息同样如图所示,也就不一一赘述了。BlockRAM有时候会被配置成为简单的双端口RAM。在这种配置模式下,每个端口分配为读或写功能,根据用户使用的BlockRAM大小,可以被配制成不同的模式:对于36Kb大小的空间的,两个端口中的一个被配置成72位;对于18Kb的空间的,两个端口中的一个被配置成32位。这是因为如果宽端口是没有必要的,用户只需要使用一个真实的双端口RAM来代替,甚至一个简单的双端口RAM的功能就足够了。

FPGA从Xilinx的7系列学起(4)相关推荐

- FPGA从Xilinx 的7系列学起(1)

FPGA进入到一个工艺越来越牛的境界,很多人在学习FPGA的时候还在墨守陈规的从Spartan3学起,还是在ISE开始着手,总是觉得工艺是类似的,方法也是类似的.在和很多工程师一起讨论的时候,就明确的 ...

- FPGA从Xilinx的7系列学起(7)

3.最基本的DSP资源 3.1 由FIR滤波器谈起 随着各种应用复杂度的不断提升,传统的DSP和处理器的架构无法支持这么复杂的并行数据算法的需求.FPGA却恰好能够满足这样的需求.FPGA拥有大量的D ...

- FPGA从Xilinx的7系列学起(6)

用户必须要认识到,学习一下技巧可以让更多的逻辑放在更少的Slice中,使工具能够达到既实现设计时序要求又满足用户对功耗的要求.而现在很多用户缺乏代码编写的想法,编写出一个有时序问题的设计.为了满足要求 ...

- FPGA从Xilinx 的7系列学起(5)

2.4 BlockRAM的级联 7系列BlockRAM存储器可以把两个相邻RAM使用专用的布线资源级联到一起.这个对于工程师的重要性在于仅仅级联两块RAM的时候,可以考虑节省不少的资源.从上面说讲述中 ...

- FPGA从Xilinx的7系列学起(3)

1.3再深入一点的了解CLB 这个图有点大,但是太经典了,搞得我不得不放弃扔掉它的想法.是不是有人已经看迷糊了.那咱就慢慢的清晰呗.有时候也不一定要一开始明白,如果一开始明白,那么会越来越糊涂. 那么 ...

- FPGA从Xilinx的7系列学起(2)

1. 最基本的CLB CLB是FPGA最最基本的单元,不能说是类似于质子和中子的概念,但也至少是原子和分子的概念了.如果是最根本的单元都无法能够很好的理解,那么其实很多FPGA的原理还是停留在一个写写 ...

- 基于Xilinx的Kintex-7系列XC7K325T的硬件加速卡

产品型号: B-PCIE-K7F5XILINX的Kintex-7系列FPGA处理器 B-PCIE-K7F5是一款基于PCI Express总线架构的高性能FPGA算法加速卡,该板卡采用Xilinx的高 ...

- Xilinx FPGA资源解析与使用系列——Transceiver(十)PRBS、RX Equalizer、CDR

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 Xilinx FPGA资源解析与使用系列--Transceiver(十)PRBS.RX Equalizer.CDR PRBS测试序列 ...

- Xilinx FPGA资源解析与使用系列——Transceiver(一)参考时钟解析

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 Xilinx FPGA资源解析与使用系列--Transceiver(一)参考时钟解析 前言 IP核的部分设置 Quad 的定义是什么? ...

最新文章

- python爬虫,爬取猫眼电影1(正则表达式)

- 别傻了,年轻人买“养生奶茶”才不是为了养生!

- Could not write file: C:\......\.classpath

- 图的遍历算法【数据结构F】

- 对于不是特别擅长Photoshop的人来说,熟悉和运用Photoshop工具提供的各类便捷的快捷键,是有帮助的。...

- Mac中docker版本的ElasticSearch和Kibana安装及操作

- ROS☞rosbag/rostopic消息记录、回放、转.txt

- VS2008(C#)制作网页Tab标签切换方法(四)

- 【Python实例第14讲】普通判别分析与缩水判别分析

- 转正述职报告怎么写?五年经验PM告诉你……

- 远程桌面要求更改电源_远程工作实际上可以使老板动态改变电源

- input框的23种类型

- mysql数据库设计教材_mySQL教程 第1章 数据库设计

- 数学建模之熵权法——基于Topsis模型

- 【kafka专栏】集成apache kafka-clients实现数据消费者

- Go语言核心之美 3.4-Struct结构体

- leet234.回文链表

- 定时循环发送TCP消息(例如:控制设备的开关机等场景)—— 定时执行专家

- android 微信抢红包软件

- Elasticsearch:Data streams(三)

热门文章

- 华为p4支持鸿蒙功能吗_吹过的牛都一步一步给实现了!明年华为手机支持升级鸿蒙系统!...

- 关于一道简单的Java 基础面试题的剖析: short s1=1;s1 = s1 +1会报错吗?

- assign深拷贝_经典前端面试题: Object.assign 是浅拷贝还是深拷贝?实现深拷贝的方法有哪些?...

- 双流棠湖中学怎么样_全川前十高中,棠湖中学后来居上,七中、四中、成外是“大佬”...

- 项目服务器有15个能说明什么,15.1 我的面试经历 by smyhvae - 前端入门进阶

- amqp协议_AMQP协议、模型及RabbitMQ常用组件

- oracle 新增自增字段,SQL server、Oracle中拿到新增列时的自增字段值

- 智能车竞赛技术报告 | 节能信标组 - 重庆大学- 赛博坦汽车人联盟

- 关于智能车竞赛程序公正问题的讨论

- 2021年春季学期-信号与系统-第五次作业参考答案-第五小题