32位单精度浮点乘法器的FPGA实现

关键词: 浮点乘法器; Boo th 算法; W allace 树; 波形仿真

随着计算机和信息技术的快速发展, 人们对微处理器的性能要求越来越高。乘法器完成一次乘法操作的周期基本上决定了微处理器的主频, 因此高性能的乘法器是现代微处理器中的重要部件。本文介绍了32 位浮点阵列乘法器的设计, 采用了改进的Booth 编码, 和Wallace树结构, 在减少部分积的同时, 使系统具有高速度, 低功耗的特点, 并且结构规则, 易于VLSI的实现。

1 乘法计算公式

32 位乘法器的逻辑设计可分为: Booth编码与部分积的产生, 保留进位加法器的逻辑, 乘法阵列的结构。

1.1 Booth编码与部分积的逻辑设计

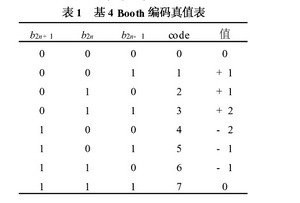

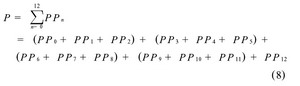

尾数的乘法部分,本文采用的是基4 Booth编码方式, 如表1。首先规定Am和Bm表示数据A和B的实际尾数,P 表示尾数的乘积, PPn表示尾数的部分积。浮点32 位数, 尾数是带隐含位1 的规格化数, 即: Am =1×a22a21….a0和Bm = 1 ×b22b21.…b0, 由于尾数全由原码表示,相当于无符号数相乘, 24 × 24 位尾数乘积P 的公式为:

1.2 乘法器的阵列结构

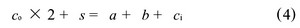

本文采用的是3 -2 加法器, 输入3 个1 位数据: a, b,ci; 输出2 个1 位数据: s, Co。运算式如下:

其逻辑表达式如下:

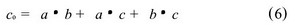

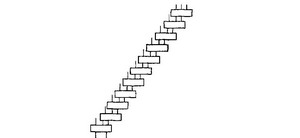

当每个部分积PPn 产生之后, 将他们相加便得到每个乘法操作的结果。相加的步骤有很多, 可采用的结构和加法器的种类也很多。比如串行累加:

而Wallace 树的乘法阵列如下:

加法器之间的连接关系如图1, 图2 所示, 或者从公式(7) 与(8) 中可以看出, 图1中串行累加的方法延迟为11个3-2 加法器的延迟, 而图2中, Wallace树延迟为5个3 -2加法器的延迟。图1的延迟比图2的延迟大。

图1 串行累加 图2 Wallace 树

2 32 位浮点乘法器的设计

本文是针对IEEE754 单精度浮点数据格式进行的浮点乘法器设计。IEEE754 单精度浮点格为32位, 如图3 所示。设A ,B均为单精度IEEE754格式, 他们的符号位, 有效数的偏移码和尾数部分分别用S , E 和M来表示。双精度和单精度采用的运算规则是一致的, 只是双精度的位长增加了一倍, 双精度是64位, 其中尾数52位, 指数11位, 1位符号位。所以提高了精度范围。

图3 32 位浮点数据格式

32 位浮点数据格式: A = (- 1) S ×M ×2E-127。其中乘法器运算操作分4步进行。

(1) 确定结果的符号, 对A 和B 的符号位做异或操作。

(2) 计算阶码, 两数相乘, 结果的阶码是两数的阶码相加, 由于A 和B 都是偏移码, 因此需要从中减去偏移码值127,得到A 和B 的实际阶码, 然后相加, 得到的是结果的阶码, 再把他加上127, 变成偏移码。

(3) 尾数相乘,A 和B 的实际尾数分别为24位数, 即1×Ma 和1×Mb, 最高位1是隐藏位, 浮点数据格式只显示后23位, 所以尾数相乘结果应为一个48位的数据。

(4) 尾数规格化, 需要把尾数相乘的48位结果数据变成24 位的数据, 分3步进行:

① 如果乘积的整数位为01, 则尾数已经是规格化了;如果乘积的整数位为10, 11, 则需要把尾数右移1位, 同时把结果阶码加1。

② 对尾数进行舍入操作, 使尾数为24位, 包括整数的隐藏位。

③ 把结果数据处理为32位符合IEEE浮点数标准的结果。包括1位符号位, 8位结果阶码位, 结果23尾数位。

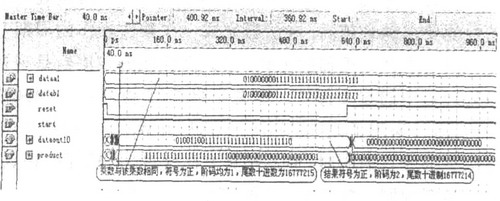

3 32 位浮点乘法器的实现与仿真

图4 列出本设计的FPGA 仿真结果。图中data1是被乘数, data2是乘数, reset是清零信号, 高有效。start 是开始信号, 也是高有效。dataout10是两个浮点32 位数相乘, 进行规格化以后的结果, 是一个32 位数。Product 是24位尾数相乘的结果, 是一个48位数。

图4 32 位浮点乘法器的仿真结果

整个设计采用了VHDL和Verilog HDL语言进行结构描述, 如果采用的是上华0.5 的标准单元库, 并用Synopsys DC 进行逻辑综合, 其结果是完成一次32位浮点乘法的时间为30ns, 如果采用全定制进行后端版图布局布线, 乘法器性能将更加优越。

4 结 语

本文给出了32 位浮点乘法器的设计, 浮点算法具有高精度性以及较宽的运算范围, 使得乘法的设计更能够满足工程和科学计算的要求, 电路的设计、模拟和实现均采用Altera Quartus II 4.1开发工具。采用的器件EPF10K100EQ 240-1, 逻辑单元是1914个, PIN的数量是147,本设计采用了一系列的算法和结构, 如采用Booth编码的方法和Wallace树的结构, 使得系统具有高速度特点, 并且易于ASIC的后端版图实现。

转载于:https://www.cnblogs.com/erizen/archive/2009/05/05/1450302.html

32位单精度浮点乘法器的FPGA实现相关推荐

- Verilog实现---IEEE标准的单精度浮点乘法器

目录 1.实现目标 2.原理说明 3.设计说明 4.Verilog代码 后言 1.实现目标 2.原理说明 首先要懂得浮点乘法器的工作原理与如何编码运算的过程,这里给出两个参考Blog. 浮点加法.减法 ...

- 32位单精度浮点数表示法

32位单精度浮点数表示法

- 【Verilog】32位单精度浮点数比较大小

参考链接 32位单精度浮点数的IEEE表示法 问题描述 在使用Verilog编写模块时,有时会需要进行多个浮点数中取最大/最小值的操作,而Vivado中提供的floating-point IP核并 ...

- 32位单精度浮点数存储格式

32位单精度浮点数的存储格式: 其中s为符号位,占据1bit, f是由低23个bit组成的分数,最高位为0.5,然后是0.25,以此类推.e为2的指数幂,b为偏置(在32位单精度里b=127). 所以 ...

- IEEE-754单精度浮点类型详解(完结篇)

IEEE-754工业标准 前言 众所周知,计算机内部系统实际只能存储二进制数据,我们在计算机中所使用到的文档.图片.影音等数据,实际都是以二进制的数据形式存放在计算机的内存或者硬盘中,不管内存(内存条 ...

- IEEE-754单精度浮点类型存储(每个步骤都有画图,清晰明了,通俗易懂)

IEEE-754标准单精度浮点类型存储概述 folat(32位单精度浮点类型) java中浮点类型也就是小数类型,浮点类型一共有两种,float和double:float为32位(4字节)单精度浮点类 ...

- C/C++中浮点数格式学习——以IEEE75432位单精度为例

这是浮点数的通常表示形式,在IEEE754中,单精度浮点数有如下形式: 32位单精度 单精度二进制小数,使用32个比特存储. 1 8 23位长 S Exp Fraction 31 30至23 偏正值( ...

- 基于TI TMS320F2837x系列的单/双核32位浮点MCU控制器+ Xilinx Spartan-6低功耗FPGA核心板

由创龙自主研发的SOM-TL2837xF核心板,大小仅有72mm*44mm.采用沉金无铅工艺的8层板设计,专业的PCB Layout保证信号完整性的同时,经过严格的质量控制,非常适用于高速数据采集与处 ...

- IEEE754:将单精度浮点数的IEEE754格式转换成32位整型

ieee754,要求如下, 定义函数 int my_int_float() 从键盘输入一个单精度浮点数的字符串,然后自己解析该字符串,并用位操作把对应的值按754格式保存到4字节里,最后返回该四字节对 ...

最新文章

- golang 反射_云原生的 Java与Golang

- MySQL分区表概念以及优缺点

- java中ATM与数据库Mysql的连接

- Start DWM manually on Windows 7 and vista

- 【JAVA 第四章 流程控制语句】课后习题 直线斜率 以及判断坐标是否在直线上点到直线的距离

- 高级应用-路由协议配置

- 电子商务世界历程及国内历程

- pytorch例子学习——NEURAL TRANSFER USING PYTORCH神经迁移

- 笔记本中的insert,idea中Alt + insert快捷键在笔记本中怎么输入

- jxcell开发简单实例

- 结合Delphi和Python的优势:使用Delphi VCL组件快速构建超现代的Python本机Windows GUI桌面酷炫用户界面应用

- 20130723 上海OOW第二日

- IP地址冲突怎么办? 如何解决局域网IP地址冲突?

- OpenJudge NOI 2.1 7621:硬币面值组合

- 我的XBox手柄怎么有线断连了

- jianx vtritualbox 虚拟镜像的体积

- 使用Github Actions自动部署vue项目到nginx服务器

- 《安卓最佳免费应用》摘要版 2012年8月版

- 安装PhotoShop报错 无法写入注册表值请检查权限(错误代码160)

- 三菱伺服图纸,三菱驱动器图纸

热门文章

- 未来计算机领域最急缺的人,未来十年最紧缺职业 没人愿意干的高薪职业

- c语言程序设计电加热炉,基于80C52单片机的电加热数字恒温控制系统设计

- fscanf不读取_思考了一天,终于把matlab的fscanf中的sizeA搞清楚了

- c语言小明今年16岁,C语言1.爷爷对小明说:我现在的年龄是你的7倍,过几年是你的6倍,再过若干年就分别是你的5倍,4倍,3倍,2倍.你知道爷爷和小明现在的年龄吗?...

- mysql 导入 sqlite_Mysql 数据导入SQlite

- java wix_使用WIX升级MSI

- Spring3 整合 Hibernate4实现数据库操作(1)

- (八)linux驱动之ioctl的使用

- 如何设置mysql表中文乱码_php mysql表中文乱码问题如何解决

- empinfo Oracle数据库,Oracle数据库---包