晶振、时钟信号、锁相环、分频器

驱动数字电路运转是的时钟信号,时序电路都需要一个外部时钟信号来驱动,完成计时,同步,计数,时序控制等各种功能。象CPU也是用时序信号驱动来完成各种运算的,而且象ARM带的模块绝大部分与时序都有关,因此理解时钟信号对于底层编程非常重要。

一.时钟信号的源头---------晶振

----------------------------------------------------------------------------

数字电路的时钟信号的来源是哪里呢?主流的设计方案是使用晶振这种外部器件来产生稳定的电流波形。这是性效比最高一个方案,晶振是一块水晶加一些电路的小器材,但是它只需要输入很小的电流就是持续稳定出时钟波形。

这是因为水晶有一个奇特的特性,如果给他通电,他就会产生机械振荡,反之,如果给他机械力,他又会产生电,这种特性叫机电效,。这称为压电效应。

更奇妙的是如在极板间所加的是交变电压,就会产生机械变形振动,同时机械变形振动又会产生交变电场。一般来说,这种机械振动的振幅是比较小的,其振动频率则是很稳定的。但当外加交变电压的频率与晶片的固有频率(决定于晶片的尺寸)相等时,机械振动的幅度将急剧增加,这种现象称为压电谐振,因此石英晶体又称为石英晶体谐振器。 其特点是频率稳定度很高。石英表就是使用这个原理制而成.

晶片会产一个稳定的波形,只要持续的供电,这种电能->机械能->电能转换会让波形不断生成. 在要求得到高稳定频率的电路中,必须使用石英晶体振荡电路。石英晶体具有高品质因数,振荡电路采用了恒温、 稳压等方式以后,振荡频率稳定度可以达到 10^(-9)至 10^(-11)。广泛应用在通讯、时钟、手表、计算机……需要高稳定信号的场合 .

数字电路中重要器件晶振就是使用这一原理制作而成. 晶振是石英晶体谐振器和石英体时钟振荡器的统称。不过由于在消费类电子产品中,谐振器用的更多,所以一般的概念把晶振就等同于谐振器理解了。后者就是通常所指钟振。

它是一种机电器件,是用电损耗很小的石英晶体经精密切割磨削并镀上电极焊上引线做成。

晶振在数字电路的作用就是供一个基准时间.数字电路都是按时序的进行工作的, 在某个时刻专门完成特定的任务,因此几乎每个电路都有会接收外部时钟信号的管脚.如果这个时钟信号发生混乱.整个电路就工作不正常了. 在一个整体设备里,如开发板,或 PC 主板.所有电路通常共享一个晶振. 便于各部分保持同步。有些通讯系统的基频和射频使用不同的晶振,而通过电子调整频率的方法保持同步。

二.系统主频--------内部时钟频率

--------------------------------------------------------------

一般晶振称为外部时钟频率,它需要把信号引入数字电路给CPU和其它模块使用,局限于材料的物理特性一般的晶振的频率并不是太高,如S3C2440/S3C6410上的晶振的频率一般是12MHz/20MHz,而对的应的CPU的需要使用时钟信号高达400MHz/600MHz,或者更高.这个时候,需要把较低外部时钟信号增加频率到CPU可以接受的频率。这称为倍频. S3C6410 的主频 最高可到667Mhz.

锁相环电路

倍频的功能是由一种特殊电路---锁相环电路来完成的。 锁相环电路(Phase-Locked Loop,缩写 PLL) , PLL基本上是一个闭环的反馈控制系统,它可以使 PLL 的输出可以与一个参考信号保持固定的相位关系。PLL 在电路的作用之一是起到倍频的作用.即可以输出系统时钟的固定倍数频率.

因为在ARM CPU启动后,最开始必须做的事情是配置倍频的比率。这样当输入外部时钟频率一定的情况下,按照倍频的比例,就可以得到CPU的频率,用不同频率运行,这在嵌入式CPU的,一个系统出于不同目的可能会以不同频率运行,低频运算速度慢但是省电,高频速度快但能耗大。

但是CPU本身是有一个设计最高频率的,如果强行配置成高于设计频率的速度运行,就是人们称的超频。有可能带加速CPU老化,运行时散热增加的问题。

一般为了保险,软件开发都都会配成产商给几种标准频率。

三.设备频率

----------------------------------------

在SOC的CPU上,除了CPU内核以外,在一个物理芯片上,还有一些其它模块,以S3C6410为例,它带了I2C,UART,USB HOST等多个模块,这一些模块通过AHB总线与CPU内核相连.这一些模块同样需要时钟信号来驱动。

但是ARM的主频信号相对这一些模块来说,频率显得过高。这个时候象S3C2440中内核会提供两种较低频率的时钟信号。 HCLK和PCLK两种时钟信号给设备使用。

divider 分频器

但是对一些低频模块,PCLK的频率仍然显得过高,这时需要模块自己使用分频器(divider)来把频率进一步降低。降到多少值一般取决于软件的需求,因此各个模块的分频参数一般都是可以调整的。因此初始化相关模块时,软件做一件重要事件就是设置分频参数。

Prescaler 预分频因子

在有一些模块,如果需要编程来设定分频的比率,通常是用Prescaler即预分频因子这个参数来设定分频后的值,假设输入频率是Fin,分频后输出的频率是Fout,而三者有如下关系

Fout = Fin /(Prescaler + 1 )

在某一些模块里,分频后的频率仍然是太高,可能需要再次分频,这时分频的参数一般称为divider value.这样公式变成

Fout = Fin /(Prescaler + 1 )/divider

链接:https://www.zhihu.com/question/20392042/answer/14999333

来源:知乎

著作权归作者所有,转载请联系作者获得授权。

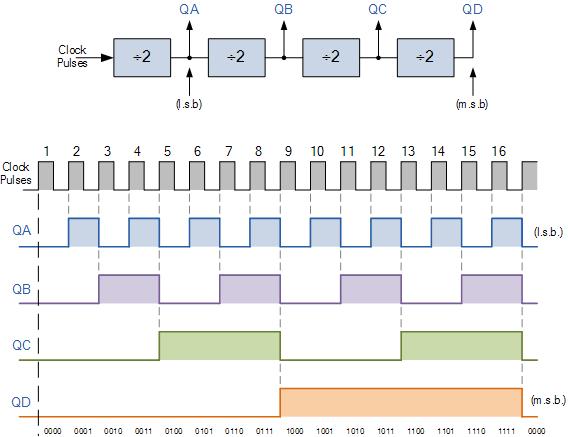

<img src="https://pic3.zhimg.com/303c5efb4815d2adde60c45452112946_b.jpg" data-rawwidth="568" data-rawheight="437" class="origin_image zh-lightbox-thumb" width="568" data-original="https://pic3.zhimg.com/303c5efb4815d2adde60c45452112946_r.jpg">(  ( http://www.electronics-tutorials.ws/counter/count_1.html )

( http://www.electronics-tutorials.ws/counter/count_1.html )

以上图为例,分频器分出来的信号有四个频率。题目中所说 CPU周期信号、节拍周期信号、节拍脉冲信号本质上都是时钟脉冲的不同分频,主要区别在于用途上。

通常来说,CPU 周期信号最“慢”,它决定 CPU 所处的状态。CPU 执行一条指令的周期叫做指令周期(instruction cycle),指令周期可以划分为 fetch、decode、和 execute 三个部分,所以也叫 fetch-decode-execute cycle。假设上图与 QD 频率相同的信号有三个,QD1、QD2、QD3,它们分别依次处于高电位,那么就可以用它们来控制 CPU 处于 fetch、decode、还是 execute 状态,这就是 CPU 周期信号。

节拍周期信号是控制信号,调整电路的功能。比如,现在 CPU 处于 fetch 状态,仍旧以上图为例,假设 QC 这个比 QD “快”的信号有 QC1、QC2、QC3……QCi 个,分别对应电路的不同功能(比如,应该将从内存中取来的数字作为指令解释,还是送给寄存器存起来),谁处于高电位,CPU 就能执行谁决定的功能。

节拍脉冲信号则是触发信号,决定电路的实际工作起点。以上图的 QB 为例,假设 QD1 决定 CPU 处于 fetch 阶段,QC1 决定 CPU 的功能是去内存取一个数字,那么 QB 的上升沿会触发整个电路切实地执行这个功能。

from: http://www.cnblogs.com/xd-elegant/p/4125853.html

晶振、时钟信号、锁相环、分频器相关推荐

- 锁相环PLL --原理浅析

1.什么是锁相环 锁相环电路是使一个特殊系统跟踪另外一个系统,更确切的说是一种输出信号在频率和相位上能够与输入参考信号同步的电路,它是模拟及数模混合电路中的一个基本的而且是非常重要的模块. 2.锁相环 ...

- PLL(锁相环)电路原理

(一) PLL(锁相环)电路原理 在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高.无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较.但是,晶体振荡器除了可以使用 ...

- 晶振,数字电路的心脏~

之所以说晶振是数字电路的心脏,就是因为所有的数字电路都需要一个稳定的工作时钟信号,最常见的就是用晶振来解决,可以说只要有数字电路的地方就可以见到晶振. 常见种类 我们常说的晶振,包含两种. 一种需要加 ...

- 电路 晶振频率_都说晶振是电路的心脏,你真的了解它吗?

之所以说晶振是数字电路的心脏,就是因为所有的数字电路都需要一个稳定的工作时钟信号,最常见的就是用晶振来解决,可以说只要有数字电路的地方就可以见到晶振. 常见种类 我们常说的晶振,包含两种. 一种需要加 ...

- 锁相环工作原理,比如我们8MHZ晶振如何让MCU工作在48MHZ或者72MHZ呢

锁相环英文 Phase locked loop,所以很多资料上就简称PLL 现在很多芯片工作频率很多,频率多高取决晶振频率大小,比如我们电脑芯片1.5GHZ比如我们常用的单片机MCU又72MHZ,但是 ...

- 锁相环(PLL),倍频器、分频器原理

废话不多说,直接开干 锁相环原理 由一个基准频率振荡器(晶体振荡器),相位频率比较器,VCO(电压控制振荡器),回路滤波器组成.晶振产生频率为fr的时钟,与VCO产生的fo的时钟同时传入相位频率比较器 ...

- 锁相环(倍频,分频,利用开发板固有频率+内部专用电路 产生特定需求的时钟信号)

一般来说,开发板的时钟是由板上的晶振产生的,频率大部分是固定的,但是我们在应用中有时候需要其他频率的时钟信号.为了解决这个问题,FPGA内部会留有专门的设置电路--时钟管理单元(硬件资源),利用已有的 ...

- 晶振如何产生数字时钟信号

MCU时钟引脚外部会接一个晶振和两个电容就能构成我们的芯片需要的数字时钟电路(方波动画),今天就来和大家分享下,这个电路晶振是如何产生数字时钟的. 首先晶振产生时钟电路其实我们只看到了外面一部分,还有 ...

- PLL锁相环原理以及Altera FPGA的IP核实现

文章目录 前言 一.PLL锁相环功能核原理 1. 锁相环功能 2. 锁相环原理[1] 二.Altera的FPGA调用IP核实现 后续补充 总结 参考文献 前言 本文主要介绍了锁相环的原理,以及适用Al ...

最新文章

- LeetCode 77. Combinations--回溯法,-Python,Java解法

- Linux疑难杂症解决方案100篇(十一)-ubuntu crontab 详细规则及不执行时的解决方法

- POJ-1941 The Sierpinski Fractal

- boost::equal_range相关的测试程序

- python2exe下载_py2exe下载 0.6.9.win32-py2.7-python转exe工具-pc6下载站

- 为什么要在Java SE 7的数字中使用下划线-在数字文字中使用下划线

- Command10,Access数据库

- H3C认证路由交换互联网络专家

- [原创]Scala学习:编写Scala脚本

- 人工智能TensorFlow工作笔记010---TensorFlow 游乐场游戏,了解神经网络主要功能作用_工作流程

- 论文赏析[NAACL19]基于DIORA的无监督隐式句法树归纳

- linux下面桌面的安装

- vue多个html传递参数,vue 项目@change多个参数传值多个事件的操作

- android+语音验证,如何使用Android的Alexa语音服务进行身份验证?

- Python-Leetcode-剑指offer(五月上做题整理)

- linux drupal 7,在CentOS 7下试验Drupal 7

- python flask后台框架_利用python实现后端写网页(flask框架)

- 蚂蚁金融科技全面开放战略背后的技术布局

- 开课吧 python课视频_开课吧人工智能时代的新起跑线python爬虫小课vip

- 联想昭阳E43闪屏|屏幕有亮线|问题交流QQ群群号