基于FPGA的直接数字频率合成器的的设计和实现设计和实现

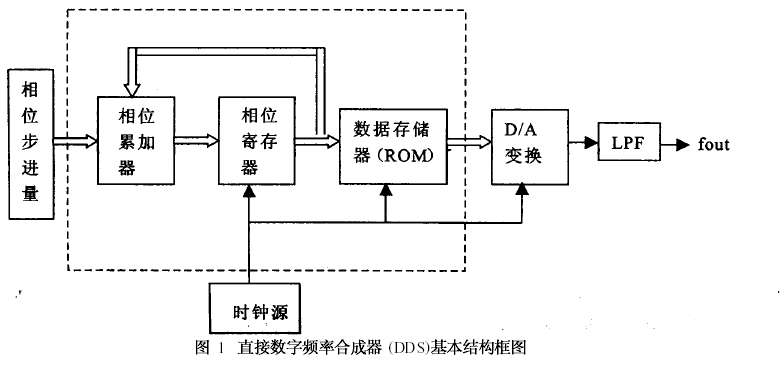

相位累加器由N位全加器和N位寄存器级联累加而成。每来一个时钟脉冲,相位累加器以频率控制字A为步长进行累加运算,产生所需的频率控制数据; 相位寄存器在时钟的控制下把累加的结果作为数据存储器(ROM)的地址(通常取其高十位的数据作为ROM的地址),对数据存储器(ROM)进行寻址,同时把累加运算的结果反馈给相位累加器,以便进行下一次累加运算。这样累加器在参考时钟的作用下,进行线形相位累加,当相位累加器累积满量时就会产生一次溢出,完成一个周期性的动作,这个周期便是DDS合成信号的一个周期,累加器的溢出频率便是DDS输出的信号频率。

由此可以知道对于位数为N的相位累加器,若频率控制字为A,则DDS系统输出的信号频率为:

可见,理论上通过设定相位累加器位数N,频率控制A和基准时钟的值,就可产生任一频率的输出。而频率的分辨率为:

由于基准频率一般固定,因此DDS的分辨率就取决于相位累加器的位数,相位累加器的为数越高,其分辨率也就越高。

数据存储器(ROM) 又称作查找表,实质是一波形存储器,其中存储离散后的波形幅值以及每个值对应的地址值。用相位累加器输出的数据作为取样地址,对波形存储器进行相位幅值转换,相位寄存器每寻址一次ROM, ROM就输出一个相对应的信号相位/幅度值,即可在给定的时间上确定输出的波形幅值。由于信号相位/幅度值用二进制码表示,如果需要输出模拟波形(例如正弦波) ,需送入D /A转换器进行数/模转换,最后经低通滤波器进行平滑处理,就可以得到平滑的信号波形了。

三 DDS的实现

1) 相位累加器和寄存器

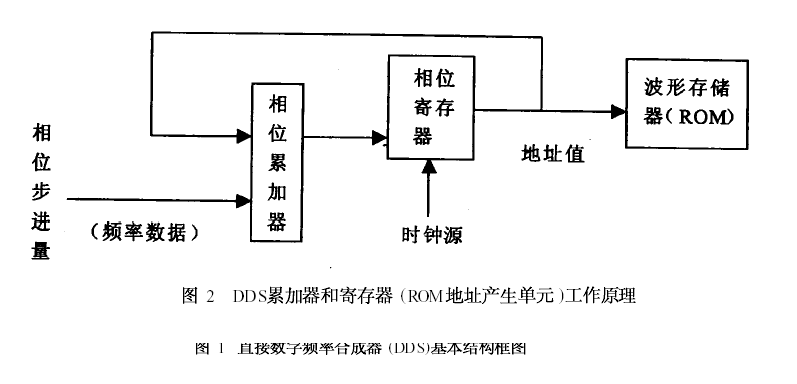

在DDS的设计中,累加器是一个很关键的部分,它决定着频率的范围和分辨率。本设计中采用的是N=24位的二进制累加器和寄存器,其工作原理如图2所示:

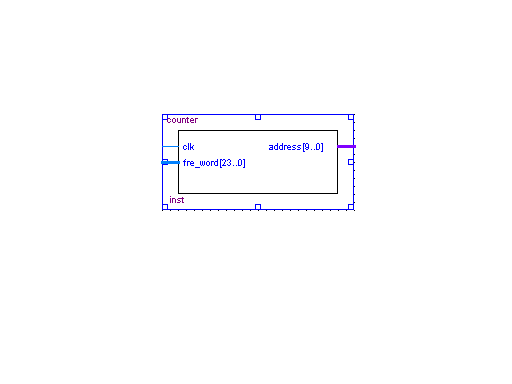

在QuartusⅡ中实现DDS累加器和寄存器的设计如图3所示:其中累加器与寄存器在同一个模块中,累加器每加一次输入到寄存器中就进行一次锁存,再将锁存后的结果反馈给累加器作为其下一次累加的初始值。同时取锁存后的数据的

图3

高十位作为查表的地址值。在图3中 clk为系统时钟, fre_word 为输入24位的频率控制字,address为输出取锁存后取十位(其对应的离散波形为一个周期取1024点)的地址值。

1) 波形表的生成

在本设计中,DDS能输出三种波形,分别为方波,三角波和正弦波。为了

确不失真地输出原波形,将一个波形周期离散成1024对相位/幅值(也对应与前面的地址值),存储于表中。由于方波和三角波的实现算法相对简单,因此只是正弦波的算法用表来实现。

a.正弦波

正弦波的生成是先通过C语言实现正弦函数的算法并生成一个后缀为.mif 的文件sin.mif。其语言函数如下:

#include<stdio.h>

#include"math.h"

void main()

{

int s;

int i;

FILE *fp;

fp=fopen("1024.mif","w+");

fprintf(fp," -- MAX+plus II - generated Memory Initialization File/n");

fprintf(fp," -- By 00022809/n/n/n/n/n");

fprintf(fp,"WIDTH=8;/n/n");

fprintf(fp,"DEPTH=1024;/n/n");

fprintf(fp,"ADDRESS_RADIX=HEX;/n/n");

fprintf(fp,"DATA_RADIX=HEX;/n/n");

fprintf(fp,"CONTENT BEGIN/n");

for(i=0;i<1024;i++)

{s=127+sin(atan(1.0)*8*i/1024)*127;

fprintf(fp,"%x/t:/t%x;/n",i,s);

}

fprintf(fp,"END;/n");

fclose(fp);

}

然后在QuartusⅡ生成一个基于 sin.mif 文件的后缀为 sin.v的文件,此文件即可作为一个模块来调用。其模块引脚图如图4所示:

图4

其中address为输入的地址值,clock为系统时钟,clken为使能信号,为高电平有效,q为输出的波形幅值。

b.方波的生成

方波算法比较容易实现。由于其只有高低电平两种状态,因此只需要在一个周期的时间中间位置翻转电平即可。其实现过程如下

由于相位累加器的值是线形累加的,因此地址address的值也是线形累加的,对所给地址值address进行判断,当地址值的最高位为0时,便将波形幅值各字位赋值1,否则赋值0。

c.三角波的生成

三角波的生成原理与方波生成原理相似,也是对地址address的值进行判断,当其最高位为0时,取其1~8位为三角波的波形幅值,即令q[7:0] =address[8:1]

当其最高位为1时,对其1~8位的值取反后再作为三角波的波形幅值,即令

q[7:0] = ~ address[8 : 1]。

2) 操作模块的实现

操作模块主要包括按键模块和状态转换模块

a.按键

在本设计中采用的是单脉冲式的按键模式,每按一次键,就产生一个标准时钟的脉冲。按键为低电平有效,检测到有键按下,便输出一个单脉冲。

b.状态转换

该模块是整个设计中的一个核心模块,其功能接受外部操作,并结合当前状态执行相应的处理,其实质是一个状态机。

在设计中一共用到了四个按键,各按键对应的功能如下表1:

|

键号 |

功能 |

|

1 |

复位键:在任何状态按下此键则输出频率为1Hz的正弦波 |

|

2 |

波形模式选择键:按键选择波形,每按一次键波形则改变一次,波形在正弦,方波,三角波三种模式下切换 |

|

3 |

频率挡位选择键:按键选择频率挡位,每按一次键选择到不同的频率挡位,频率一共分为四挡,分别为1Hz ~ 1KHz, 1KHz ~ 10KHz,10KHz ~ 200KHz,大于200KHz |

|

4 |

频率步进选择键:按键选择频率步进值,每按一次键,其步进值根据此时所处的频率挡位的不同而不同:当频率处于1Hz ~ 1KHz 时,步进值为1Hz,当频率处于1KHz ~ 10KHz 时,步进值为100Hz,当频率处于10KHz ~ 200KHz 时,步进值为1KHz,当频率大于200KHz 时,步进值为10KHz, |

表1 按键功能表

其程序的实现实质是一个Mealy状态机的实现,应用case语句对键值进行判断并进行各种状态的转换和对应操作。其模块引脚图如图5所示:

图5

其中 clk为系统时钟,keyin为输入键值,wavemode为输出波形模式值,length为输出频率控制字给累加器进行累加。

3) 频率显示模块的实现

频率显示模块所执行的功能是将当前输出波形的频率在LCD上显示出来。根据输出波形频率计算公式: 可知,只要知道了频率控制字A,标准时钟频率fclk,累加器的长度N,就可计算出输出频率 .

其实现过程依次用到的模块有:乘法模块,除法模块,二进制数转化为BCD码,LED显示模块。

小结:

本文简述了DDS的工作原理,介绍了DDS的FPGA实现。经实验证明,根据此思路设计的DDS具有频率范围宽,约为1Hz ~ 800K Hz,调节方便,波形高度保真的特点。但由于时间有限,其功能方便还有许多不足之处,有待进一步得到扩展。

基于FPGA的直接数字频率合成器的的设计和实现设计和实现相关推荐

- 基于FPGA的遥控数字时钟设计

基于FPGA的遥控数字时钟设计报告 Author:张宏宇 摘要 数字时钟是一种通过数字显示时间的计时装置,本次项目采用Cyclone Ⅳ系列芯片,使用QuartusII开发环境,使用Ver ...

- 基于 FPGA Vivado 的数字钟设计(附源工程)

今天给大侠带来基于 FPGA Vivado 的数字钟设计,开发板实现使用的是Digilent basys 3,如有想要入手 basys 3 开发板的,可以联系牛总:18511371833.话不多说,上 ...

- 基于FPGA的简易数字时钟

基于FPGA的可显示数字时钟,设计思路为自底向上,包括三个子模块:时钟模块,进制转换模块,led显示模块.所用到的FPGA晶振频率为50Mhz,首先利用它得到1hz的时钟然后然后得到时钟模块,把时钟模 ...

- 基于FPGA的八位数字抢答器

一.课程设计的内容 通过学习掌握使用可编程逻辑器件和QuartusII 软件的基本使用,利用QuartusII 软件各种器件进行多路智力竞赛抢答器设计:利用DE2板对所设计的电路进行验证:总结电路设计 ...

- 基于FPGA的时间数字转换(TDC)设计(五:基于Carry4的高精度TDC设计)

1.基于Carry4进位链设计原理 常见的基于FPGA开发的TDC有直接计数法,多相位时钟采样法,抽头延迟线法等,之前内容为基于多相位的TDC,本章节中,主要讲解基于抽头延迟线法.在Xilinx FP ...

- 基于FPGA的USB2.0数据传输(通过本文可以自己设计USB2.0模块)

文章部分内容参考了相关论坛中的内容: 对文章中内容感兴趣或者有不懂的可以咨询QQ:2859340499 B站对应讲解本文视频链接 首先来说一下USB这个大家都知道的东西吧: USB通用串行总线,是应用 ...

- 基于FPGA的HDB3数字编码器设计

1.问题描述: 数字基带信号的传输是数字通信系统的重要组成部分之一.在数字通信中,一般由信源发出的数字基带信号含有丰富的低频分量,甚至直流分量,这些信号往往不宜直接用于传输,易产生码间干扰进而直接影响 ...

- 基于FPGA的外部数字键盘输入

文章目录 前言 一.前期准备工作 二.软件思路 1.设计流程 2.代码解读 3.仿真波形 总结 前言 最近闲来没事儿,想练习一下FPGA,于是衍生出了做一个外部按键输入的想法.做起来不难,但是对于新手 ...

- 基于 FPGA 的高级数字电路设计(7)单口 RAM、同步 FIFO、异步 FIFO 设计

一.单口 RAM 设计 module BRAM_PORTA( input clka, input ena, input wea, input [3:0] addra, input [15:0] din ...

最新文章

- (C++)设计一个程序能计算一个日期加上若干天后是什么日期and计算日期差值

- 《愤怒的小鸟》对移动互联网经营的启示

- 现代信用卡管理(二)

- 算法训练营03-数组链表

- 天津科技大学计算机合资办学,天津科技大学计算机科学与信息工程学院介绍

- python startswitch_使用python esl 实现FreeSWITCH自动外呼

- sql2008问题大全

- c语言解析sql语句_解析SQL语句比解析类C语言更麻烦?

- 怎样让jquery mobile 的footer/header 固定?

- java serviceimple,java apiimpl怎么调用 service接口

- ubuntu18.4.02配置静态IP和DNS并ping外网

- html之设置页面ico图标ie浏览器,如何修改网页小图标,浏览器页面上的图标(favicon.ico)...

- 显示器与计算机主机无线连接,如何让手机、电脑和显示器无线连接

- 实现字符串倒序并输出

- 子弹散射——Unity随手记(2021.2.4)

- 腾讯设计师是这么理解和运用的设计规范的

- Photoshop使用路径排版美化文字创作图案

- 【微信小程序】小程序应用和页面生命周期

- Node.js实现网络新闻爬虫及搜索功能(四)

- Google浏览器在新标签页打开网址设置