【FPGA】【转载】跨越鸿沟:同步世界的异步信号

在许多应用中,跨时钟域传送的不只是简单的信号,数据总线、地址总线和控制总线都会同时跨域传输。工程师们用一些其它的手段来处理这些情况,如握手协议和 FIFO 等。

当几个电路不能预知相互的响应时间时,握手方法能让数字电路间实现有效的通信。例如,仲裁总线结构可以让一个以上的电路请求使用单个的总线,用仲裁方法来决定哪个电路可以获得总线的访问权,例如 PCI 或 AMBA(高级微控制器总线架构)。每个电路都发出一个请求信号,由仲裁逻辑决定谁是“赢家”。获胜的电路会收到一个应答,表示它可以访问总线。该电路于是中断请求,开始使用总线。

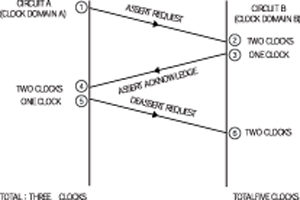

不同时钟域电路使用的握手协议有两种基本类型:全握手(Full-handshake)和部分握手(partial-handshake)。每种类型的握手都要用同步器,每种都各有自己的优缺点。对全握手信号,双方电路在声明或中止各自的握手信号前都要等待对方的响应(图 4)。首先,电路 A 声明它的请求信号,然后,电路 B 检测到该请求信号有效后,声明它的响应信号。当电路 A 检测到响应信号有效后,中止自己的请求信号。最后,当电路 B 检测到请求无效后,它中止自己的响应信号。除非电路 A 检测到无效的响应信号,否则它不会再声明新的请求信号。

图4,对全握手信号,双方电路在声明或中止各自的握手信号前都要等待对方的响应。

这种类型的握手使用了电平同步器。设计人员将这种技术用在如下情况:响应电路(电路 B)需要告知请求电路(电路 A)它可以处理请求。这种握手方法要求请求电路延迟它的下一个请求,直到它检测到响应信号无效。可以用经验估算法判断这个协议的时序:信号跨越一个时钟域要花两个时钟周期的时间,信号在跨越多个时钟域前被电路寄存。全部的时间序列是:A 时钟域中最多五个周期加上 B 时钟域最多六个周期。全握手类型很强健,因为通过检测请求与响应信号,每个电路都清楚地知道对方的状态。这种方式的不足之处是完成所有交互的整个过程要花费很多时钟周期。

另一种类型是部分握手,它可以缩短这些事件的过程。使用部分握手信号时,通信双方的电路都不等对方的响应就中止各自的信号,并继续执行握手命令序列。部分握手类型比全握手类型在健壮性方面稍弱,因为握手信号并不指示各自电路的状态,每一电路都必须保存状态信息(在全握手信号里这个信息被送出去)。但是,由于无需等待其它电路的响应,完整的事件序列花费时间较少。

当使用部

分握手信号方式时,响应的电路必须以正确的时序产生它的信号。如果响应电路要

求先处理完一个请求,然后才能处理下一个请求,则响应信号的时序就很重要。电路用它的响应信号来指示它的处理任务何时完成。一种部分握手方法混合了电平与脉冲信号,而其它的方法则只使用脉冲信号。

在第一种部分握手方法中,电路A以有效电平声明其请求信号,电路B则以一个单时钟宽度脉冲作为响应。此时,电路B并不关心电路A何时中止它的请求信号。但为了使这种方法成立,电路A中止请求信号至少要有一个时钟周期长,否则,电路B就不能区别前一个请求和新的请求。在这种握手方式下,电路B为请求信号使用一个电平A为响应信号使用一个脉冲同步器。只有当电路B检测到请求信号时才发出响应脉冲。这种情况可以使电路A通过控制其请求信号的时序,控制同步器接收到的脉冲间隔(图5)。同样可以用经验估算法确定时序,即信号跨越一个时钟域要花两个时钟周期并且在跨越时钟域前被电路寄存。

图5,在一个部分握手方法中,电路A发出它的请求信号,电路B则以一个单时钟宽度脉冲作为响应。

全部的序列为A时钟域最多三个周期加上B时钟域最多五个周期。这种部分握手方法比全握手方法在A,B两个时钟域分别少用了两个和一个时钟周期。如果采用第二种部分握手方法可以再减少一些时钟周期,此时电路A用一个单时钟宽度脉冲发出它的请求,而电路B也用一个单时钟宽度脉冲响应这个请求。这种情况下,两个电路都需要保存状态,以指示请求正待处理。

图6中,这种握手类型使用的是脉冲同步器,但如果其中一个电路时钟比另一个电路时钟快两倍,则可以用边沿检测同步器来代替。

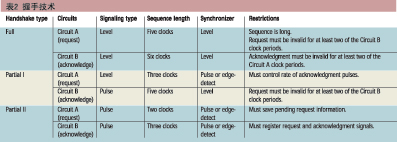

这种握手类型使用的是脉冲同步器,但如果其中一个电路时钟比另一个电路时钟快两倍,则可以用边沿检测同步器来代替(图6)。完整的时序是:A时钟域最多两个周期加上B时钟域最多三个周期。所以这种部分握手技术与全握手方法相比,在A时钟域少用三个时钟周期,在B时钟域也少用三个时钟周期。同时,也比第一种部分握手方法分别在A,B时钟域快了一个和两个周期(表2)。这些握手协议针对的都是跨越时区域的单一信号。但当几组信号要跨越时钟域时,设计人员就需要使用更加复杂的信号传送方法。

表2

数据路径设计

在进行信号同步时有一个重要的规则,那就是不应当在设计中的多个地方对同一信号进行同步,即单个信号扇出至多个同步器。因为同步要花一到两个时钟周期,设计者不能确切地预测到每个信号何时跨越一个时钟域。此外,在新时钟域中一组经同步后的信号其时序是不定的,因为同步延迟可以是一到两个时钟周期,这与输入信号到达同步器的时间有关。这种情况会在各个同步信号间形成一种“竞争状况”。这种竞争状况在需要跨越时钟域传输的多组信号间也会发生,例如数据总线,地址总线和控制总线等。因此,不能对组中的每个信号单独使用同步器,也不能对数据或地址总线的每一位单独使用同步器,因为在新的时钟域中,要求每个信号同时有效。

一种解决总线同步问题的方法是使用一个保持寄存器和握手信号。这种电路包括一个保持信号总线的寄存器,以及一个握手机制(图7)。握手信号指示新时钟域的电路何时可以对总线采样,以及源电路何时可以更换当前寄存器中保存的内容。

图7,一种数据路径同步器设计使用一个保持寄存器和握手信令。

在这种设计中,传输电路将数据(信号总线)存储在保持寄存器,同时发出请求信号。这两个动作可以同时发生,因为请求信号至少要花一个时钟周期才能让接收电路检测到它(最小的握手 - 同步延迟)当接收电路采样到数据(信号总线)时,它发出一个响应信号这种设计使用了全握手方法,所以要花较长时间才能完成整个传输对接收电路而言。 ,使用全握手信号的设计有较大的时间窗口用于对信号总线采样,因而效率较低。如用部分握手方法代替全握手方法则可以加快传输速度。

用这种总线同步方式,你可以同步握手信号,但不能同步信号总线。信号总线来自于保持寄存器,它在接收电路采样前一直保持稳定。注意,如果传输电路向接收电路提交数据太快以致来不及处理,则应用中的总线同步可能不起作用。

高级数据路径设计

在许多情况下,数据在跨越时钟域时需要“堆积”起来,因此使用单个保持寄存器无法完成工作。例如一种情况是某个传输电路猝发式发送数据,接收电路来不及采样。另一种情况是接收电路采样速度超出传输电路发送数据的速度,但采样的数据宽度不够。这些情况就要使用 FIFO 了。

基本上,设计者使用 FIFO 有两个目的:速度匹配或数据宽度匹配。在速度匹配时,FIFO较快的端口处理猝发的数据传输,而较慢的端口则维持恒定的数据流。但是,虽然访问方式和速度不同,但进出FIFO的平均数据速率必须是相同的,否则FIFO就会出现上溢(overflow)或下溢(underflow)问题。与单寄存器设计相同,FIFO将数据保存在寄存器或存储器中,同时同步状态信号,判断何时可以把数据写入FIFO或从FIFO中读出。

在速度匹配应用中,每个端口(读或写)的时钟不同.FIFO中的寄存器使用写端口时钟,就像保持寄存器使用电路时钟来改变寄存器内容一样。信号同步发生在指针逻辑中,而且比握手信号要复杂得多。

转自:https : //wenku.baidu.com/view/3b84da0f844769eae009ed5e.html

【FPGA】【转载】跨越鸿沟:同步世界的异步信号相关推荐

- 【FPGA——基础篇】同步FIFO与异步FIFO——Verilog实现

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其 ...

- FPGA之道(15)组合逻辑与时序逻辑、同步逻辑与异步逻辑的概念

组合逻辑电路与时序逻辑电路 数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑:另一类叫做时序逻辑电路,简称时序电路或时序逻辑. 如果数字电路满足任意时刻的输 ...

- (47)FPGA同步复位与异步复位(异步复位同步释放)

(47)FPGA同步复位与异步复位(异步复位同步释放) 1 文章目录 1)文章目录 2)FPGA入门与提升课程介绍 3)FPGA简介 4)FPGA同步复位与异步复位(异步复位同步释放) 5)技术交流 ...

- (46)FPGA同步复位与异步复位(异步复位)

(46)FPGA同步复位与异步复位(异步复位) 1 文章目录 1)文章目录 2)FPGA入门与提升课程介绍 3)FPGA简介 4)FPGA同步复位与异步复位(异步复位) 5)技术交流 6)参考资料 2 ...

- (45)FPGA同步复位与异步复位(同步复位)

(45)FPGA同步复位与异步复位(同步复位) 1 文章目录 1)文章目录 2)FPGA入门与提升课程介绍 3)FPGA简介 4)FPGA同步复位与异步复位(同步复位) 5)技术交流 6)参考资料 2 ...

- (87)FPGA面试题-同步FIFO与异步FIFO区别?异步FIFO代码设计

1.1 FPGA面试题-同步FIFO与异步FIFO区别?异步FIFO代码设计 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA面试题-同步FIFO与异步FIFO区 ...

- (61)FPGA面试题-使用Verilog语言编写异步复位同步释放代码

1.1 FPGA面试题-使用Verilog语言编写异步复位同步释放代码 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA面试题-使用Verilog语言编写异步复位 ...

- (86)FPGA同步复位与异步复位-面试必问(十)(第18天)

(86)FPGA同步复位与异步复位-面试必问(十)(第18天) 1 文章目录 1)文章目录 2)FPGA初级课程介绍 3)FPGA初级课程架构 4)FPGA同步复位与异步复位-面试必问(十)(第18天 ...

- (11)FPGA面试题同步复位与异步复位

1.1 FPGA面试题同步复位与异步复位 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA面试题同步复位与异步复位: 5)结束语. 1.1.2 本节引言 &quo ...

- (5)FPGA面试题同步电路和异步电路

1.1 FPGA面试题同步电路和异步电路 1.1.1 本节目录 1)本节目录: 2)本节引言: 3)FPGA简介: 4)FPGA面试题同步电路和异步电路: 5)结束语. 1.1.2 本节引言 &quo ...

最新文章

- 优点和阵列的缺点,并且一个链表

- Numpy中stack(),hstack(),vstack()函数详解

- 把一个项目放到GItHub上

- Jpgraph php怎么变异,php使用Jpgraph绘制3D饼状图的方法

- ng-content和@ContentChild的配合用法

- 简化从Win32到Windows 10的迁移之路

- 在用dw.GetSqlSelect()获得到的Sql语句出现PBSELECT( VERSION的解决办法

- html5 查看图片,html5实现图片预览和查看原图

- 13.ThreadPoolExecutor线程池之submit方法

- 北京这些5平米不到的外卖窗口,居然能够排起100米以上的长龙!

- 怎样将Datatable中的数据直接导入到Excel模板上

- 浅谈矩阵分解在推荐系统中的应用

- 四边形不等式优化dp

- 学计算机的银行从业人员,银行从业人员继续教育

- 连上WiFi后,笔记本离路由器比较近时,电脑播音偶尔卡音

- 关于plsqldeveloper打开报错解决方法MSVCR71.dll is missing from your compute

- java求两数最小公倍数_java求解2个数的最小公倍数

- Python 程序员需要知道的 30 个技巧

- 攻与防--论游戏好玩的本质

- 火焰图Flame Graph