Virtex中的ILA属性、VIO属性

ILA属性

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】,双击ILA。弹出ILA触发和配置界面,如图9-7所示。

(1) 【Component Name】:输入组件名称。

(2) Trigger Port Settings选项组:触发端口设置。

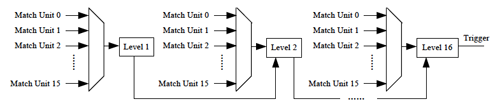

【Number Of Trigger Ports】:设臵触发端口的个数。每个ILA核最多可以支持16个触发端口。设臵好触发端口的数量后,每个触发端口对应一组选项,包含触发宽度、触发条件等,对应标号为TRIGn,其中n代表触发端口号0到15。【Max Sequence Levels】:为触发条件设臵最大序列级数。如图9-8 所示,前一级的输出在条件满足的情况下,可以作为下一级的条件,以此类推,可以最大传递16 个状态。  图9-7 ILA 配置界面

图9-7 ILA 配置界面  图9-8 触发序列器框图 【Use RPMs】:选择是否用相关布局宏(RPM)生成ILA 核,以提高性能。如果选择该选项,则会阻止布局布线器对ILA 核内部进行布局优化,保持其较好的时序特性。通常推荐使用该选项。【Enable Trigger Output Port】:使能ILA 触发输出端口。在HDL 代码设计中,将该触发端口输出至FPGA 引脚,可以用于触发外部测试设备。该触发输出端口也可以和设计的其他逻辑相连,作为触发、中断或者控制信号。其波形(电平或者脉冲)和极性(高有效或者低有效)可以在运行中通过分析工具随时控制。ILA 触发输出相对于触发输入延时10 个时钟周期。

图9-8 触发序列器框图 【Use RPMs】:选择是否用相关布局宏(RPM)生成ILA 核,以提高性能。如果选择该选项,则会阻止布局布线器对ILA 核内部进行布局优化,保持其较好的时序特性。通常推荐使用该选项。【Enable Trigger Output Port】:使能ILA 触发输出端口。在HDL 代码设计中,将该触发端口输出至FPGA 引脚,可以用于触发外部测试设备。该触发输出端口也可以和设计的其他逻辑相连,作为触发、中断或者控制信号。其波形(电平或者脉冲)和极性(高有效或者低有效)可以在运行中通过分析工具随时控制。ILA 触发输出相对于触发输入延时10 个时钟周期。

(3) Storage Settings 选项组:存储选项设置。

【Sample On】:选择上升沿还是下降沿触发。【Sample Data Depth】:设臵ILA核最大数据采样深度,它与器件BRAM容量有关。【Enable Storage Qualification】:存储限制条件,它不同于触发条件,但它可以与触发条件配合使用,是Trigger的一种补充。当被测逻辑满足触发条件后,可以通过该选项来控制采样到的数据是否可以被记录到存储器中,默认为使能。所以,触发条件和存储限制条件可以组合在一起,来决定捕获进程什么时候开始,捕获什么样的数据。【As Trigger】:选择数据和触发条件是否相同。如果选中此功能,数据和触发条件相同,这是大多数逻辑分析中常用的一种模式,因为用户可以捕获和采集任何触发ILA内核的数据。独立的触发端口也可以被排除在数据端口之外,这样的话,数据输入端口将不会出现在ILA核的端口映射中。如果禁止此功能,数据端口将完全独立于触发端口,这种模式限制了被采样数据总量,节省了BRAM资源。如果禁止了此功能,用户将需要设臵【Data Port Width】参数。【Data Port Width】:ILA采样数据的宽度。如果数据和触发字互相独立,那么允许的最大数据宽度将取决于器件类型和数据深度。Spartan-3、Spartan-3E、Spartan-3A、Spartan-3A DSP和Virtex-4支持的最大数据采样宽度为256 bit,其他器件支持的最大数据宽度为4096bit。

设置好ILA核的触发和存储选项后,单击【Next】。进入ILA触发端口设置界面,如图9-9所示。

图9-9 ILA触发端口设置界面

图9-9 ILA触发端口设置界面

(4) Trigger Port 1选项组:触发端口1选项组。

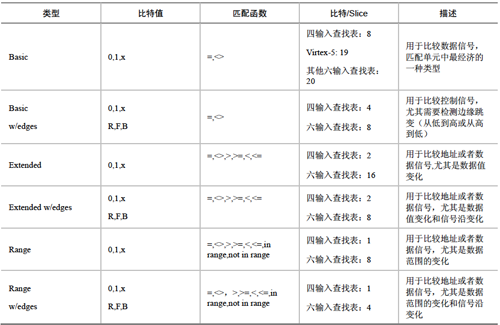

【Trigger Port Width】:触发端口宽度,最大为256位。【Match Units】:设臵触发端口的匹配条件的个数,用于检测触发端口是否满足设定的条件。一个触发器最多可以有16个触发匹配单元。匹配类型在【Match Type】下拉列表框中选择。【Counter Width】:匹配单元计数器宽度,用于设臵满足匹配条件的次数。最大32位宽。【Match Type】:匹配类型选择,ILA核支持六种匹配类型(Basic、Basic w/edges、Extended、Extended w/edges、Range以及Range w/edges),如表9-1所示。【Exclude Trigger Port from Data Storage】:是否从所采样和保存的数据中删除触发端口。当选择【Data Same As Trigger】复选框时,该选项有效。

配置完毕后,会在界面右侧的【Core Utilization】栏自动给出核所占用的资源。

表9-1 触发条件判断单元类型列表

表9-1 触发条件判断单元类型列表

说明:

(1) “0”表示“逻辑0”,“1”表示“逻辑1”,“X”表示“未知”,“R”表示“从0到1的跳转”,“F”表示“从1到0的跳转”,“B”表示“任何电平跳转”。

(2) 比特/Slice数值只是说明不同匹配单元的大致资源利用率,不能用精确的硬件资源消耗评估。

VIO属性

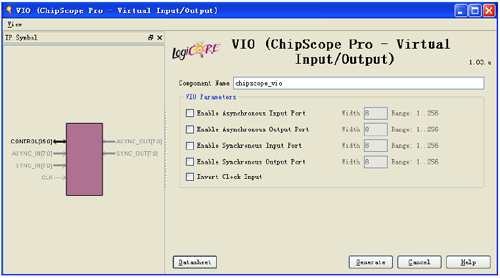

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】,双击VIO。弹出VIO配置界面,如图9-10所示。

图9-10 VIO参数设置界面

图9-10 VIO参数设置界面

(1) 【Component Name】:输入组件名称。

(2) VIO Parameters选项组:VIO参数选项组。

【Enable Asynchronous Input Port】:使能异步输入信号,最多可以设臵256个异步输入信号,VIO的异步输入用来监测设计中待测试模块的输出信号,它与时钟无关。【Enable Asynchronous Output Port】:使能异步输出信号,最多可以设臵256个异步输出信号,VIO的异步输出用来为待测试逻辑模块提供输入激励,它与时钟无关。【Enable Synchronous Input Port】:使能同步输入信号,最多可以设臵256个同步输入信号,VIO的同步输入信号用于监测设计中待测试模块的输出信号,要求待测试信号与VIO核的CLK同步。【Enable Synchronous Output Port】:使能同步输出信号,最多可以设臵256个同步输出信号,VIO的同步输出信号为待测试模块的输入提供激励,要求待测试信号与VIO核的CLK同步。【Invert Clock Input】:VIO核可以选择时钟信号翻转,即选择采用时钟的上升沿或者下降沿作为触发条件。

注意:只有使用同步输入和/或输出的时候,时钟信号翻转才有效。

9.2.4 ATC2属性

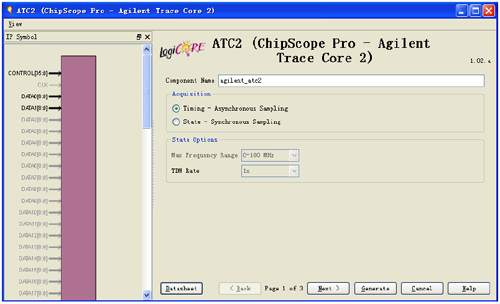

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by function】→【Debug & Verification】→【ChipScope Pro】。双击ATC2,弹出ATC2配置界面,如图9-11所示。

图9-11 ATC2参数设置界面

图9-11 ATC2参数设置界面

(1) 【Component Name】:输入组件名称。

(2) Acquisition选项组:

【Timing – Asynchronous Sampling】:用于异步数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由组合逻辑组成。【State - Synchronous Sampling】:用于和CLK输入信号同步的数据捕获。数据信号经ATC核输出到FPGA引脚上的通道由流水线触发器和CLK输入信号组成。

(3) State Options:状态选项组。

【Max Frequency Range】:ATC2核的最大频率范围。有效的最大频率选择项为0~100 MHz, 101~200 MHz, 201~300 MHz和301~500 MHz。当目标数据捕获方式设臵成【State - Synchronous Sampling】,此选择对ATC2核有效。【TDM Rate】:ATC2核不用片上存储器来存储捕获的数据,Agilent逻辑分析仪通过一个专用探头连接器和FPGA引脚连接传送捕获的数据。ATC2内核数据传送到FPGA引脚上的速率可以与ATC2输入端口DATA的速率相同(TDM速率=1x)或者是DATA速率的2倍(TDM速率=2x)。只有当目标数据捕获方式设臵成【State - Synchronous Sampling】时,TDM速率才可以设臵成2倍数据速率。

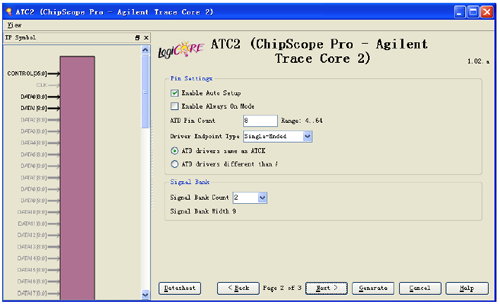

设置好后,单击【Next】,弹出引脚设置界面,如图9-12所示。

图9-12 ATC2核ATCK和ATD引脚参数

图9-12 ATC2核ATCK和ATD引脚参数

(4) Pin Settings选项组:引脚设置选项组。

【Enable Auto Setup】:使能Agilent逻辑分析仪自动设臵ATC2核引脚和逻辑分析仪POD的连接。这个属性使得Agilent逻辑分析仪能自动设定每个ATC2引脚的最佳相位和电压采样偏移量。缺省为使能状态。【Enable Always On Mode】:用于强制ATC2核使能ATC2核内部逻辑和输出缓冲器。FPGA配臵完成后,该模式强制选择BANK0。在该模式下,不通过手动设臵ATC2核,器件在配臵完成之后就可以立即捕获事件。只有当目标数据捕获方式设臵成【TIMING】方式时,该选项设臵才有效。【ATD Pin Count】:设臵ATD输出引脚数量,范围是4~128。【Driver Endpoint Type】:用于设臵控制ATCK和ATD输出引脚的输出驱动器类型:单端或者差分。所有的ATCK和ATD引脚必须设臵成相同的驱动器终端类型。【ATD drivers same as ATCK】:可以修改ATCK引脚参数,如I/O标准、SLEW参数和驱动强度等,并强制ATD驱动器参数与ATCK的驱动器参数保持一致。【ATD drivers different than ATCK】:可以单独设臵ATD的每一个引脚的驱动器参数,完全独立于ATCK。

(5) Signal Bank选项组:Signal Bank设置选项组。

【Signal Bank Count】:ATC2核包含了一个实时可选的数据信号组多路选择器。该选项代表了多路复用器输入,即数据输入端口数量或者信号分组的数量。有效的信号分组值为1、2、4、8、16、32和64。【Signal Bank Width】:设臵信号组宽度。ATC2核的每个输入信号组数据端口的宽度取决于捕获模式及TDM速率。在【State - Synchronous Sampling】模式,每个信号组数据端口的宽度等于【ATD Pin Count】ATD引脚数和【TDM Rate】TDM速率的乘积。在【Timing – Asynchronous Sampling】模式下,每个信号组数据端口的宽度等于(【ATD Pin Count】ATD引脚数+1)和【TDM Rate】TDM速率的乘积。

单击【Next】,出现ATC2核ATCK和ATD引脚参数,如图9-13所示。

图9-13 ATC2核ATCK和ATD引脚参数

图9-13 ATC2核ATCK和ATD引脚参数

输出时钟(ATCK)和数据(ATD)引脚在ATC2核内例化,因此用户不用在顶层设计中手动设计,只需在内核产生器中指定这些引脚的位置和属性。这些引脚属性添加在ATC2核的*.NCF文件中。在引脚参数表中,可以设置ATCK和ATD引脚的位置、I/O标准、输出驱动和歪斜率。

(6) Pins选项组。

【Pin Name】:ATC有两类输出引脚:ATCK和ATD。当捕获模式设臵成【State - Synchronous Sampling】模式时,ATCK引脚用作时钟引脚;当捕获模式设臵成【Timing – Asynchronous Sampling】模式时,ATCK和ATD引脚都用作数据引脚。引脚名称是不能改变的。【Pin Loc】:设臵ATCK或ATD引脚的位臵。【IO Standard】:设臵ATCK或每个ATD引脚的I/O标准,标准根据器件和驱动器终端类型而定,它和约束文件中定义的I/O标准一样。【Drive】:设臵引脚输出驱动器的最大输出驱动电流,2~24mA。【Slew Rate】:设臵ATCK和ATD引脚的信号斜率,FAST或SLOW。

Virtex中的ILA属性、VIO属性相关推荐

- css规则中区块block,css常用属性总结:背景background下篇

前言:这段时间天天加班到10:30之后,简直是x了. 在上一篇文章中,分别解析了background各个属性的用法和注意细节.如果我们在项目上使用背景效果,如果使用下面的写法,你可能抓狂. body{ ...

- 可以获取python中输出函数帮助的是_Python帮助函数调试函数 用于获取对象的属性及属性值...

Python帮助函数调试函数 用于获取对象的属性及属性值 刚接触Python,上篇 <Python入门>第一个Python Web程序--简单的Web服务器 中调试非常不方便,不知道对象详 ...

- 网页中的盒模型css属性,详解CSS中的Box Model盒属性的使用

页面上显示的每个元素(包括内联元素)都可以看作一个盒子,即盒模型( box model ).请看 Chrome DevTools 里的截图: 可以显而易见的看出盒模型由 4 部分组成.从内到外分别是: ...

- 在vuejs 中使用axios不能获取属性data的解决方法

在vuejs 中使用axios不能获取属性data的解决方法 参考文章: (1)在vuejs 中使用axios不能获取属性data的解决方法 (2)https://www.cnblogs.com/lo ...

- MyBatis框架学习:<select>节点中的resultType和resultMap属性

1.为什么要进行resultType或resultMap注解配置 当需要实现的数据访问是查询类型的,在<select>节点中必须配置resultType或resultMap中的某1个属性( ...

- 【Visual Studio 扩展工具】使用ComponentOne中的GroupDefinition和SortDefinition属性保存和还原布局...

2019独角兽企业重金招聘Python工程师标准>>> 概述 在此前的ComponentOne中,我们为C1FlexGrid(最快,最灵活的.Net数据网格控件)添加了一个非常强大的 ...

- python中文读音ndarray-numpy中的ndarray方法和属性详解

NumPy数组的维数称为秩(rank),一维数组的秩为1,二维数组的秩为2,以此类推.在NumPy中,每一个线性的数组称为是一个轴(axes),秩其实是描述轴的数量.比如说,二维数组相当于是一个一维数 ...

- 项目文件中的已知 NuGet 属性(使用这些属性,创建 NuGet 包就可以不需要 nuspec 文件啦)...

知道了 csproj 文件中的一些常用 NuGet 属性,创建 NuGet 包时就可以充分发挥新 Sdk 自动生成 NuGet 包的优势,不需要 nuspec 文件啦.(毕竟 nuspec 文件没有 ...

- Intent中的四个重要属性——Action、Data、Category、Extras

Intent中的四个重要属性--Action.Data.Category.Extras 支持原文:点击链接进入原文阅读-->http://www.cnblogs.com/wisekingokok ...

最新文章

- python和c学习-python与c++交互学习入门之5

- ChaosBlade 在工商银行混沌工程体系中的应用实践

- C++之return的作用域

- python+django(解决对象编码显示Test Object问题)

- Python 正则表达式详解(建议收藏!)

- c语言弹出u盘 api,一个简单的C++编写的u盘病毒代码

- 《经济机器是怎样运行的》笔记(二)

- JavaWeb之Servlet-注册页面

- stm32h743单片机嵌入式学习笔记8-avi视频解码

- 解决KEIL MDK编译生成Bin文件时,却生成了*bin文件夹

- luci html 页面,luci更改登录账号.htm

- 计算机组成原理-宝典

- jav中jar包的MANIFEST.MF

- 笔记本电脑f11功能键_电脑的键盘上的F1至F12的功能分别是什么

- html css 距离顶部距离,详解CSS line-height和height

- 技术之路如何成长而不迷茫

- DM数据守护读写分离集群

- php异位或加密,PHP异位或加密实现自动登陆

- Linux source文件后提示 export:command not found

- 计算机c盘加容量,两种方法,给电脑C盘增加10G的容量,电脑焕然一新

热门文章

- 对现有代码的分析方法随想

- python语言函数库_Python 的标准库,从0到1学Python

- confluence 编辑器这次没有加载_代码编辑器横评:为什么 VS Code 能拔得头筹

- 麦克风阵列降噪_黄鹂智声降噪耳机E100u,与喧嚣说再见

- Java程序员面试如何超常发挥?

- mysql外键教程_MySQL外键使用详解

- linux mysql 1045 错误_Linux 下,mysql数据库报无法登陆错误:ERROR 1045 (28000): Access denied for use...

- android 自定义相册选择,Android通过手机拍照或从本地相册选取图片设置头像

- iis服务器文件上传速度慢,windows 2008 R2 上传速度慢

- 在图片中如何生成带有文字边缘空心字体?